多通道應(yīng)用中使用的精密高速數(shù)據(jù)采集系統(tǒng)需要最先進(jìn)的性能。本模擬技巧涵蓋了在選擇ADC驅(qū)動(dòng)器以優(yōu)化信號(hào)鏈性能時(shí)需要考慮的關(guān)鍵規(guī)格。

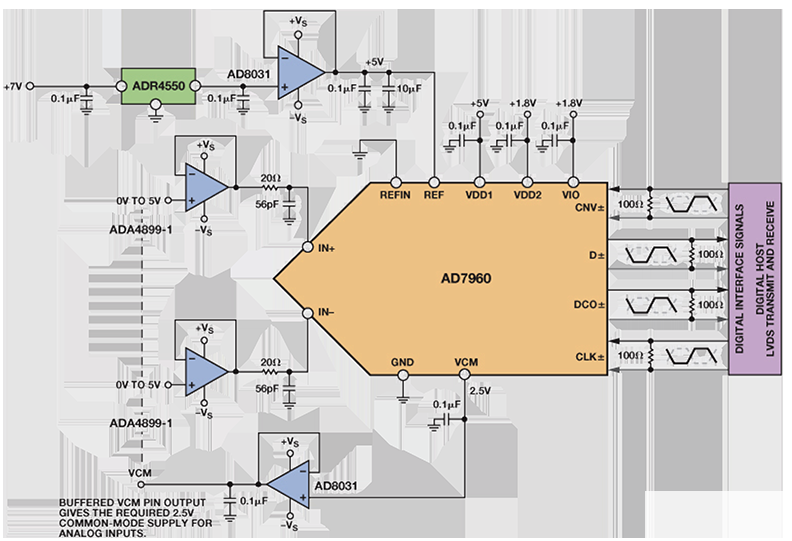

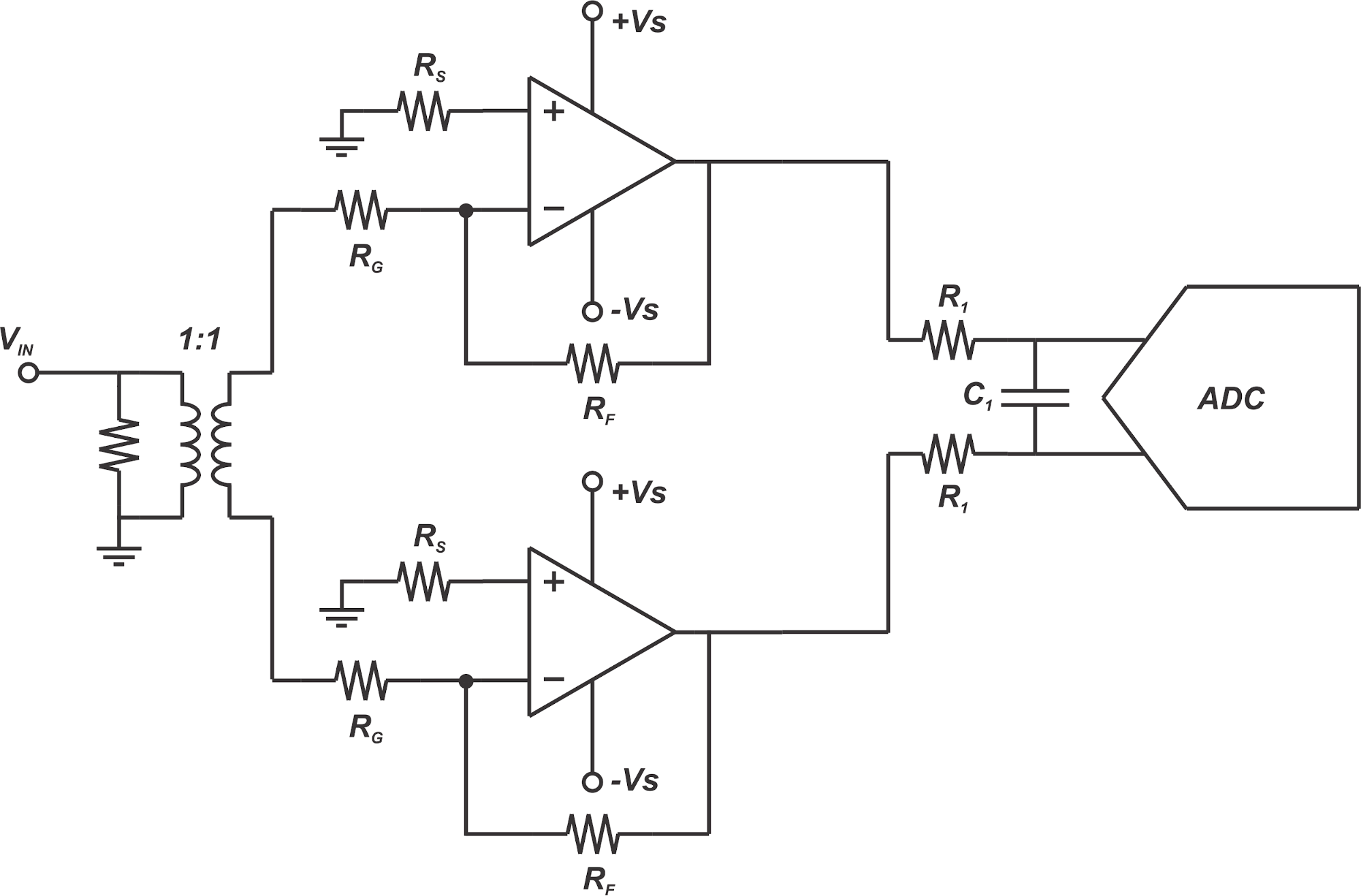

該圖顯示了一個(gè)高精度、低噪聲、18位數(shù)據(jù)采集信號(hào)鏈,具有±0.8 LSB積分非線性(INL)、±0.5 LSB差分非線性(DNL)和99 dB信噪比(SNR)。AD7960 18位、5 MSPS PulSAR差分ADC采用容性數(shù)模轉(zhuǎn)換器(CAPDAC),可提供前所未有的噪聲和線性度,無(wú)延遲或流水線延遲。它提供多路復(fù)用應(yīng)用所需的寬帶寬、高精度(100 dB DR)和快速采樣(200 ns),同時(shí)顯著降低多通道應(yīng)用的功耗和成本。

采用AD7960、ADA4899、AD8031和ADR4550的精密、快速建立信號(hào)鏈

模數(shù)轉(zhuǎn)換器驅(qū)動(dòng)器

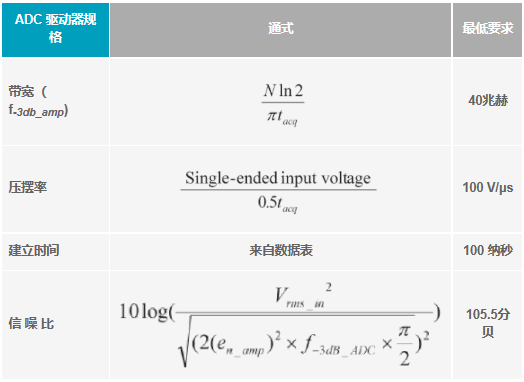

ADC的采集時(shí)間決定了ADC驅(qū)動(dòng)器的建立時(shí)間要求。下表顯示了選擇ADC驅(qū)動(dòng)器時(shí)必須考慮的一些規(guī)格。與往常一樣,應(yīng)在工作臺(tái)上驗(yàn)證信號(hào)鏈性能,以確保可實(shí)現(xiàn)所需的性能。

AD7960 ADC驅(qū)動(dòng)器選擇基準(zhǔn)測(cè)試

注:N= 18,tACQ= 100 ns, Vrms_in2= 52/2 = 12.5 V2, en_amp= 2 nV/√Hz, f–3dB_ADC= 28 MHz。

運(yùn)算放大器數(shù)據(jù)手冊(cè)通常將建立時(shí)間指定為線性建立和回轉(zhuǎn)的組合時(shí)間;給出的公式是一階近似值,假設(shè)線性建立率為50%,回轉(zhuǎn)(多路復(fù)用應(yīng)用)為50%。

ADA4899-1軌到軌放大器具有600 MHz帶寬、–117 dBc失真@ 1 MHz和1 nV/√Hz噪聲。當(dāng)配置為單位增益緩沖器以5 V差分信號(hào)驅(qū)動(dòng)AD7960的輸入時(shí),它在50 ns內(nèi)建立至0.1%。

審核編輯:郭婷

-

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

54文章

8646瀏覽量

149382 -

運(yùn)算放大器

+關(guān)注

關(guān)注

217文章

5685瀏覽量

176142 -

adc

+關(guān)注

關(guān)注

99文章

6660瀏覽量

548567

發(fā)布評(píng)論請(qǐng)先 登錄

求助,為什么要在ADC的輸入前端放置ADC驅(qū)動(dòng)器呢?

可實(shí)現(xiàn)最佳噪聲和THD性能的ADC驅(qū)動(dòng)器TIDA-01053技術(shù)資料下載

全能DAQ ADAQ798x的常見(jiàn)ADC驅(qū)動(dòng)器配置方案

高性能DAQ系統(tǒng)的ADC電壓基準(zhǔn)兩級(jí)緩沖器優(yōu)化設(shè)計(jì)

DAQ ADAQ798x為何要配置ADC驅(qū)動(dòng)器?

寬帶運(yùn)算放大器優(yōu)化高速14位性能差分驅(qū)動(dòng)器PCB布局技術(shù)的概述

如何針對(duì)設(shè)計(jì)選擇合適的差分ADC驅(qū)動(dòng)器

探究減少差分ADC驅(qū)動(dòng)器諧波失真的PCB布局技術(shù)

AN123-2 GHz差分放大器/ADC驅(qū)動(dòng)器的應(yīng)用與優(yōu)化

簡(jiǎn)化ADC輸入和基準(zhǔn)驅(qū)動(dòng),簡(jiǎn)化信號(hào)鏈設(shè)計(jì)

用于降低差分ADC驅(qū)動(dòng)器諧波失真的PCB布局技術(shù)

為何要組合使用低通濾波器和模數(shù)轉(zhuǎn)換器驅(qū)動(dòng)器?

如何優(yōu)化MCU SPI驅(qū)動(dòng)程序以實(shí)現(xiàn)高ADC吞吐速率

最大限度提高∑-? ADC驅(qū)動(dòng)器的性能

選擇ADC驅(qū)動(dòng)器以實(shí)現(xiàn)優(yōu)化的信號(hào)鏈性能

選擇ADC驅(qū)動(dòng)器以實(shí)現(xiàn)優(yōu)化的信號(hào)鏈性能

評(píng)論