JESD204是一款高速串行接口,用于將數據轉換器(ADC和DAC)連接到邏輯器件。該標準的修訂版B支持高達12.5 Gbps的串行數據速率,并確保JESD204鏈路上的可重復確定性延遲。隨著轉換器速度和分辨率的不斷提高,JESD204B接口在ADI公司的高速轉換器和集成RF收發器中變得越來越普遍。此外,FPGA和ASIC中的柔性串行器/解串器(SERDES)設計自然開始取代傳統的LVDS/CMOS接口到轉換器,并用于實現JESD204B物理層。本文介紹如何使用 Xilinx FPGA 快速設置項目以實現 JESD204B 接口,并為 FPGA 設計人員提供一些應用和調試建議。?

JESD204B協議實施概述

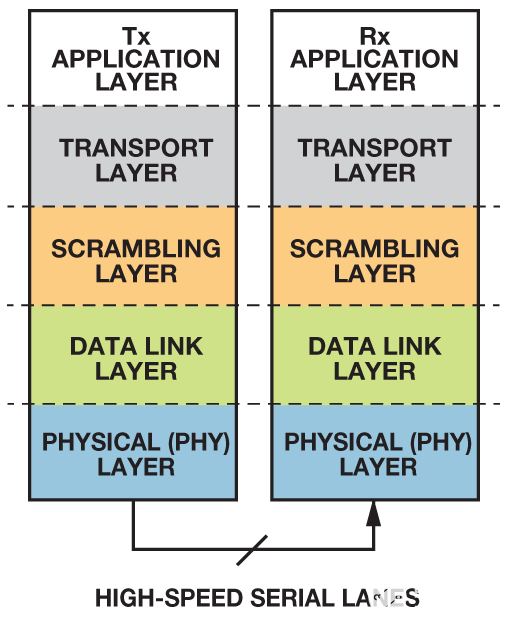

JESD204B規范定義了實現協議數據流的四個關鍵層,如圖1所示。傳輸層映射樣本和成幀、未加擾的八位字節之間的轉換。可選的加擾層對八位組進行加擾/解擾,分散頻譜峰值以降低EMI。數據鏈路層處理鏈路同步、設置和維護,并對可選的加擾八位字節進行編碼/解碼,使其與 10 位字符/從 10 位字符進行加擾。物理層負責以比特率傳輸和接收字符。

圖1.JESD204B標準的關鍵層。

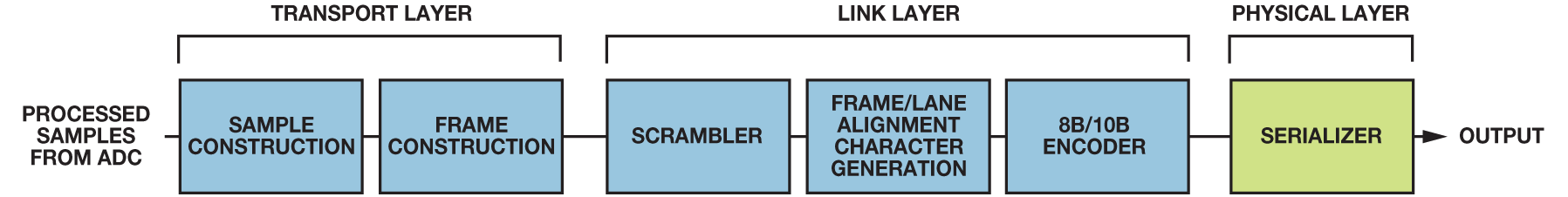

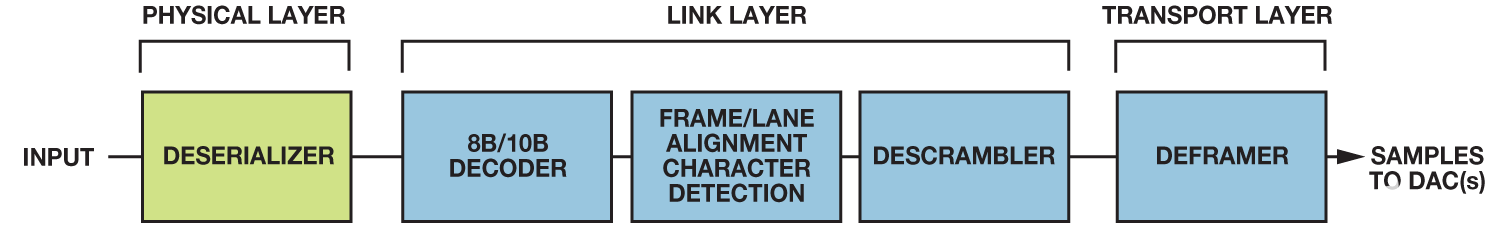

不同的JESD204B IP供應商可能以不同的方式實現這些層。圖2和圖3說明了ADI如何實現JESD204B發送和接收協議。

圖2.JESD204B發射器實現。

圖3.JESD204B接收器實現

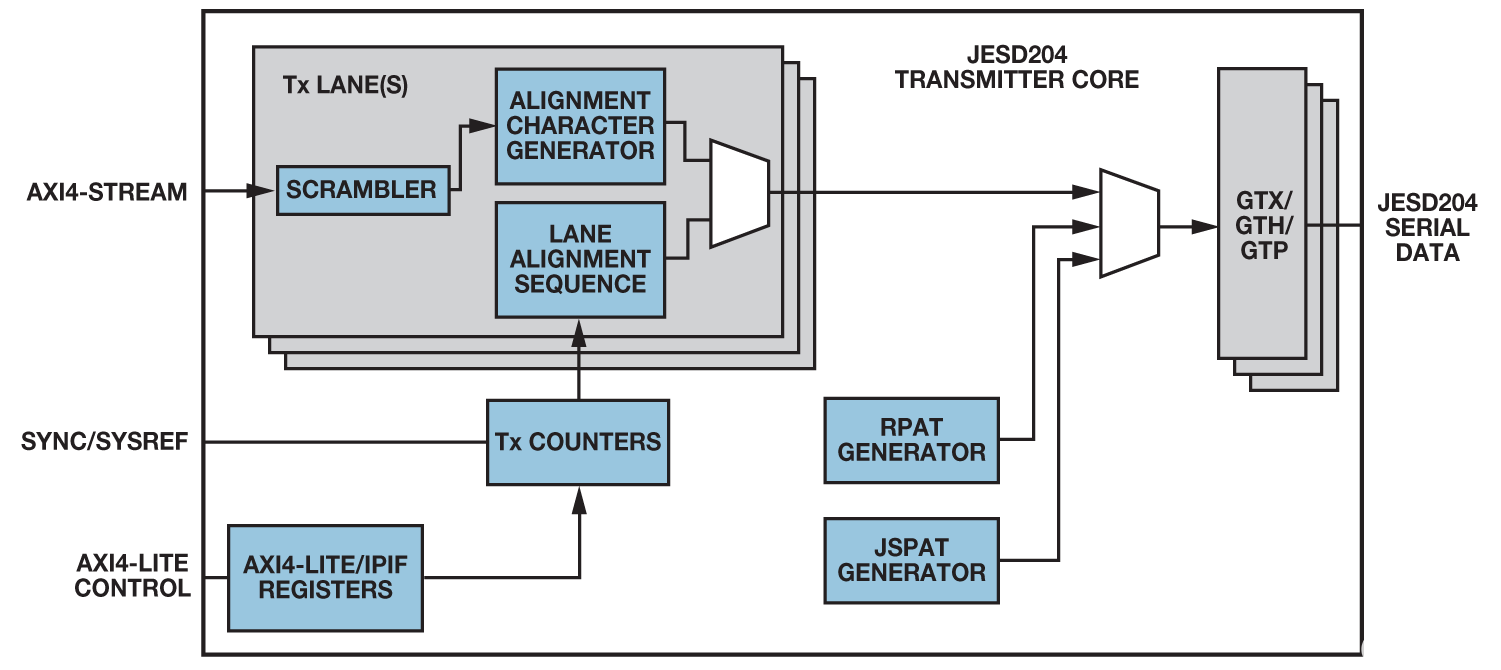

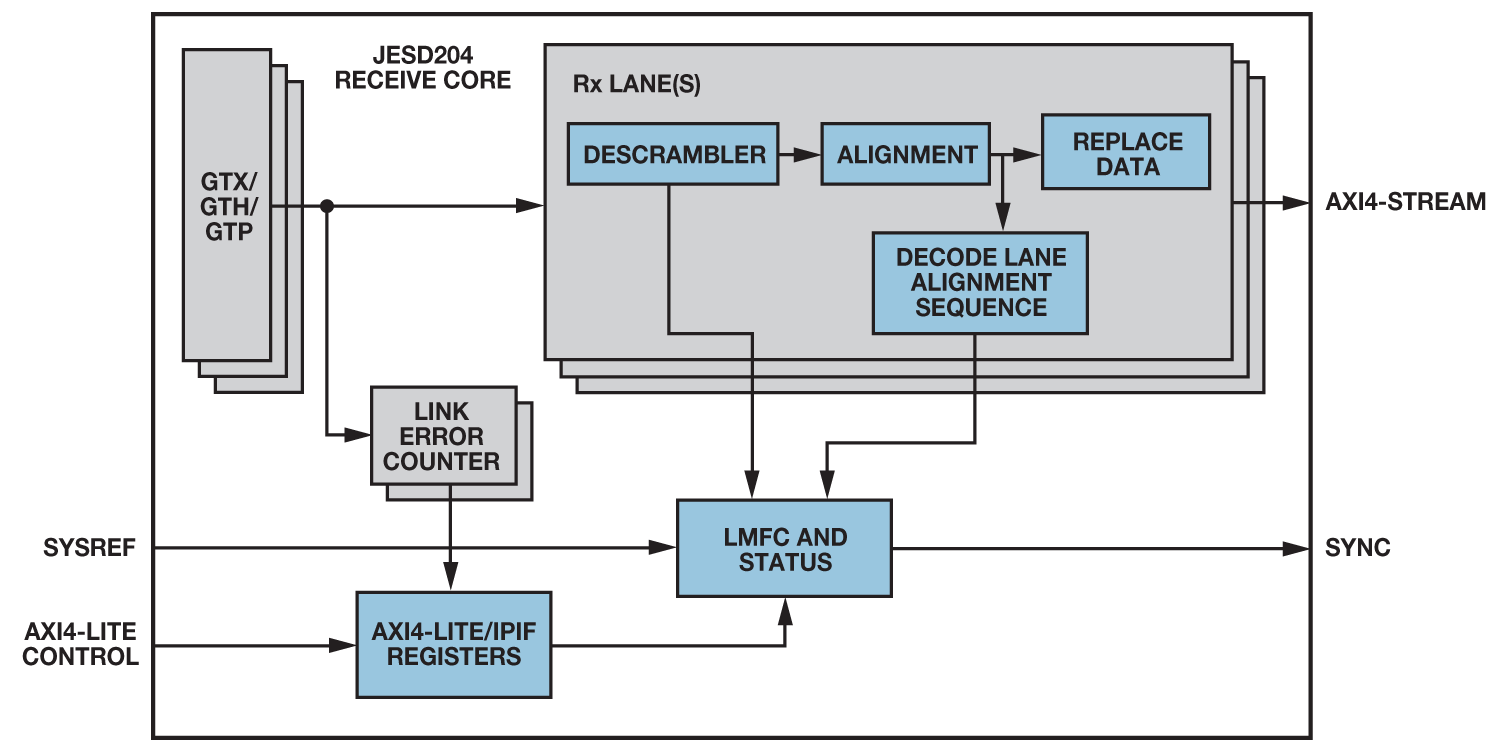

傳輸層的實現在很大程度上取決于特定轉換器的配置以及它在樣本和幀之間的映射方式,因此大多數FPGA供應商將其從其JESD204 IP中排除。此外,高度可配置、緊密集成的SERDES收發器集成在FPGA中。這些可用于支持各種串行協議,包括PCIe,SATA,SRIO,CPRI和JESD204B。因此,實現鏈路層的邏輯內核與實現物理層的可配置SERDES相結合,構成了JESD204B鏈路的基礎。圖 4 和圖 5 顯示了賽靈思 FPGA 上的 JESD204B 發射器和接收器的框圖。發射器/接收器通道實現加擾層和鏈路層;8B/10B 編碼器/解碼器和物理層在 GTP/GTX/GTH 千兆收發器中實現。

圖4.采用賽靈思 FPGA 的 JESD204B 發送器實現。

圖5.采用賽靈思 FPGA 的 JESD204B 接收器實現。

采用賽靈思 FPGA 的 JESD204B 設計示例

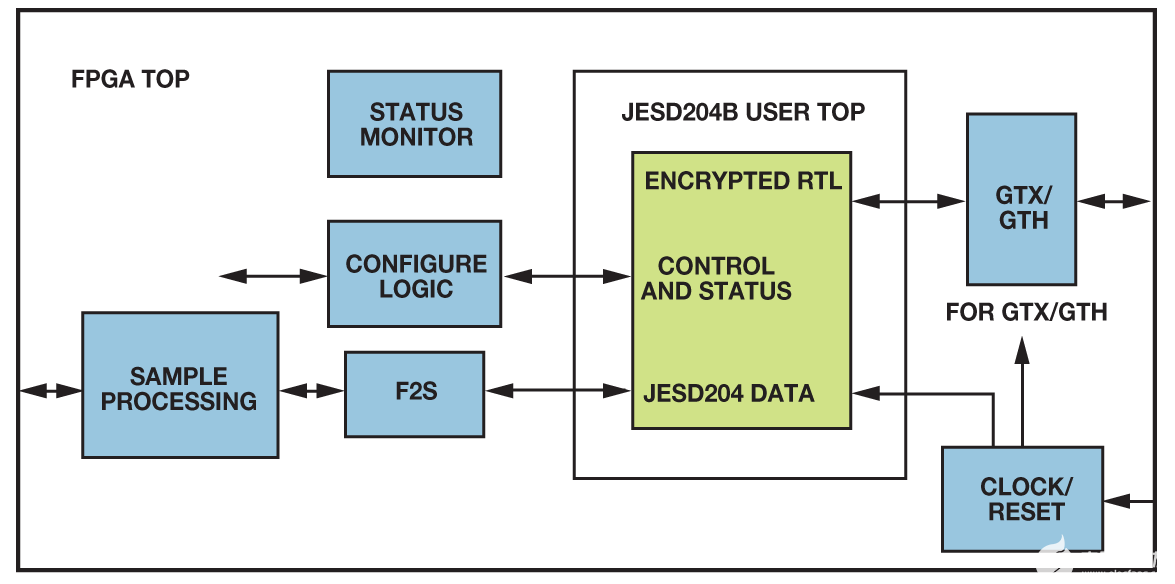

最新的 Xilinx JESD204 IP 核通過Vivado 設計套件?.Xilinx 還提供了使用高級可擴展接口 (AXI) 的 Verilog 示例設計,但此示例項目針對大多數應用進行了過度設計。用戶通常有自己的配置接口,不需要為JESD204B邏輯集成額外的AXI。圖6顯示了一個簡化的JESD204設計,旨在幫助FPGA用戶了解JESD204的結構,并快速啟動他們自己的基于FPGA的JESD204項目。

圖6.JESD204B設計示例

加密寄存器傳輸語言(RTL)模塊(由Vivado生成的JESD204邏輯IP核)等效于圖4和圖5所示的發射器和接收器模塊。加密接口定義可在 Xilinx 示例設計文件中找到。然后將加密的RTL包裝到JESD204B用戶頂部。來自加密 RTL 的控制、配置、狀態和 JESD 數據接口通過包裝器與用戶邏輯和 GTX/GTH 收發器數據連接。GTX/GTH 的符號對齊配置經過優化和更新,使收發器工作更可靠。

專用焊盤應用于SERDES收發器的GTX/GTH參考時鐘。必須特別注意FPGA邏輯的全局時鐘設計,包括內部PLL的時鐘、并行接口、JESD204邏輯內核和用戶特定的處理邏輯。此外,必須準確捕獲JESD204B邏輯內核(子類1)的主系統基準(SYSREF)輸入,以保證JESD204鏈路的確定性延遲。

GTX/GTH收發器和JESD204內核的復位順序對于可靠的JESD鏈路初始化至關重要,因此JESD204內核應處于復位狀態,直到GTX/GTH收發器中的內部PLL被鎖定并且GTX/GTH復位。

需要幀到樣本(F2S)模塊來實現JESD204的傳輸層,該傳輸層根據特定的JESD204B配置將樣本映射到幀或從幀映射幀。然后,由特定于應用程序的邏輯處理示例。輔助模塊監控JESD204邏輯和物理層(PHY)狀態,以便進行系統調試。

賽靈思 SERDES 收發器中的符號對齊

在SERDES接收器中,串行數據必須與符號邊界對齊,然后才能用作并行數據。為了對齊數據,發射器發送一個可識別的序列,通常稱為逗號。接收器在傳入的串行數據流中搜索逗號,并在找到后將其移動到符號邊界。這使接收到的并行字能夠匹配傳輸的并行字。逗號通常是 K,它是 8B/10B 表中用于控制符號的特殊字符。對于JESD204B應用,發送器將發送K = K28.5符號流,用于代碼組同步(CGS)。因此,FPGA可以使用K28.5作為逗號來對齊符號邊界,用戶可以指定逗號匹配是由逗號加號(運行視差為正號)還是逗號減號(運行視差為負)或兩者組成。GTX/GTH逗號檢測的JESD204B默認設置允許使用逗號加號或逗號減號來對齊逗號。

在某些應用程序中,默認逗號設置可能會導致符號重新對齊或對齊到錯誤的符號邊界。這可能會導致混亂的8B/10B解碼錯誤和JESD204B鏈路損壞。逗號加號和減號的組合更可靠,強制逗號對齊塊連續搜索兩個逗號,僅當接收的數據具有逗號加號或減號后跟逗號減號或加號且中間沒有額外位時,才檢測逗號。這有助于在線路速率較高或系統噪聲過多時保持符號邊界和鏈路穩定性。

基于FPGA的JESD204項目的設計考慮

從JESD204接收器到發射器的同步、低電平有效SYNC信號指示同步狀態。正常運行期間鏈路重新初始化會導致樣本數據混亂,因此必須實時監控鏈路狀態。特別是,SYNC上的連續低電平意味著接收器無法識別接收數據流中的至少四個連續K28.5符號。如果發生這種情況,請檢查發射器/接收器 SERDES 配置或確保發射器正在發送 K28.5。SYNC 上的持續高電平表示鏈路已建立并保持穩定性。當 SYNC 從高到低再回到高時,應計算低狀態的持續時間。如果長度超過5幀加9個八位字節,則接收器檢測到大錯誤并發送重新初始化JESD204鏈路的請求。如果持續時間等于兩個幀時鐘,則接收器檢測到一個小錯誤,但不觸發鏈路重新初始化。此功能可以顯著簡化系統調試和進一步的鏈路監控,因此用戶應將其納入其設計中。

8B/10B解碼錯誤可能導致JESD204B鏈路重新初始化,但不是唯一原因,因此用戶設計應能夠計算每個通道的解碼錯誤,以確定鏈路重新同步的原因。此外,SERDES鏈路質量可以通過8B/10B解碼錯誤狀態實時確定。

偽隨機位序列 (PRBS) 為測量高速鏈路中的信號質量和抖動容限提供了有用的資源。大多數 FPGA 中的 SERDES 收發器具有內置的 PRBS 發生器和檢查器,因此不需要額外的 FPGA 資源。因此,不要忘記實例化此函數,在評估誤碼率(BER)或眼圖時應使用該函數。

SERDES收發器中始終使用緩沖器來改變內部時鐘域。發射器和接收器的時鐘設計錯誤或錯誤的時鐘和數據恢復 (CDR) 設置可能導致緩沖區溢出或下溢。在這種情況下可能會發生一些鏈路錯誤,因此監視緩沖區狀態是有意義的。緩沖區溢出和下溢的中斷記錄對于系統調試很有用,因此還應監視用戶邏輯中不允許下溢或溢出的其他內部緩沖區。

結論

本文介紹了如何在賽靈思 FPGA 上快速實現 JESD204 模塊,但該方法也可以應用于其他 FPGA。首先,了解FPGA供應商提供的JESD204邏輯內核和收發器的功能和接口,然后將它們實例化并封裝到邏輯中。其次,全局設計FPGA時鐘樹并重置整個項目的順序。第三,仔細定義JESD204邏輯內核、用戶邏輯和收發器之間的接口。最后,添加必要的調試資源。遵循以下步驟將幫助您快速成功地設計JESD204接口。

審核編輯:郭婷

-

FPGA

+關注

關注

1645文章

22016瀏覽量

616888 -

收發器

+關注

關注

10文章

3664瀏覽量

107731 -

adc

+關注

關注

99文章

6673瀏覽量

548792

發布評論請先 登錄

JESD204B的系統級優勢

在Xilinx FPGA上快速實現JESD204B

JESD204B串行接口時鐘的優勢

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

JESD204B協議有什么特點?

JESD204B協議介紹

JESD204B的優勢

在Xilinx FPGA上快速實現 JESD204B

JESD204B標準及演進歷程

JESD204B是FPGA中的新流行語嗎

在賽靈思FPGA上快速實現JESD204B

在賽靈思FPGA上快速實現JESD204B

評論