事實(shí)證明,將多個(gè) die 或 Chiplet 集成到同一個(gè)封裝里跟將它們集成到同一個(gè) die 上有很大不同,在同一個(gè) die上,所有模塊都是在同一個(gè)節(jié)點(diǎn)上使用相同的工藝開(kāi)發(fā)的。

隨著設(shè)計(jì)變得更加異構(gòu)和細(xì)分化,Chiplet 需要在系統(tǒng)環(huán)境中進(jìn)行建模、適當(dāng)?shù)钠矫嬉?guī)劃、驗(yàn)證和調(diào)試,而非僅作為單獨(dú)的組件。這通常始于高層次抽象的系統(tǒng)的完整規(guī)范。然后再將規(guī)范分成塊并分配給各個(gè)設(shè)計(jì)人員,同時(shí)優(yōu)化他們的設(shè)計(jì)。最后,將所有子系統(tǒng)作為一個(gè)整體重新組合、驗(yàn)證和測(cè)試。

在最簡(jiǎn)單的設(shè)計(jì)中,只有很少的 Chiplet 和相對(duì)簡(jiǎn)單的互連,設(shè)計(jì)過(guò)程類似于具有幾個(gè)大塊的 SoC。“不同的團(tuán)隊(duì)就形狀和面積、引腳位置及其連接等問(wèn)題達(dá)成一致,” Siemens Digital Industries Software的 DRC 應(yīng)用和 Calibre 設(shè)計(jì)解決方案營(yíng)銷總監(jiān) John Ferguson 說(shuō)。“至少對(duì)于數(shù)字設(shè)計(jì)而言,這種方法擴(kuò)展了現(xiàn)有的布局布線技術(shù)。但隨著每個(gè)額外的 Chiplet 或互連的添加,它會(huì)變得更加復(fù)雜。”

最初,向異構(gòu)架構(gòu)的轉(zhuǎn)變是由系統(tǒng)公司推動(dòng)的,這些系統(tǒng)公司希望提高其特定數(shù)據(jù)類型的性能,同時(shí)盡可能節(jié)省能源。現(xiàn)在,隨著芯片制造商尋求將這種級(jí)別的功率和性能優(yōu)化擴(kuò)展到更多市場(chǎng),他們正在尋找方法來(lái)標(biāo)準(zhǔn)化和簡(jiǎn)化這種優(yōu)化,并使其更具成本效益。

Synopsys 營(yíng)銷高級(jí)總監(jiān) Shekhar Kapoor 說(shuō):“正在發(fā)生的根本性宏觀變化是硅的顛覆。“直到最近,生活還是美好的,你可以指望轉(zhuǎn)移到下一個(gè)節(jié)點(diǎn)來(lái)實(shí)現(xiàn)性能和功能優(yōu)勢(shì)。但是現(xiàn)在這些好處正在減少并且成本高得令人望而卻步,因此你真的必須考慮分解,并從成本的角度看待異構(gòu)集成。分解本質(zhì)上是將單個(gè)芯片拆分為多個(gè)芯片,這是推動(dòng)多芯片設(shè)計(jì)的主要變化。這與整個(gè) IP 重用概念相結(jié)合。chiplet 采取了一種曾經(jīng)是主要芯片內(nèi)部的塊的形式。現(xiàn)在,如果你將一個(gè)芯片分成多個(gè)裸片,其中一個(gè)塊或裸片就是一個(gè) Chiplet ,你基本上可以在下一個(gè)設(shè)計(jì)中重復(fù)使用它。

不過(guò),這需要一種不同的芯片設(shè)計(jì)思維方式。“一旦你從業(yè)界正在做的單一單片芯片轉(zhuǎn)向多 Chiplet 設(shè)計(jì),你首先需要將系統(tǒng)級(jí)聚合工具的概念引入流程,”產(chǎn)品負(fù)責(zé)人 John Park 說(shuō)。Cadence 定制 IC 和 PCB 集團(tuán)管理集團(tuán)總監(jiān)。“你不是在設(shè)計(jì)一件事。你正在設(shè)計(jì)多個(gè)事物、多個(gè) Chiplet 及其封裝排列的組合。”

優(yōu)化 Chiplet到 Chiplet 的連接至關(guān)重要。但它也需要在其他芯片和 IP 以及潛在的其他系統(tǒng)的背景下看待。

“你需要在系統(tǒng)級(jí)別——而不是芯片級(jí)別——驗(yàn)證 Chiplet A 通過(guò)封裝正確連接到 Chiplet B,”P(pán)ark 說(shuō)。“這就是我所理解的系統(tǒng)級(jí)設(shè)計(jì)的轉(zhuǎn)變。這是遠(yuǎn)離單芯片的第一步。這是你必須做的第一件事 —— 安裝一個(gè)允許你組裝系統(tǒng)并對(duì)其進(jìn)行優(yōu)化的工具。它將成為你驅(qū)動(dòng)系統(tǒng) LVS(布局與原理圖)的黃金網(wǎng)表,這一點(diǎn)至關(guān)重要。系統(tǒng) LVS 人員經(jīng)常在他們的流程進(jìn)行到一半時(shí)說(shuō),“我要如何驗(yàn)證這個(gè)?” 如果他們沒(méi)有以正確的方式開(kāi)始設(shè)計(jì),他們就會(huì)發(fā)現(xiàn)自己遇到很多麻煩。”

最大的挑戰(zhàn)和限制涉及設(shè)計(jì)的功率、熱、應(yīng)力和 EM-IR 元素。

“只有兩個(gè)維度,這些問(wèn)題更容易解決,”Ferguson。“但是連接 Chiplet 的堆疊或復(fù)雜方式越多,這些挑戰(zhàn)就越困難。我希望我們會(huì)達(dá)到這樣一個(gè)地步,其中每一個(gè)都有限制,有一些合理的保護(hù)帶來(lái)防止出現(xiàn)問(wèn)題。但是,由于連接這些東西的方式有這么多不同的可能組合,因此需要確定更多的約束條件,因此它變得更加復(fù)雜,并且涉及到每個(gè)堆疊/連接的項(xiàng)目。”

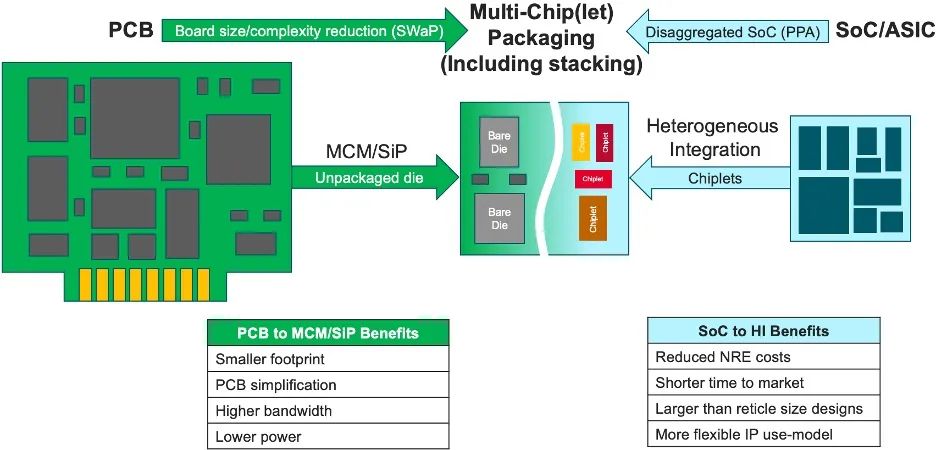

另一個(gè)考慮因素是,多模塊并不總是意味著 Chiplet。“有時(shí)是裸片,有時(shí)是 Chiplet,”P(pán)ark 說(shuō)。“直到大約三年前,它還是multi-chip modules (MCM)。現(xiàn)在我們說(shuō)的是multi-die modules。它是關(guān)于將芯片從他們的封裝組件中取出并將裸芯片安裝在層壓基板上,這就是系統(tǒng)級(jí)封裝 (SiP)/MCM 模塊。這并不會(huì)因?yàn)槲覀冞M(jìn)入 Chiplet的世界而消失。”

圖 1:SiP/MCM與基于chiplet的(異質(zhì)集成)架構(gòu)的對(duì)比。資料來(lái)源:Cadence

智能手機(jī)多年來(lái)一直采用 SiP,尤其是 RF 和模擬組件。“這當(dāng)然是異構(gòu)整合,”P(pán)ark 說(shuō)。“但我們不關(guān)心它們是在什么節(jié)點(diǎn)上構(gòu)建的,它們是基于什么技術(shù)構(gòu)建的。過(guò)去,我們只是不使用異構(gòu)集成這個(gè)詞。”

Chiplet 是這種方法的下一個(gè)增長(zhǎng)階段。“我們希望嘗試圍繞 Chiplet空間創(chuàng)建一些標(biāo)準(zhǔn)化,因?yàn)樗娴暮苄拢铱雌饋?lái)很重要 - 不僅在數(shù)字領(lǐng)域,而且在堆棧內(nèi)存方面也是如此,”應(yīng)用程序開(kāi)發(fā)大師 Matthew Ozalas 觀察到是德科技的工程師和科學(xué)家。“當(dāng)我們展望無(wú)線 6G 系統(tǒng)時(shí),Chiplet 可能是實(shí)現(xiàn)這一目標(biāo)的唯一途徑。通常在進(jìn)化中發(fā)生的事情是它從較低的層次或數(shù)字開(kāi)始,因?yàn)樾酒呀?jīng)可以用功能塊構(gòu)建。最后一個(gè)前沿領(lǐng)域始終是高頻 RF 微波,看起來(lái) Chiplet 也會(huì)如此。”

原因是這種高頻射頻不是標(biāo)準(zhǔn)化的設(shè)計(jì)流程。“如果你看看數(shù)字芯片,這些芯片中有數(shù)十億個(gè)晶體管,沒(méi)有人可以在那里進(jìn)行晶體管級(jí)別的設(shè)計(jì),”O(jiān)zalas 說(shuō)。“所以人們構(gòu)建了這些功能塊,并將它們很好地集成在一起。例如,他們將在他們的數(shù)字芯片中構(gòu)建一個(gè)加法器塊并將這些塊粘在一起。他們已經(jīng)在進(jìn)行這種塊功能/塊級(jí)設(shè)計(jì)。如果你是一名數(shù)字設(shè)計(jì)師,那么你并不是真正在使用晶體管。你真正遇到晶體管的唯一一次是當(dāng)你遇到可靠性問(wèn)題時(shí),或者當(dāng)其中一個(gè)晶體管出現(xiàn)問(wèn)題時(shí)它吸收了太多電流或變得太熱,或者導(dǎo)致你的各種閂鎖問(wèn)題出現(xiàn)問(wèn)題。模擬緊隨其后,并且還有一組功能塊。然后,當(dāng)我們談到射頻和微波時(shí),幾乎全是晶體管。那里的設(shè)計(jì)人員正在研究晶體管。這是非常一觸即發(fā)的。盡管我們希望系統(tǒng)中有一個(gè)低噪聲放大器,但這些組件是高頻的。它們確實(shí)是功能塊,但不是那么標(biāo)準(zhǔn)。如果晶體管拓?fù)浼夹g(shù)發(fā)生變化,這些東西不會(huì)隨之縮小。所以一切都需要改變。” 如果晶體管拓?fù)浼夹g(shù)發(fā)生變化,這些東西不會(huì)隨之縮小。所以一切都需要改變。” 如果晶體管拓?fù)浼夹g(shù)發(fā)生變化,這些東西不會(huì)隨之縮小。所以一切都需要改變。”

他說(shuō),這就是高頻塊最終成為最后邊界的原因。“它無(wú)處不在,Chiplet 也是如此。如果你要構(gòu)建 Chiplet,則可以構(gòu)建具有高頻電路的功能塊。但將它們放在一起,讓它們完美地工作更難。”

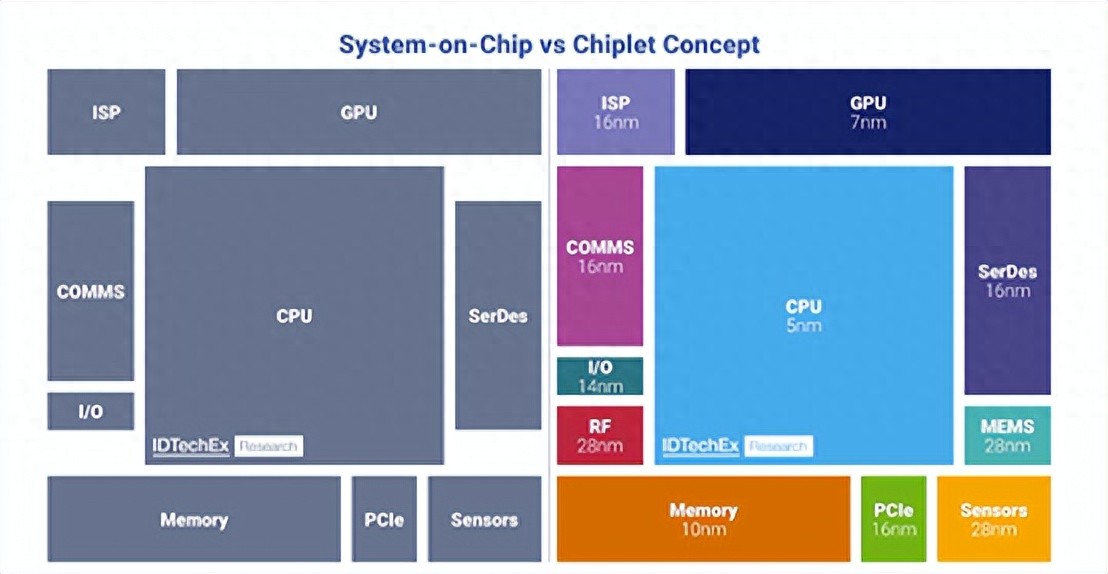

成本也是 Chiplet 越來(lái)越多的考慮因素。“人們正在為摩爾定律的終結(jié)而設(shè)計(jì),”Cadence‘s Park 說(shuō)。“他們正在從單片、巨大的 SoC 和 ASIC 轉(zhuǎn)向分解或模塊化的方法,在這種方法中,這些大芯片上的 IP 已被分解為 Chiplet。在這里,每個(gè) Chiplet也可以根據(jù)最有意義的技術(shù)進(jìn)行設(shè)計(jì)。”

這在某些方面簡(jiǎn)化了事情,因?yàn)?PCIe 或 SerDes 等傳統(tǒng) I/O 仍然可以與前沿邏輯結(jié)合使用。“這可能不會(huì)改變你在電路板上使用的東西與你在裸片上使用的東西之間的 I/O 連接,”Cadence IP 組產(chǎn)品營(yíng)銷組總監(jiān) Wendy Wu 說(shuō)。“但對(duì)于 Chiplet方法,設(shè)計(jì)團(tuán)隊(duì)會(huì)使用更多新興的 die-to-die I/O,它的功耗非常低,五年前可能還不存在。”

Chiplet通常并排集成,但它們也可以使用中介層或 3D-IC 堆疊在 2.5D 封裝中。Park 預(yù)計(jì)硅中介層封裝不會(huì)繼續(xù)下去,并相信有機(jī)中介層和互連橋會(huì)得到推動(dòng)。

多個(gè)模塊的額外問(wèn)題

Multiple-die 系統(tǒng)的一個(gè)重要考慮因素是協(xié)同設(shè)計(jì)。“當(dāng)工程團(tuán)隊(duì)開(kāi)始將這些系統(tǒng)組裝成組件時(shí),他們無(wú)法知道限制是什么,直到他們定義了該組裝系統(tǒng)將是什么,”Siemens Digital 的 Calibre 接口和 mPower 產(chǎn)品管理高級(jí)總監(jiān) Joseph Davis 說(shuō)行業(yè)軟件。“人們現(xiàn)在最想做的事情之一就是將來(lái)自不同制造商的 Chiplet組合在一起。這變成了一個(gè)系統(tǒng)問(wèn)題,所有的模型和限制現(xiàn)在都來(lái)自不同的代工廠并流向第三方。從 IP 的角度來(lái)看,這是非常具有挑戰(zhàn)性的。如果你真的想從集成的角度突破你能做的事情的界限。

鑒于當(dāng)今的復(fù)雜程度,每個(gè)堆棧都是獨(dú)一無(wú)二的。“你不能只說(shuō)適用于 2.5D 的內(nèi)容也適用于 3D,”Davis 指出。“當(dāng)你開(kāi)始構(gòu)建這些東西時(shí),你會(huì)遇到直接的技術(shù)兼容性問(wèn)題。即使在一個(gè)代工廠內(nèi),每次客戶說(shuō),’嘿,我想做這個(gè)堆棧,‘他們必須定義,’我想把這個(gè)芯片和這個(gè)芯片放在一起,然后把這個(gè)芯片和這個(gè)中介層放在一起。然后,該代工廠必須與所涉及的 EDA 供應(yīng)商合作,以提供所有相關(guān)的抵押品。你不能只是拿標(biāo)準(zhǔn)的 PDK 并在它們周圍放一些打包線。”

Synopsys 的 Kapoor 認(rèn)為第一個(gè)挑戰(zhàn)是為心目中的產(chǎn)品定義規(guī)范。“例如,這可能是你的下一個(gè)移動(dòng)設(shè)計(jì)或下一個(gè)數(shù)據(jù)服務(wù)器設(shè)計(jì)。所以現(xiàn)在你必須打破它。你怎么打破它?從系統(tǒng)功能的角度來(lái)看,硬件負(fù)責(zé)哪些部分?哪些部分由軟件處理?對(duì)于某些客戶來(lái)說(shuō),這很容易。這只是記憶凌駕于邏輯之上,或者說(shuō)邏輯凌駕于記憶之上。但是當(dāng)你拆分邏輯時(shí),它會(huì)使事情變得非常復(fù)雜。它分為許多部分。關(guān)鍵部件是什么?GPU、CPU 和 I/O。如何將它們放入理想的包裝中?將使用哪種互連結(jié)構(gòu)來(lái)幫助滿足某些限制和規(guī)范?這些決定過(guò)去非常簡(jiǎn)單,只需在 PowerPoint 或 Excel 或 Visio 中完成。”

現(xiàn)在,更復(fù)雜的工具是探索目的所必需的。“這些工具必須更加復(fù)雜才能預(yù)先進(jìn)行一些分析,”Kapoor 說(shuō)。“Thermal 是典型的例子。除非設(shè)計(jì)團(tuán)隊(duì)在進(jìn)行 PCB 封裝設(shè)計(jì)或系統(tǒng)設(shè)計(jì),否則他們從來(lái)不會(huì)考慮熱問(wèn)題。現(xiàn)在這些問(wèn)題很早就出現(xiàn)了,所以他們?cè)谶M(jìn)行早期架構(gòu)設(shè)計(jì)時(shí)必須開(kāi)始將熱力作為一個(gè)約束來(lái)考慮。一旦你決定了如何拆分設(shè)計(jì),那么從封裝和連接的角度來(lái)看,最佳和最具成本效益的配置是什么?你還會(huì)滿足你的 PPA 嗎?PPA 總是會(huì)存在,現(xiàn)在你被分割開(kāi)來(lái)了。這怎么會(huì)出現(xiàn)在畫(huà)面中?

啟用Chiplet

在過(guò)去五年左右的時(shí)間里,衍生設(shè)計(jì)變得更具挑戰(zhàn)性。Siemens的 Davis說(shuō):“如果你采用了一項(xiàng)核心技術(shù),就會(huì)開(kāi)始一種更長(zhǎng)的跨越式發(fā)展。” “然后是下一項(xiàng)新技術(shù),再次將其翻倍。所以業(yè)界開(kāi)始說(shuō),‘等等,那是不是說(shuō)Chiplet,可以讓我做2個(gè)、4個(gè)甚至8個(gè)模塊,把它放在substrate上,而無(wú)需進(jìn)行新的流片?‘ 這一切都在組裝層面,而非硅,這非常有吸引力。”

這的確很有吸引力,但也并不簡(jiǎn)單。對(duì)于初創(chuàng)公司甚至中型公司而言,這種方法的復(fù)雜性可能令人望而生畏。“對(duì)于一個(gè)單一裸片,有一大堆不同的集成商可以處理這種封裝模型和集成,并與代工廠合作。而現(xiàn)在你需要做一個(gè)自定義集合。能做到這一點(diǎn)的人要少得多。你現(xiàn)在是否將它帶到內(nèi)部來(lái)執(zhí)行此操作并驗(yàn)證你的功能,因?yàn)楝F(xiàn)在在系統(tǒng)驗(yàn)證方面需要做更多的工作?從系統(tǒng)的角度來(lái)看,可靠性驗(yàn)證變得更加困難,自制還是外購(gòu)決策也變得更加復(fù)雜。你的“做出”決定可能意味著雇用五個(gè)人而不是一個(gè)人。順便說(shuō)一下,這個(gè)國(guó)家以前只有5個(gè)人有過(guò)這方面經(jīng)驗(yàn)。這在很大程度上是一種引導(dǎo)性的努力。’嗨,我們需要找一些有 5 年以上 SiP 和 3D stacking 經(jīng)驗(yàn)的人。嗯??等等,這個(gè)技術(shù)好像剛開(kāi)始不到3年。”

在芯片的預(yù)計(jì)使用壽命內(nèi)確保可靠性變得更具挑戰(zhàn)性。Kapoor 說(shuō):“因?yàn)槟悴鸱至薲ie,你現(xiàn)在有更多的互連,更多的接口,其中任何一個(gè)都可能失敗,任何一個(gè)都可能成為安全問(wèn)題的切入點(diǎn)。” “關(guān)于KGD(known good die)有很多說(shuō)法,但如何引入它的監(jiān)控部分,以及如何確保它在整個(gè)流程中都是可觀察的、可優(yōu)化的和可測(cè)試的?這些都是已經(jīng)出現(xiàn)的新挑戰(zhàn)。”

除此之外,工程團(tuán)隊(duì)要如何有效地完成以上這些工作?如果說(shuō)單芯片設(shè)計(jì)很難,那么多芯片系統(tǒng)則需要新模型和標(biāo)準(zhǔn)化。

“ Chiplet的傳統(tǒng)工作方式是基于一些驅(qū)動(dòng)和接收信號(hào)、處理 SD 和測(cè)試等的微緩沖器的 die-to-die 通信包裝器,”Cadence 的 Park 說(shuō)。“我們?cè)诟蟮男酒峡吹搅送瑯拥氖虑椤5F(xiàn)在它們更小了,因?yàn)槲覀儧](méi)有一直延伸到電路板的大電容負(fù)載。這意味著你離開(kāi)了諸如時(shí)序分析之類的世界,即觸發(fā)器到觸發(fā)器的時(shí)序,你在其中通過(guò)混合鍵在兩個(gè)不同的設(shè)備之間移動(dòng)。在multiple-die設(shè)計(jì)中,需要驗(yàn)證合規(guī)性,這可能基于 AIB、UCIe、BoW 或其他。有許多新興的 Chiplet標(biāo)準(zhǔn),你現(xiàn)在需要驗(yàn)證這些標(biāo)準(zhǔn)的信號(hào)完整性。你實(shí)質(zhì)上是通過(guò)一些具有正確信號(hào)行為的互連通道來(lái)驗(yàn)證收發(fā)器到接收器,并且該接口上沒(méi)有太多抖動(dòng)或噪聲。這使得信號(hào)完整性成為一個(gè)系統(tǒng)級(jí)問(wèn)題,業(yè)界已經(jīng)這樣做了 40 多年。”

問(wèn)題是芯片設(shè)計(jì)者不一定知道如何做到這一點(diǎn)。“數(shù)字方面的芯片設(shè)計(jì)人員只關(guān)心觸發(fā)器到觸發(fā)器的時(shí)序,這與理解信號(hào)完整性類型挑戰(zhàn)的重要性截然不同。出于所有這些原因,你需要把 multiple-die 設(shè)計(jì)和3D 異構(gòu)集成當(dāng)做一個(gè)系統(tǒng)來(lái)設(shè)計(jì),而不是一個(gè)單片芯片。”

審核編輯 :李倩

-

芯片

+關(guān)注

關(guān)注

460文章

52520瀏覽量

441086 -

晶體管

+關(guān)注

關(guān)注

77文章

10020瀏覽量

141732 -

chiplet

+關(guān)注

關(guān)注

6文章

459瀏覽量

13003 -

奇異摩爾

+關(guān)注

關(guān)注

0文章

61瀏覽量

3739 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

476瀏覽量

628 -

芯粒

+關(guān)注

關(guān)注

0文章

67瀏覽量

279

原文標(biāo)題:進(jìn)入 Chiplet 時(shí)代,設(shè)計(jì)將發(fā)生哪些轉(zhuǎn)變?

文章出處:【微信號(hào):奇異摩爾,微信公眾號(hào):奇異摩爾】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Chiplet與先進(jìn)封裝設(shè)計(jì)中EDA工具面臨的挑戰(zhàn)

淺談Chiplet與先進(jìn)封裝

Chiplet:芯片良率與可靠性的新保障!

如何檢測(cè)材料的玻璃化轉(zhuǎn)變溫度?

2025 CES落幕,AI定義汽車時(shí)代正式啟航

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

ESG報(bào)告進(jìn)入“強(qiáng)信披”時(shí)代,企業(yè)面臨新挑戰(zhàn)

Chiplet在先進(jìn)封裝中的重要性

Chiplet技術(shù)有哪些優(yōu)勢(shì)

Chiplet將徹底改變半導(dǎo)體設(shè)計(jì)和制造

2035年Chiplet市場(chǎng)規(guī)模將超4110億美元

IMEC組建汽車Chiplet聯(lián)盟

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺(tái)

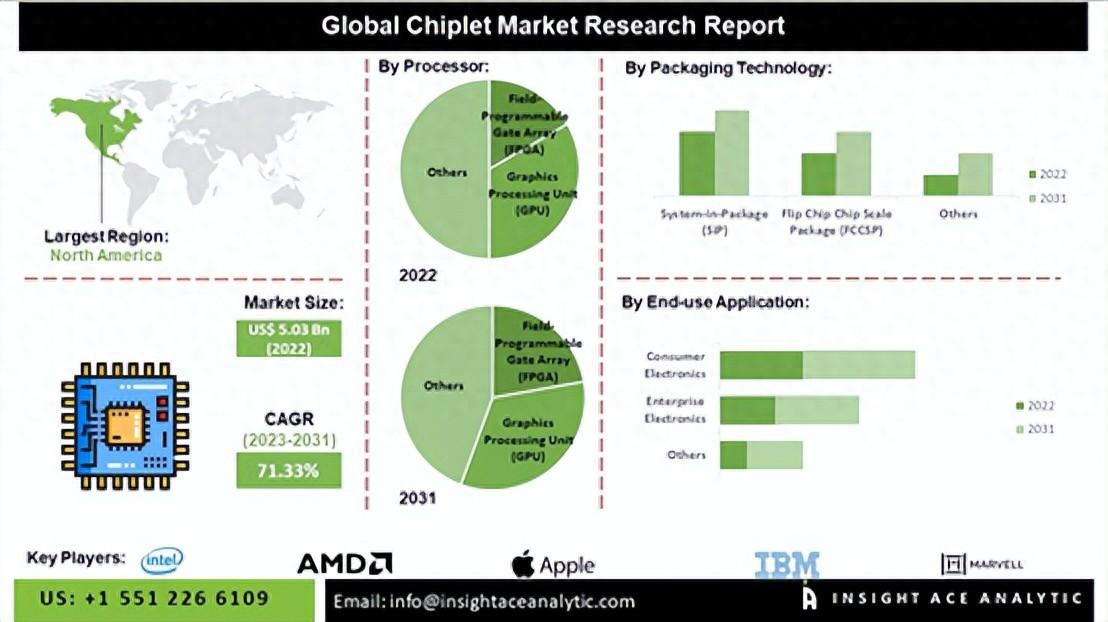

2031年全球Chiplet市場(chǎng)預(yù)測(cè)

剖析 Chiplet 時(shí)代的布局規(guī)劃演進(jìn)

進(jìn)入Chiplet時(shí)代,設(shè)計(jì)將發(fā)生哪些轉(zhuǎn)變?

進(jìn)入Chiplet時(shí)代,設(shè)計(jì)將發(fā)生哪些轉(zhuǎn)變?

評(píng)論