完善資料讓更多小伙伴認識你,還能領取20積分哦,立即完善>

標簽 > chiplet

chiplet是什么意思?chiplet國內公司有哪些?chiplet關鍵技術在哪里?chiplet對行業的優劣怎么評估? chiplet工藝和chiplet和SoC區別分析,這里一文讀懂chiplet!

chiplet 的概念其實很簡單,就是硅片級別的重用。設計一個系統級芯片,以前的方法是從不同的 IP 供應商購買一些 IP,軟核(代碼)或硬核(版圖),結合自研的模塊,集成為一個 SoC,然后在某個芯片工藝節點上完成芯片設計和生產的完整流程。

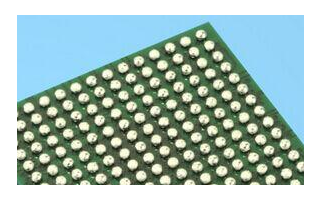

很多的行業大佬都把chiplet 看成是未來芯片的重要基礎技術。簡單來說,chiplet 技術就是像搭積木一樣,把一些預先生產好的實現特定功能的芯片裸片(die)通過先進的集成技術(比如 3D integration)集成封裝在一起形成一個系統芯片。而這些基本的裸片就是 chiplet。從這個意義上來說,chiplet 就是一個新的 IP 重用模式。未來,以 chiplet 模式集成的芯片會是一個“超級”異構系統,可以為 AI 計算帶來更多的靈活性和新的機會。

chiplet 的概念最早來自 DARPA 的 CHIPS(Common Heterogeneous Integration and IP Reuse Strategies)項目。該項目試圖解決的主要問題如下“The monolithic nature of state-of-the-art SoCs is not always acceptable for DoD or other low-volume applications due to factors such as high initial prototype costs and requirements for alternative material sets. To enhance overall system flexibility and reduce design time for next-generation products, the Common Heterogeneous Integration and Intellectual Property (IP) Reuse Strategies (CHIPS) program seeks to establish a new paradigm in IP reuse.”。而它的愿景是:“The vision of CHIPS is an ecosystem of discrete modular, reusable IP blocks, which can be assembled into a system using existing and emerging integration technologies. Modularity and reusability of IP blocks will require electrical and physical interface standards to be widely adopted by the community supporting the CHIPS ecosystem. Therefore, the CHIPS program will develop the design tools and integration standards required to demonstrate modular integrated circuit (IC) designs that leverage the best of DoD and commercial designs and technologies.” 從這段描述來看 chiplet 可以說是一種新的芯片設計模式,要實現 chiplet 這種新的 IP 重用模式,首先要具備的技術基礎就是先進的芯片集成封裝技術。

奇異摩爾榮獲2025中國創新IC強芯-創新突破獎,助力國產化芯片技術突破

7月11日,2025年度中國創新IC-強芯獎頒獎典禮在ICDIA創芯展上揭曉獲獎名單。 奇異摩爾申報的Kiwi 3D Base Die產品從申報的142...

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布擴大與三星晶圓代工廠的合作,包括簽署一項新的多年期 IP 協議,在三星晶圓代工廠的...

7月15日,由“集成芯片前沿技術科學基礎”重大研究計劃指導,中國科學院計算技術研究所、中國電子科技集團公司第五十八研究所主辦的第三屆芯粒開發者大會即將在...

專家對話:新思科技×無問芯穹 AI與EDA的雙向賦能,重構芯片設計,破局算力瓶頸

2025年5月23日,新思科技直播間邀請到清華大學電子工程系博士、博士后曾書霖(無問芯穹001號員工)、無問芯穹智能終端技術總監胡楊,以及新思科技戰略生...

Cadence攜手臺積公司,推出經過其A16和N2P工藝技術認證的設計解決方案,推動 AI 和 3D-IC芯片設計發展

同時宣布針對臺積公司 N3C 工藝的工具認證完成,并基于臺積公司最新 A14 技術展開初步合作 中國上海,2025 年 5 月 23 日——楷登電子(美...

從產業格局角度分析Chiplet技術的戰略意義,華芯邦如何通過技術積累推動中國從“跟跑”到“領跑”。

換一批

換一批

編輯推薦廠商產品技術軟件/工具OS/語言教程專題

| 電機控制 | DSP | 氮化鎵 | 功率放大器 | ChatGPT | 自動駕駛 | TI | 瑞薩電子 |

| BLDC | PLC | 碳化硅 | 二極管 | OpenAI | 元宇宙 | 安森美 | ADI |

| 無刷電機 | FOC | IGBT | 逆變器 | 文心一言 | 5G | 英飛凌 | 羅姆 |

| 直流電機 | PID | MOSFET | 傳感器 | 人工智能 | 物聯網 | NXP | 賽靈思 |

| 步進電機 | SPWM | 充電樁 | IPM | 機器視覺 | 無人機 | 三菱電機 | ST |

| 伺服電機 | SVPWM | 光伏發電 | UPS | AR | 智能電網 | 國民技術 | Microchip |

| 開關電源 | 步進電機 | 無線充電 | LabVIEW | EMC | PLC | OLED | 單片機 |

| 5G | m2m | DSP | MCU | ASIC | CPU | ROM | DRAM |

| NB-IoT | LoRa | Zigbee | NFC | 藍牙 | RFID | Wi-Fi | SIGFOX |

| Type-C | USB | 以太網 | 仿真器 | RISC | RAM | 寄存器 | GPU |

| 語音識別 | 萬用表 | CPLD | 耦合 | 電路仿真 | 電容濾波 | 保護電路 | 看門狗 |

| CAN | CSI | DSI | DVI | Ethernet | HDMI | I2C | RS-485 |

| SDI | nas | DMA | HomeKit | 閾值電壓 | UART | 機器學習 | TensorFlow |

| Arduino | BeagleBone | 樹莓派 | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| 示波器 | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | 華秋DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |