引 言

摩爾定律在設(shè)計、制造、封裝3個維度上推動著集成電路行業(yè)發(fā)展。隨著硅工藝節(jié)點的逐代更新,每平方毫米的晶體管數(shù)量從1.8萬個增加到5000萬個,芯片功能也從單純的數(shù)字邏輯擴展到集數(shù)模轉(zhuǎn)換、FPGA、存儲器件、高速接口于一體,這一進程推動了片上系統(tǒng)(SoC)的產(chǎn)生,從而將電子信息系統(tǒng)的發(fā)展推向了新的高度[1]。

隨著SoC的發(fā)展,其高復(fù)雜度、長周期、低良率的特點導致制程微縮的研發(fā)投入和加工成本急劇攀升。為了解決這些問題,將不同功能的模塊從大規(guī)模單芯片上解耦成為新的發(fā)展方向。通過將多個單功能或多功能的IP核芯片化,再通過中后道技術(shù)對其進行復(fù)用和集成,以形成1個完整的系統(tǒng),即芯粒(Chiplet)架構(gòu)技術(shù)[2-4]。相較于傳統(tǒng)的SoC技術(shù),Chiplet架構(gòu)技術(shù)的各計算單元和接口可以選擇不同的工藝制程,以滿足不同器件的異構(gòu)集成需求。由于單顆Chiplet的面積小,其制造過程中的良率得以提升,從而可以降低制造成本。同一款Chiplet可以在不同產(chǎn)品中重復(fù)應(yīng)用,不同款Chiplet可以根據(jù)市場需求靈活組合,以縮短產(chǎn)品上市時間。2022年初,Intel發(fā)布了UCIe標準[5-7],該標準對Chiplet協(xié)議層、芯片間適配、物理層、接口等內(nèi)容進行了規(guī)范性描述,并更新了時鐘結(jié)構(gòu)、功率噪聲、電源效率等內(nèi)容。2022年12月,由國內(nèi)集成電路領(lǐng)域的相關(guān)企業(yè)和專家制定的《小芯片接口總線技術(shù)要求》團體標準發(fā)布。2023年初,中國Chiplet產(chǎn)業(yè)聯(lián)盟牽頭發(fā)布《芯粒互連接口標準》。在中美貿(mào)易摩擦升級、技術(shù)制裁加劇的背景下,國內(nèi)正不斷研究UCIe的兼容和替代方案,以不斷提升自身的技術(shù)實力和競爭力。

本文圍繞UCIe中關(guān)于電氣物理層的相關(guān)內(nèi)容,對不同封裝類型和互連通道的電氣指標進行解讀,并結(jié)合有機基板工藝,從設(shè)計和仿真的角度探討了應(yīng)對Chiplet互連的標準封裝方案的技術(shù)可行性,有助于推動國內(nèi)芯粒互連集成技術(shù)的發(fā)展。

01

Chiplet封裝方案及模型

1.1典型Chiplet封裝方案

按照封裝結(jié)構(gòu),系統(tǒng)集成技術(shù)可分為2D、2.5D和3D封裝;按照封裝材料,基板可分為硅基板和有機基板;在UCIe中,Chiplet封裝方案分為先進封裝方案和標準封裝方案。

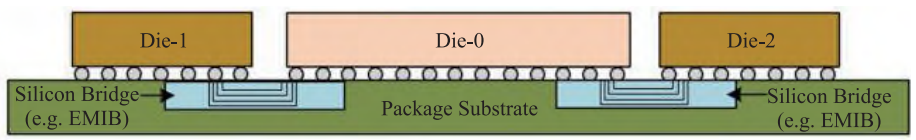

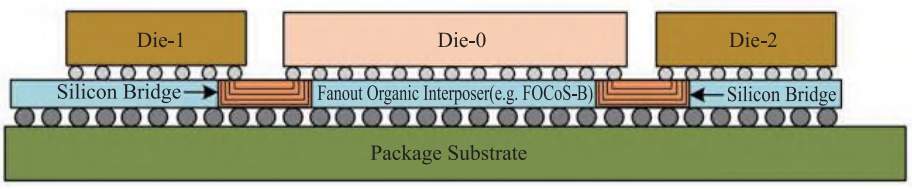

在UCIe中,采用先進封裝方案的模塊被稱為先進封裝模塊,1個先進封裝模塊應(yīng)當包含1對時鐘,64個單端數(shù)據(jù)通道(用于發(fā)送和接收數(shù)據(jù)的有效通道)以及1個跟蹤通道。典型的先進封裝技術(shù)包括Intel的嵌入式多芯片互連橋接(EMIB)技術(shù)、臺積電的CoWoS(Chip on Wafer on Substrate)技術(shù)[9]以及日月光的FOCoS-B(Fan-Out Chip on Substrate Bridge)技術(shù),不同先進封裝方案的結(jié)構(gòu)如圖1所示。以上3種先進封裝技術(shù)的共同特點是采用2.5D異構(gòu)集成方式,將硅基板埋嵌在有機基板中以實現(xiàn)混合使用,利用硅基板實現(xiàn)高密度、短互連,利用有機基板完成剩余互連。先進封裝方案適用于具備多引腳和高帶寬需求的產(chǎn)品,如高帶寬存儲(HBM)接口,其由1 024個I/O引腳組成,并需要滿足100 GB/s以上的帶寬要求,其缺點是加工成本很高,難以實現(xiàn)長距離互連,在靈活性方面存在不足。

(a) 嵌入橋接芯片基板(EMIB)

(b)硅轉(zhuǎn)接板2.5D集成(CoWoS)

(c) 有機轉(zhuǎn)接板2.5D集成(FOCoS----﹣--B)

圖1不同先進封裝技術(shù)結(jié)構(gòu)

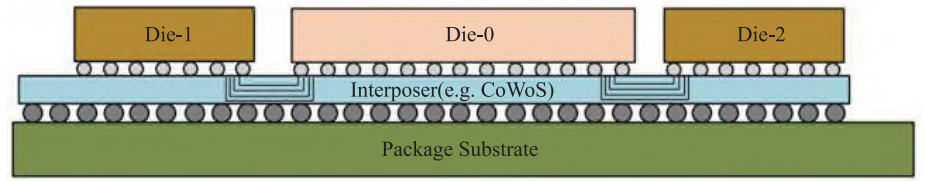

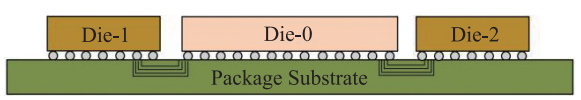

在UCIe中,標準封裝方案依托于2D結(jié)構(gòu),通過有機基板實現(xiàn)互連,采用標準封裝方案的結(jié)構(gòu)如圖2所示。每個標準封裝模塊由1對時鐘、16個單端數(shù)據(jù)通道以及1個跟蹤通道組成。典型的集成Chiplet的標準封裝技術(shù),其代表是AMD公司提出的IF(Infinity Fabric)技術(shù),其分布式架構(gòu)由可擴展數(shù)據(jù)結(jié)構(gòu)和可擴展控制結(jié)構(gòu)組成,已經(jīng)在第一代和第二代的霄龍處理器中得到應(yīng)用。標準封裝方案的技術(shù)成熟且成本較低,有機基板具有較低的介質(zhì)損耗,能夠滿足高頻率、高速、長距離的信號傳輸需求,布線靈活度高,適用于各種集成方案。標準封裝方案的主要缺點是互連密度低,導致帶寬受限。

圖2采用標準封裝方案的結(jié)構(gòu)

1.2Chiplet封裝電氣互連驗證

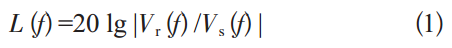

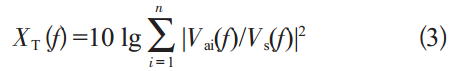

在UCIe中,針對標準封裝和先進封裝方案中的電氣互連通道,采用電壓傳遞函數(shù)(VTF)作為衡量電氣互連通道損耗和串擾的指標。VTF可以基于發(fā)送端(TX)/接收端(RX)的阻容分量(Rt、Ct、Rr、Cr)對無源通道的微波散射參數(shù)(S參數(shù))進行轉(zhuǎn)換。相較于使用S參數(shù),使用VTF可以綜合地評估電氣互連通道的性能。將VTF損耗定義為L(f),L(f)為TX電壓Vr(f)與RX電壓Vs(f)的比值,單位為dB,其計算公式為

在直流情形下,將直流耗損定義為L(0),其與通道寄生電阻Rchannel相關(guān),L(0)的計算公式為

其中,Rt為TX的電阻,Ct為TX的電容,Rr為RX的電阻、Cr為RX的電容。

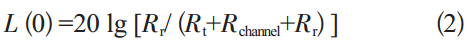

將VTF串擾定義為XT(f),其為非預(yù)期接收端與發(fā)送端功率比的疊加,XT(f)的計算公式為

其中,n為非預(yù)期接收端數(shù)量,Vai(f)為對應(yīng)非預(yù)期接收端觀測電壓。

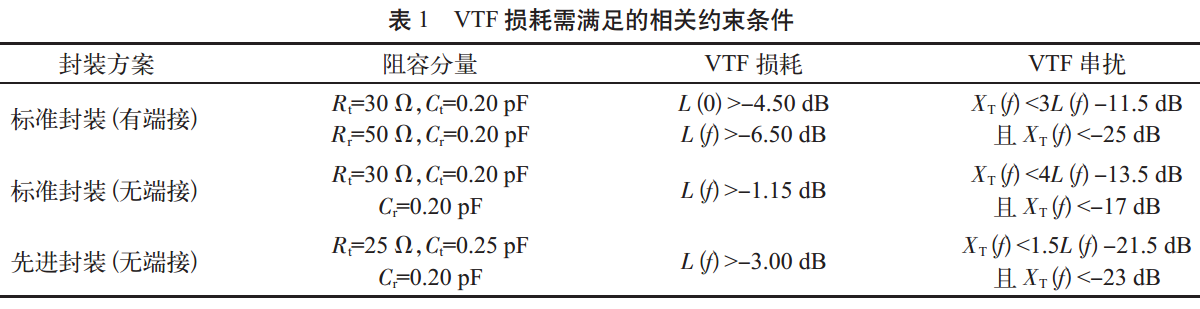

在兩端阻容作用下,VTF曲線與S參數(shù)在描述傳輸通道的頻域特性方面存在明顯的不同。因此,在UCIe中,在16 Gbit/s的速率下,VTF損耗需要滿足一定的約束條件,相關(guān)約束條件如表1所示。

表1VTF損耗需滿足的相關(guān)約束條件

市面上暫時沒有用于VTF仿真的專用工具,為進一步解讀UCIe中的指標,采用Keysight ADS仿真工具中的傳輸線模組,通過交流仿真模塊的轉(zhuǎn)換,對比3種阻容配置下的VTF損耗和VTF串擾,如圖3所示,同時比較特定驅(qū)動能力下的RX眼圖。

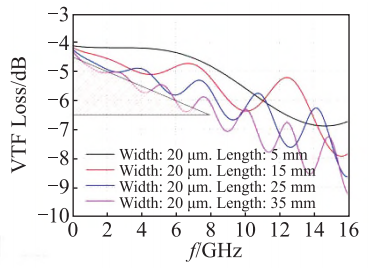

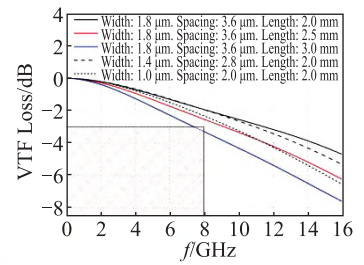

(a)線長對VTF損耗的影響(標準封裝50 Ω端接)

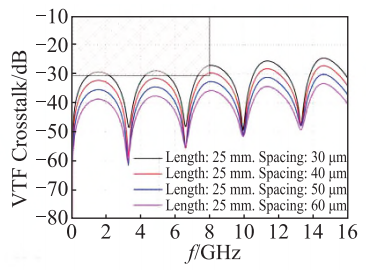

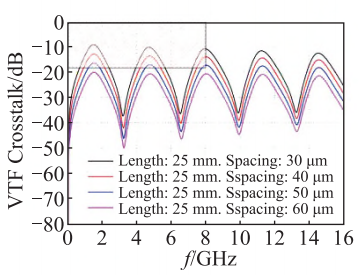

(b)線距對VTF串擾的影響(標準封裝50 Ω端接)

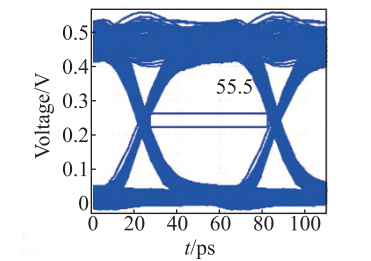

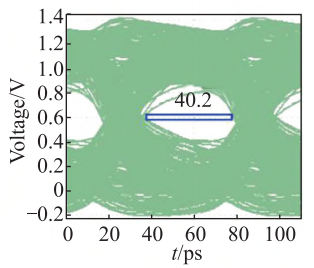

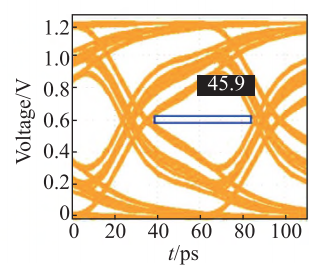

(c)線長25 mm、線寬20 μm、線距40 μm條件下的眼圖(標準封裝50 Ω端接)

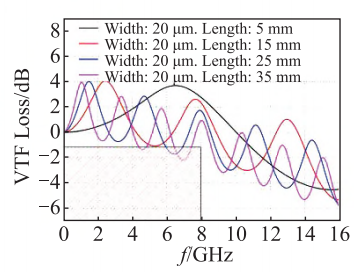

(d)線長對VTF損耗的影響(標準封裝無端接)

(e)線距對VTF串擾的影響(標準封裝無端接)

(f)線長25 mm、線寬20 μm、線距40 μm條件下的眼圖(標準封裝無端接)

(g)線長對VTF損耗的影響(先進封裝無端接)

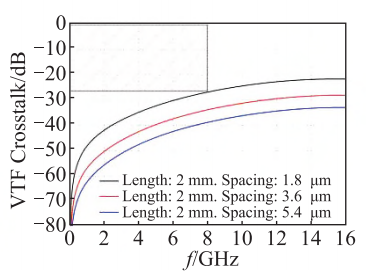

(h)線距對VTF串擾的影響(先進封裝無端接)

(i)線長2 mm、線寬1.8 μm、線距3.6 μm條件下的眼圖(先進封裝無端接)

圖316 Gbit/s速率下3種阻容配置的VTF損耗、VTF串擾及對應(yīng)眼圖

按照無錫中微高科電子有限公司的有機基板設(shè)計標準進行設(shè)計,使用的介質(zhì)材料的相對介電常數(shù)DK=3.2、介電損耗角正切DF=0.006,將線寬設(shè)計為20 μm,以匹配50 Ω的特征阻抗。與端口匹配的插入損耗相比,VTF損耗曲線呈現(xiàn)隨頻率和線長的增加而增大的趨勢。RX端接50 Ω電阻時,直流損耗偏離0點,而VTF損耗呈現(xiàn)與線長相關(guān)的振蕩周期。在UCIe中,當頻率為0~8 GHz時,要求VTF損耗不侵入mask區(qū)域(評估VTF損耗是否符合要求的閾值)。從圖3(a)可知,當線長大于25 mm時,VTF損耗會超出限定范圍。從圖3(b)可知,當線距為40 μm時,紅色曲線在8 GHz附近侵入mask區(qū)域,此時常規(guī)的封裝設(shè)計無法滿足VTF串擾的限定范圍,因此,當線寬為20 μm時,線距應(yīng)大于40 μm,即大于2倍的線寬。在實際設(shè)計中,需要進一步確保布線和過孔的回流效果。通過使用具有9 mA等效驅(qū)動能力的TX緩沖器,能夠在50 Ω端接條件下驅(qū)動RX,實現(xiàn)450 mV的電壓擺幅。從圖3(c)可知,眼高為40 mV,眼寬為55.5 ps(0.89 UI),滿足UCIe要求。

在無端接條件下,標準封裝的互連線性能受到寄生電感和RX電容的影響。從圖3(d)可知,直流損耗為0,在寄生電感與RX電容共同作用的儲能振蕩下,VTF損耗在0~8 GHz甚至更寬的頻段內(nèi)出現(xiàn)大于0的現(xiàn)象,為了避開前幾個VTF損耗波谷,互連線長度需要被限制在15 mm以下。從圖3(e)可知,當線距與線寬比為2.5時,藍色曲線侵入mask區(qū)域,無法滿足VTF串擾要求,這說明反射疊加進一步加重了串擾問題。在相同的驅(qū)動條件下,眼圖的塌陷和抖動變得嚴重,眼寬僅為40.2 ps(0.64 UI),如圖3(f)所示。

在UCIe中,先進封裝方案要求的通道互連長度僅為2 mm,標準封裝方案要求的通道互連長度為25 mm,該標準主要考慮到在先進工藝條件下,通道互連長度會受到50 Ω阻抗偏離和微小尺寸的寄生效應(yīng)限制。在1.8 μm線寬工藝中,寄生電阻的量級達到了10 Ω/mm。從圖3(g)可知,隨著線長的增加,VTF損耗快速增大。在理想模型下,3 mm的通道互連長度已超出標準。同時,線寬變小同樣會導致VTF損耗的增大,這成為先進封裝方案中提升布線密度與保障傳輸質(zhì)量之間的主要矛盾之一。先進封裝方案未配置電阻性端接,較短的通道互連長度下信號反射的影響變小,薄介質(zhì)層導致傳輸線與回流平面緊密耦合,線距小于等于2倍的線寬也可以滿足VTF串擾的要求,線距對VTF串擾的影響如圖3(h)所示。從圖3(i)可知,在相同驅(qū)動下,線路的寄生電阻導致電平轉(zhuǎn)換邊沿塌陷嚴重,眼寬為45.9 ps(0.73 UI)。

基于相對理想的傳輸模型,針對UCIe中對不同封裝方案和阻容配置的約束條件進行驗證。結(jié)果表明,先進封裝(無端接)和標準封裝(無端接)方案能夠?qū)崿F(xiàn)更優(yōu)的空間配置,而標準封裝(有端接)方案在常規(guī)端接配置下最大限度地保留了通道性能完整性。在此基礎(chǔ)上,以無錫中微高科電子有限公司的有機基板工藝為依托,對標準封裝方案的布局進行設(shè)計,本團隊進一步考慮了實際布線中過孔、焊盤、繞線等工藝結(jié)構(gòu)對通道性能的具體影響,最終目標是為了達到UCIe的設(shè)計要求。

02

Chiplet標準封裝方案設(shè)計與信號完整性仿真

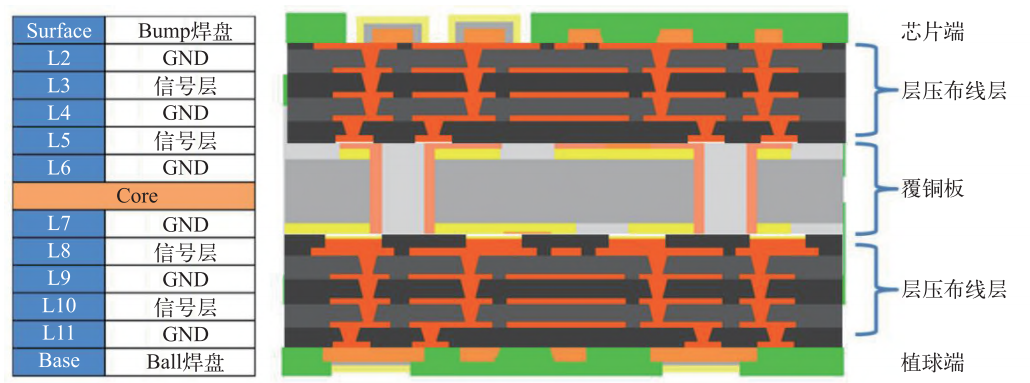

本文提出的高密度基板工藝是通過在覆銅板的兩面實施電鍍通孔銅柱、介質(zhì)層壓合、表面研磨、圖形化布線的重復(fù)流程,實現(xiàn)多層布線。有機基板工藝的最小線寬/線距為20 μm/20 μm,在芯片倒裝區(qū)域,線寬/線距可進一步縮小為15 μm/15 μm。高密度基板的層疊結(jié)構(gòu)與高速信號層的分布如圖4所示,在最高12層的布線結(jié)構(gòu)下,為了確保高速信號的完整性,采用電源/地-信號-電源/地的帶狀線布局,將L3/L5/L8/L10層作為高速信號的布線層。

圖4高密度基板的層疊結(jié)構(gòu)與高速信號層的分布

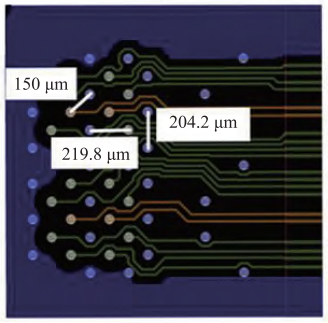

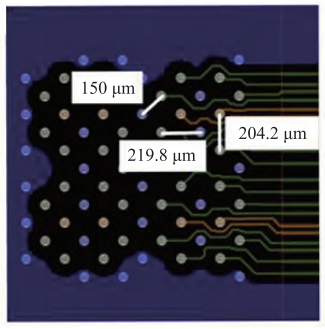

在UCIe中,理想的凸點節(jié)距是100~130 μm,以確保所需的互連帶寬密度。制造商可以根據(jù)自身的實際工藝能力進行調(diào)整,聯(lián)華電子股份有限公司采用了146 μm的凸點節(jié)距。本團隊在有機基板設(shè)計過程中,遵循加工規(guī)范要求的節(jié)距(150 μm),根據(jù)UCIe要求的凸點布局方式,計算出垂直互連引線方向上單個TX/RX模塊的邊緣寬度為612.6 μm。若在單層上實現(xiàn)20個通道(含時鐘、有效信號、跟蹤信號)的布線,通道的平均寬度僅為30.6 μm,因此,在芯片的倒裝區(qū)域?qū)崿F(xiàn)合理的布線設(shè)計非常困難。采用雙層布線通道的設(shè)計,通道的平均寬度增加為61.3 μm,有助于實現(xiàn)合理的布線設(shè)計。

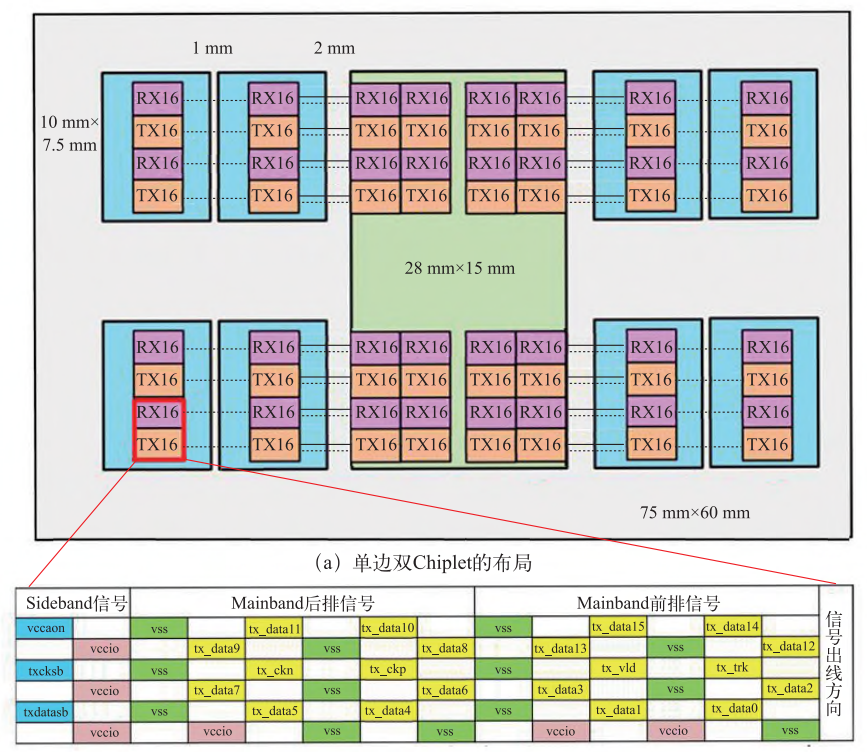

參照AMD公司IF技術(shù)的分布式架構(gòu)設(shè)計,采用單邊雙Chiplet的布局,主Chiplet的尺寸為28 mm×15 mm,主Chiplet周圍分布8個小Chiplet,每個尺寸為10 mm×7.5 mm。TX/RX接口被有序地排列在小Chiplet的中央?yún)^(qū)域和主Chiplet的長邊邊緣位置,這些接口通過4層走線實現(xiàn)了全通道的互連。將常規(guī)區(qū)域的線寬/線距設(shè)置為20 μm/40 μm,其中近端Chiplet的前、后排信號分別在L3、L5層進行布線設(shè)計,信號線長約為10 mm;遠端Chiplet的前、后排信號分別在L8、L10層進行布線設(shè)計,信號線長約為25 mm。實際的互連密度為每毫米60個通道。在單通道數(shù)據(jù)傳輸速率為32 GT/s的條件下,每毫米的帶寬達到了240 GB/s,該設(shè)計滿足UCIe的帶寬要求。Chiplet集成布局模型如圖5所示。

(b)Chiplet的TX/RX接口布局

(c)單元后排引腳布線設(shè)計

(d)單元前排引腳布線設(shè)計

圖5Chiplet集成布局模型

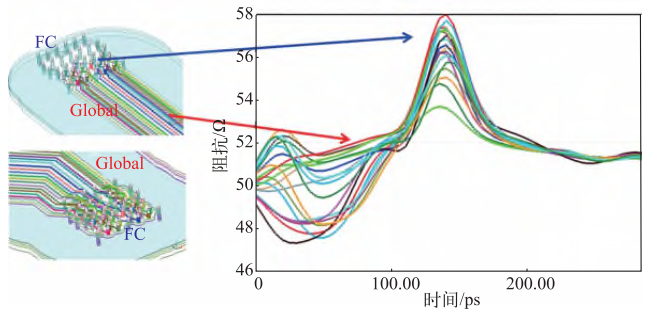

采用高頻電磁仿真工具Ansys HFSS對互連模型中的無源通道進行模擬和分析。使用Ansys HFSS的時域反射阻抗(TDR)分析功能對常規(guī)走線(Global)區(qū)域的特性阻抗進行測量,走線區(qū)域的特征阻抗為50~52 Ω,其與預(yù)期設(shè)計相符。在Chiplet倒裝區(qū)域,由于線寬變小并且通孔對應(yīng)位置的回流平面被挖空,導致局部的特征阻抗偏高,基板互連的結(jié)構(gòu)模型與TDR仿真曲線如圖6所示。

圖6基板互連結(jié)構(gòu)模型與TDR仿真曲線

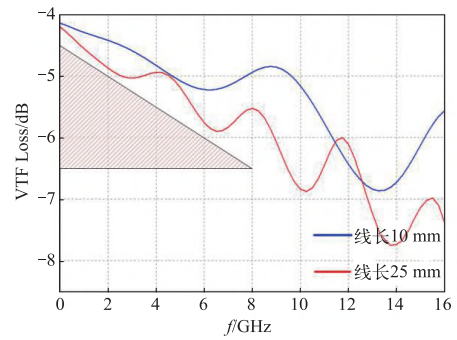

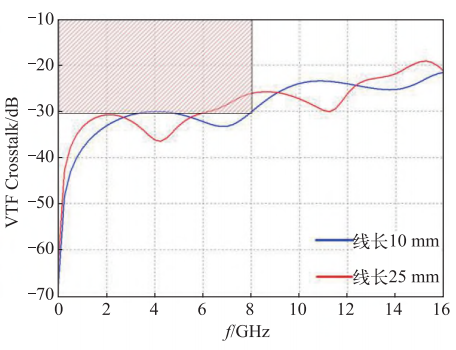

使用Ansys HFSS提取了S參數(shù),將其轉(zhuǎn)換為VTF。近端Chiplet(互連線長為10 mm)和遠端Chiplet(互連線長為25 mm)的VTF損耗如圖7(a)所示。當頻率為8 GHz時,近端Chiplet的VTF損耗為-4.94 dB,遠端Chiplet的VTF損耗為-5.56 dB,均符合UCIe要求。兩者之間的差異主要來源于兩端阻容負載產(chǎn)生的反射振蕩。盡管倒裝區(qū)域的局部阻抗有所突變,但其對整體性能的影響相對有限。近端Chiplet和遠端Chiplet的VTF串擾如圖7(b)所示,當頻率為8 GHz時,近端Chiplet的VTF串擾為-30.16 dB,遠端Chiplet的VTF串擾為-26.12 dB。產(chǎn)生串擾的主要原因為當參考地平面回流能力不足時,鄰近信號之間的能量發(fā)生耦合。

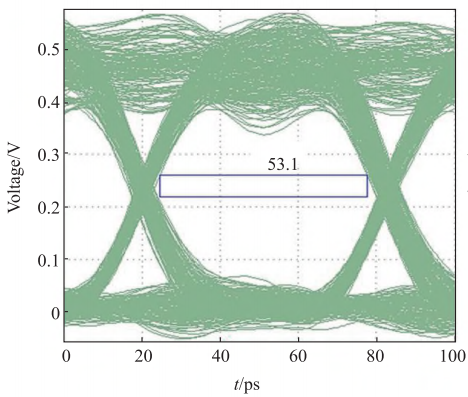

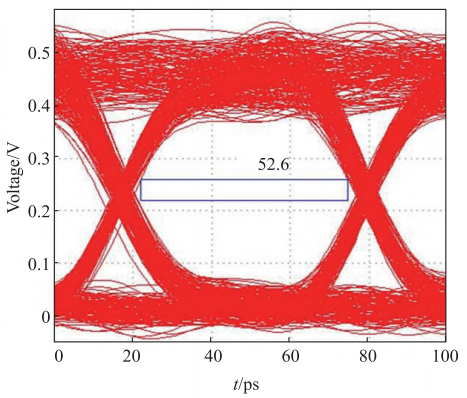

在長距離布線中,需要特別注意減小信號線之間的耦合強度,以降低潛在的串擾。得益于RX良好的端接匹配,兩種長度的互連線在9 mA的TX驅(qū)動下都能得到良好的信號質(zhì)量。圖7(c)(d)為近端Chiplet和遠端Chiplet的眼圖,近端Chiplet的眼寬為53.1 ps(0.85 UI),遠端Chiplet的眼寬為52.6 ps(0.84 UI),這說明線長差異導致的信號邊沿退化及串擾對眼圖抖動的影響有限。在缺少特定電源噪聲模型的情況下,本文未針對基板的同步開關(guān)噪聲進行建模或分析,但得益于有機基板的空間布局靈活性,信號通道在合理的端接配置下可以滿足UCIe的設(shè)計要求,這一結(jié)果有望為Chiplet應(yīng)用提供重要的設(shè)計和加工支持。

(a)近端Chiplet和遠端Chiplet的VTF損耗

(b)近端Chiplet和遠端Chiplet的VTF串擾

(c)近端Chiplet眼圖

(d)遠端Chiplet眼圖

圖7Chiplet集成模型的VTF損耗和眼圖

03

結(jié) 論

本文基于國內(nèi)有機基板工藝,完成了Chiplet的標準封裝布局設(shè)計,并對信號完整性進行了仿真分析。結(jié)果表明,該設(shè)計在單通道速率為32 GT/s的條件下,可實現(xiàn)每毫米240 GB/s的邊緣帶寬密度。同時,近端Chiplet和遠端Chiplet的VTF損耗與VTF串擾及眼寬均滿足UCIe的設(shè)計要求。本文對VTF指標的仿真方法進行了確認,并深入研究了國內(nèi)有機基板在Chiplet應(yīng)用方面的設(shè)計加工潛力,證明國內(nèi)有機基板在Chiplet應(yīng)用方面具有良好的前景,為推動Chiplet通用協(xié)議的國產(chǎn)應(yīng)用轉(zhuǎn)化提供了有價值的參考。有機基板的尺寸所導致的延遲和能效問題仍然是其相對短板,因此需要與上下游單位進行更深入的合作與探討,以尋求解決方案。

-

集成電路

+關(guān)注

關(guān)注

5420文章

12009瀏覽量

367757 -

摩爾定律

+關(guān)注

關(guān)注

4文章

638瀏覽量

79756 -

晶體管

+關(guān)注

關(guān)注

77文章

10003瀏覽量

141128 -

信號完整性

+關(guān)注

關(guān)注

68文章

1440瀏覽量

96585 -

chiplet

+關(guān)注

關(guān)注

6文章

453瀏覽量

12928

原文標題:?專題報道 | Chiplet封裝用有機基板的信號完整性設(shè)計

文章出處:【微信號:封裝與高速技術(shù)前沿,微信公眾號:封裝與高速技術(shù)前沿】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

信號完整性與電源完整性的仿真分析與設(shè)計

信號完整性與電源完整性的仿真

什么是信號完整性?

聽懂什么是信號完整性

Chiplet封裝用有機基板的信號完整性設(shè)計

Chiplet封裝用有機基板的信號完整性設(shè)計

評論