該文提出了一種寬帶鎖相環(huán)(PLL)構(gòu)建模塊集成電路(IC),該電路可以適應(yīng)0.5GHz至9GHz的信號(hào)頻率。該設(shè)計(jì)集成了具有可選分頻比的預(yù)分頻器、鑒相器、用于生產(chǎn)測(cè)試的壓控振蕩器以及相關(guān)電路。該芯片采用Maxim的GST-2雙極線性陣列技術(shù)設(shè)計(jì),采用16引腳塑料雙列直插式封裝。其結(jié)果是適用于各種PLL系統(tǒng)的低成本寬帶解決方案。

介紹

許多高速PLL設(shè)計(jì)的發(fā)展重點(diǎn)正在從研究演變?yōu)榻?jīng)濟(jì)挑戰(zhàn)。系統(tǒng)設(shè)計(jì)人員需要高度集成、具有價(jià)格競(jìng)爭(zhēng)力的解決方案。低成本解決方案通常需要使用廉價(jià)的塑料封裝,盡管它對(duì)高速性能有不利影響。更高的集成度導(dǎo)致更大的功耗,進(jìn)一步增加了與塑料封裝相關(guān)的挑戰(zhàn)。因此,本文描述的PLL構(gòu)建模塊的目標(biāo)是以低功耗實(shí)現(xiàn)寬帶性能,并使性能受封裝限制的影響最小。

設(shè)計(jì)

PLL構(gòu)建模塊IC可以適應(yīng)0.5GHz至9GHz的輸入信號(hào)頻率范圍,使其適用于大多數(shù)PLL應(yīng)用,如衛(wèi)星通信系統(tǒng)、高速測(cè)量設(shè)備和RF數(shù)據(jù)通信。該芯片采用硅雙極技術(shù)制造,NPN晶體管fT和 f.max分別等于 24GHz 和 22GHz。為了縮短上市時(shí)間,使用了線性陣列。線性陣列類似于門陣列,不同之處在于,線性陣列沒(méi)有預(yù)先放置用于數(shù)字功能的門,而是具有用于模擬設(shè)計(jì)的晶體管、電阻器和電容器等預(yù)置元件。使用線性陣列可以實(shí)現(xiàn)更快的周轉(zhuǎn)時(shí)間,但增加的布局寄生效應(yīng)和固定數(shù)量的元件和元件值可能會(huì)阻礙設(shè)計(jì)人員實(shí)現(xiàn)最佳設(shè)計(jì)。盡管存在這些潛在的限制,但寬帶性能仍然通過(guò)精心的布局和創(chuàng)造性設(shè)計(jì)來(lái)實(shí)現(xiàn),這些設(shè)計(jì)最有效地利用了可用組件。

芯片的框圖如圖1所示。芯片從0.5GHz至9GHz頻率范圍內(nèi)的外部源接收調(diào)制信號(hào)。信號(hào)通過(guò)片內(nèi)鑒相器和片外環(huán)路濾波器鎖相至外部RF輸入。預(yù)分頻器分為兩部分:八分頻塊和八分/九分頻塊。VCO、電荷泵和環(huán)路濾波器省略在片外,因此該構(gòu)建模塊可用于各種系統(tǒng)應(yīng)用。

圖1.PLL構(gòu)建模塊和完整的PLL電路。

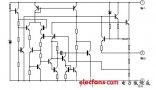

八分頻中的觸發(fā)器采用主/從配置,Q-bar輸出反饋到數(shù)據(jù)輸入,使時(shí)鐘頻率分頻2倍。八分頻鏈中第一個(gè)觸發(fā)器的示意圖如圖2所示。第一個(gè)觸發(fā)器的一個(gè)特點(diǎn)是包含稱為“保活”電流的電流,記作IK在原理圖中。保活電流縮短了完全切換 Q 的時(shí)間9- Q16通過(guò)防止晶體管關(guān)閉。值約為主差分對(duì)電流的 1/10 (ID)的使用。所有八個(gè)發(fā)射器跟隨器(Q1- Q8) 對(duì)于八分頻中的第一個(gè)觸發(fā)器是必需的,因?yàn)榘l(fā)射極跟隨器的低輸出阻抗和高電流驅(qū)動(dòng)能力提高了切換速率。對(duì)于不考慮速度的后續(xù)階段,消除(或減少數(shù)量)發(fā)射極跟隨器,并降低差分對(duì)電流以最大限度地降低功耗。

圖2.除以八鏈中第一個(gè)觸發(fā)器的示意圖。

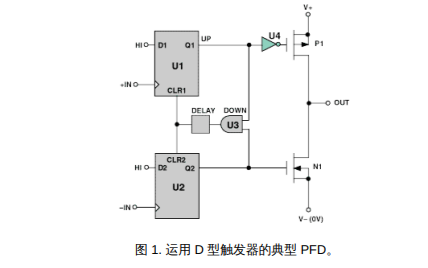

這項(xiàng)工作中的鑒相器基于標(biāo)準(zhǔn)設(shè)計(jì)。鑒相器的框圖如圖3所示。鑒相器有三個(gè)輸出:UP、DWN 和 LD。當(dāng)環(huán)路失鎖時(shí),UP或DWN輸出上會(huì)出現(xiàn)不規(guī)則的脈沖序列,具體取決于輸入信號(hào)頻率是比參考頻率快還是慢。另一個(gè)信號(hào)的濾波輸出保持高電平。如果信號(hào)頻率和參考頻率相等,則輸出脈沖序列是周期性的,平均值是相位偏移的量度。

圖3.鑒相器框圖。

開(kāi)發(fā)低成本的PLL構(gòu)建模塊“高速”測(cè)試是其生產(chǎn)成功的關(guān)鍵。包括一個(gè)片內(nèi)高頻(~5GHz)環(huán)形振蕩器。振蕩器的目的是提供一種在近速晶圓或封裝測(cè)試期間測(cè)試分頻器的方法。VCO是一種環(huán)形振蕩器,它使用插值來(lái)增加頻率響應(yīng)[1]。振蕩器通過(guò)外部“使能”引腳單獨(dú)供電,該引腳在接地時(shí)禁用其工作,并在連接到電源時(shí)允許工作。二分頻電路用于將測(cè)試輸出信號(hào)降低到與低速晶圓測(cè)試和芯片分選兼容的頻率。

包裝

PLL構(gòu)建模塊IC要在高頻下成功運(yùn)行,需要仔細(xì)重新設(shè)計(jì)塑料封裝,如圖4所示。需要絕對(duì)最小化接地電感,以實(shí)現(xiàn)良好的相位噪聲響應(yīng)。高頻預(yù)分頻器輸入(VRF)需要與鑒相器輸入(REFIN)很好地隔離。SOIC 封裝上的 16 個(gè)引腳中有 6 個(gè)是接地引腳,它們與焊盤(pán)短路。重新加工為要連接的芯片接地和芯片基板提供了一個(gè)相對(duì)“干凈”的接地點(diǎn)。用四個(gè)接地引腳(每側(cè)兩個(gè))包圍高頻輸入信號(hào),改善了輸入信號(hào)的隔離。此外,重新加工封裝有助于顯著改善熱阻。封裝的Φja從~100°C/W降低到72°C/W,芯片在所有情況下的最高結(jié)溫都不會(huì)超過(guò)125°C。

圖4.包裝圖紙。

基于封裝的物理特性,建立了集總參數(shù)封裝模型。圖 5 顯示了該模型,其中包含用于仿真的特定參數(shù)值。(給出的值適用于最短引線長(zhǎng)度。高頻輸入信號(hào)放置在封裝的中心,以最大限度地減少焊線和引線電感,從而降低耦合并改善匹配。

圖5.封裝模型。

測(cè)量結(jié)果

封裝PLL構(gòu)建模塊的最小可檢測(cè)輸入信號(hào)與輸入頻率的關(guān)系如圖6所示。-20dBm或更小的輸入信號(hào)足以在很寬的頻率范圍內(nèi)工作。該設(shè)計(jì)的工作頻率范圍為 0.5GHz 至 9GHz,但在頻率邊界下需要稍大的輸入功率電平。封裝芯片的測(cè)量是在-35°C至+90°C的溫度范圍內(nèi)進(jìn)行的。在較低溫度下,PLL構(gòu)建模塊在給定輸入信號(hào)電平下以較高的速度工作,因?yàn)榫w管T隨著結(jié)溫的降低而增加。仿真結(jié)果預(yù)測(cè)了溫度對(duì)性能的影響。在每個(gè)溫度下,電源在4.5V至5.5V范圍內(nèi)變化。圖6中的數(shù)據(jù)表明,電路的性能與電源電壓相對(duì)無(wú)關(guān)。

圖6.封裝器件在各種電源電壓和溫度下的分壓器靈敏度。

還使用膜探頭測(cè)量了未封裝芯片的分壓器靈敏度。圖7所示兩條曲線的相似性顯示了封裝的寬帶性能。高達(dá)9GHz的晶圓和封裝測(cè)量之間幾乎沒(méi)有區(qū)別。

圖7.分壓器靈敏度:標(biāo)稱條件下封裝和晶圓探針數(shù)據(jù)的比較。(T = 25°C, V抄送= 11V)

驅(qū)動(dòng)分壓器的輸入緩沖器設(shè)計(jì)為與50Ω阻抗相匹配。S的測(cè)量結(jié)果11圖8所示可以通過(guò)了解輸入緩沖器拓?fù)鋪?lái)解釋。阻抗匹配通過(guò)連接在輸入和偏置電壓之間的50Ω內(nèi)部電阻來(lái)實(shí)現(xiàn)。在非常低的頻率下,偏置電路的阻抗會(huì)增加輸入阻抗。偏置節(jié)點(diǎn)處的電容會(huì)隨著頻率的增加而降低偏置電路的阻抗。在中頻帶實(shí)現(xiàn)良好的匹配。在高頻下,封裝和布局寄生效應(yīng)開(kāi)始降低輸入阻抗。顯示的數(shù)據(jù)還反映了SMA連接器的阻抗,這進(jìn)一步降低了高頻下的性能。優(yōu)于 -5dB 的 S11可以在整個(gè)工作頻率頻帶上實(shí)現(xiàn),這足以滿足大多數(shù)閉環(huán)應(yīng)用的需求。

圖8.封裝PLL構(gòu)建模塊的輸入阻抗。

用于測(cè)試目的的片內(nèi)振蕩器的振蕩頻率約為5GHz。該設(shè)計(jì)沒(méi)有針對(duì)速度進(jìn)行優(yōu)化,并且通過(guò)這種設(shè)計(jì)可以實(shí)現(xiàn)更高的頻率。在100kHz失調(diào)頻率下,測(cè)得的相位噪聲為-69dBc/Hz。

鑒相器在分壓器的整個(gè)范圍內(nèi)正常工作。輸出為帶外部負(fù)載的集電極開(kāi)路。對(duì)于150Ω負(fù)載,UP和DWN引腳上的輸出電壓為1.1V。LD輸出在負(fù)載500Ω電阻時(shí)可實(shí)現(xiàn)2V擺幅。所需的最小基準(zhǔn)輸入信號(hào)為-18dBm (匹配至50Ω),可承受高達(dá)+10dBm的電壓。

電路芯片尺寸為 70 mil x 75 mil。大約 85% 的線性陣列用于 PLL 構(gòu)建模塊的設(shè)計(jì)。標(biāo)稱條件下的功耗(T = 25°C 和 V抄送= 5V)約為500mW。

結(jié)論

本文描述的設(shè)計(jì)是一個(gè)寬帶PLL構(gòu)建模塊,能夠適應(yīng)0.5GHz至9GHz的信號(hào)頻率。制造的零件體現(xiàn)了低成本、快速上市的設(shè)計(jì),同時(shí)又不犧牲性能。該芯片通過(guò)有效的封裝建模、內(nèi)置測(cè)試和重新加工,克服了與廉價(jià)封裝相關(guān)的設(shè)計(jì)問(wèn)題。

審核編輯:郭婷

-

集成電路

+關(guān)注

關(guān)注

5415文章

11865瀏覽量

366238 -

濾波器

+關(guān)注

關(guān)注

162文章

8010瀏覽量

180466 -

pll

+關(guān)注

關(guān)注

6文章

878瀏覽量

135893

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

集成電路的分類

雙向可控硅調(diào)壓電路的擦字集成電路

X78XX:雙極型線性集成電路中文資料簡(jiǎn)介

使用LT1567雙放大器構(gòu)建模塊設(shè)計(jì)低噪聲差分電路

TTL集成電路與CMOS集成電路元件比較

什么是集成電路?

什么是雙極型集成電路

PLL頻率合成器的主要構(gòu)建模塊詳細(xì)資料說(shuō)明

硅光電子集成電路與CMOS器件的集成有較大的市場(chǎng)需求

集成電路制造工藝有哪幾種?

硅集成電路技術(shù)的優(yōu)勢(shì)與挑戰(zhàn)

利用硅雙極寬帶PLL構(gòu)建模塊集成電路

利用硅雙極寬帶PLL構(gòu)建模塊集成電路

評(píng)論