本文翻譯轉載于 Cadence blog

作者:Anika Sunda

功能驗證占用了目前 SoC 設計投入勞動的 70% 以上。然而,即使在驗證上投入如此之大,流片時出現功能失效的風險卻比以往任何時候都要高。其主要原因是,設計團隊不知道功能正確性與流片目標的距離。SoC 驗證時的覆蓋收斂就像是追逐海市蜃樓。

實現真正的功能驗證收斂從而充滿信心地完成流片,看似天方夜譚。做出流片決定只能取決于當時的判斷。有經驗的工程師會基于驗證完整性指標、發現的功能性錯誤的占比和復雜性等因素,來判斷是否達到足夠的收斂水平和信心。

所有運行了無數夜間回歸測試的驗證工程師,都希望可以更快地實現覆蓋目標,尋找到一種即插即用的解決方案,一種自動化的方法,用最少的資源更快地實現覆蓋率收斂。

Xcelium 機器學習 App 從以前的回歸運行中學習,并引導 Xcelium 隨機化內核,幫助縮短回歸時間,以顯著縮短的仿真周期更快地實現覆蓋率收斂,在特定的感興趣的覆蓋點周圍捕獲更多漏洞。

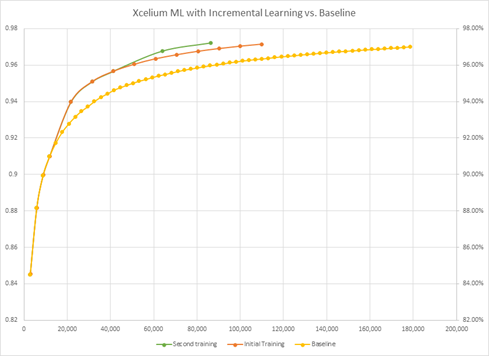

下圖是機器學習 App 在某頭部半導體公司的成功應用案例。可以看到,機器學習(ML)回歸比基準運行快了大約 1.4 倍(機器學習(ML)在 ~62k 次運行時達到 96%,基準運行在約 80k 次運行后才達到相同水平)。

這個數據意味著,過去耗時 2 個月的收斂周期縮短了 2- 3 周左右。很明顯,機器學習(ML)讓回歸運行更加高效,幫助用戶更快實現覆蓋率收斂的目標。

Cadence楷登

-

soc

+關注

關注

38文章

4356瀏覽量

221864 -

Cadence

+關注

關注

67文章

966瀏覽量

143926 -

APP

+關注

關注

33文章

1585瀏覽量

73874 -

機器學習

+關注

關注

66文章

8493瀏覽量

134179 -

Xcelium

+關注

關注

1文章

5瀏覽量

5955

原文標題:還在為覆蓋率收斂而掙扎?Xcelium 機器學習 App 為驗證插上翅膀

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

新思科技VSO.ai如何顛覆芯片驗證

秒驗:重構APP用戶體驗與運營效率

聲智APP暢享多元模型體驗

如何優化BP神經網絡的學習率

英諾達發布全新靜態驗證產品,提升芯片設計效率

NPU與機器學習算法的關系

synopsys 的design ware:DW_fpv_div,浮點數除法器,默認32位下,想提升覆蓋率(TMAX),如果用功能case去提升覆蓋率呢?

利用靜態檢查工具完善功能安全中測試覆蓋率

【「時間序列與機器學習」閱讀體驗】+ 簡單建議

信達生物利用AI技術為藥物研發插上翅膀

機器學習中的交叉驗證方法

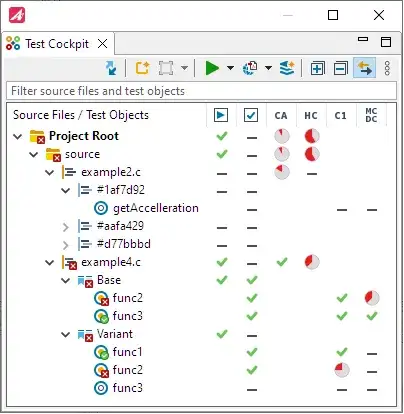

單元測試工具TESSY 新版本亮點速覽:提供測試駕駛艙視圖、超級覆蓋率、代碼訪問分析、增強覆蓋率審查

還在為覆蓋率收斂而掙扎?Xcelium機器學習App為驗證插上翅膀

還在為覆蓋率收斂而掙扎?Xcelium機器學習App為驗證插上翅膀

評論