隨著半導(dǎo)體工藝的不斷發(fā)展,器件特征尺寸逐漸減少,激發(fā)單粒子翻轉(zhuǎn)(Single Event Upset, SEU)效應(yīng)所需的能量閾值呈幾何級(jí)下降趨勢(shì)。例如,65 nm工藝下器件發(fā)生電平翻轉(zhuǎn)需6500個(gè)電荷,16 nm工藝下器件電平翻轉(zhuǎn)僅需1000個(gè)電荷 。

雖然電平錯(cuò)誤翻轉(zhuǎn)引發(fā)的軟錯(cuò)誤不會(huì)對(duì)電路造成永久性的破壞,但是由于發(fā)生的能量閾值較低,所以在所有單粒子效應(yīng)造成集成電路工作失效的事件中,電平錯(cuò)誤翻轉(zhuǎn)效應(yīng)引起的事件占有比例最高,為40%。

由此可見(jiàn),軟錯(cuò)誤已經(jīng)成為先進(jìn)工藝下大規(guī)模數(shù)字集成電路在輻射環(huán)境中最為主要的失效模式,這極大地限制了集成電路在一些可靠性較高的領(lǐng)域尤其是富含高通量低能粒子的航天航空?qǐng)鼍爸械膽?yīng)用。為促進(jìn)航空航天事業(yè)的快速發(fā)展,需要對(duì)集成電路功能軟錯(cuò)誤的敏感性進(jìn)行充分的研究和評(píng)估。

在所有的評(píng)估手段中,空間環(huán)境實(shí)測(cè)的方式獲得的數(shù)據(jù)最為準(zhǔn)確,但航天器的發(fā)射次數(shù)和載荷都是有限的,實(shí)驗(yàn)機(jī)會(huì)少且價(jià)格昂貴。因此,更多的評(píng)估手段被開(kāi)發(fā)出來(lái),主要有輻照測(cè)試,軟件仿真和現(xiàn)場(chǎng)可編程門(mén)陣列(Field Programmable Gate Array, FPGA)模擬等技術(shù)路線 。

輻照測(cè)試可以精確控制輻射強(qiáng)度和時(shí)間,相比空間試驗(yàn)有著良好的可控性和靈活性。但是搭建輻照測(cè)試環(huán)境的開(kāi)銷(xiāo)依然非常龐大,具備輻照測(cè)試條件的單位也極少。此外,輻照測(cè)試需要批量測(cè)試,在測(cè)試過(guò)程中也極可能損傷芯片,且芯片出錯(cuò)后也很難定位敏感節(jié)點(diǎn),故一般只用于成品芯片的性能測(cè)試和最終測(cè)試。

軟件仿真通過(guò)數(shù)學(xué)分析方法,將真實(shí)情況下單粒子效應(yīng)對(duì)電路造成的影響轉(zhuǎn)化為故障產(chǎn)生概率,故障持續(xù)時(shí)間和故障節(jié)點(diǎn)位置等故障模型參數(shù),最后將故障注入到電路中 。

軟件仿真的優(yōu)勢(shì)在于模擬單粒子效應(yīng)的靈活性,可從工藝級(jí)、器件級(jí)、晶體管級(jí)、門(mén)級(jí)和行為級(jí)各個(gè)層次對(duì)單粒子效應(yīng)進(jìn)行建模、仿真和分析。但隨著電路規(guī)模的增加,軟件仿真計(jì)算過(guò)程的時(shí)間開(kāi)銷(xiāo)也在顯著增加,諸如開(kāi)關(guān)級(jí)模擬的時(shí)間爆炸問(wèn)題 。

相對(duì)于軟件仿真技術(shù),F(xiàn)PGA模擬單粒子翻轉(zhuǎn)效應(yīng)的實(shí)現(xiàn)成本更低,評(píng)估速度更快,更適合用于快速評(píng)估集成電路對(duì)單粒子翻轉(zhuǎn)效應(yīng)的敏感程度。具體實(shí)現(xiàn)方式主要有FPGA重配置注入故障,掃描鏈注入故障和旁路電路注入故障3種。

FPGA重配置注入故障是基于FPGA的重配置功能,在運(yùn)行過(guò)程中,動(dòng)態(tài)修改FPGA的配置信息以實(shí)現(xiàn)注入故障。掃描鏈注入故障是復(fù)用可測(cè)性設(shè)計(jì)的掃描鏈結(jié)構(gòu),將故障寫(xiě)至掃描鏈的入口,控制掃描鏈的數(shù)據(jù)進(jìn)行串行移動(dòng),將故障準(zhǔn)確寫(xiě)入待評(píng)估的寄存器中。旁路電路注入故障的實(shí)現(xiàn)原理和掃描鏈注入故障的實(shí)現(xiàn)原理類似,也是在原有的電路結(jié)構(gòu)上添加附加電路,然后對(duì)電路注入故障以模擬單粒子翻轉(zhuǎn)效應(yīng),但是消除了掃描鏈注入故障速度慢的缺點(diǎn)。

FPGA重配置注入故障、掃描鏈注入故障和旁路電路注入故障由于實(shí)現(xiàn)方式不一樣,在評(píng)估速度、敏感點(diǎn)定位精度和使用電路規(guī)模等性能上也各有優(yōu)劣。本文總結(jié)了FPGA重配置注入故障技術(shù),討論了掃描鏈注入故障技術(shù),描述了旁路電路注入故障技術(shù),對(duì)比了3種注入故障技術(shù)并對(duì)各類技術(shù)的發(fā)展方向進(jìn)行了展望。

2

** FPGA重配置注入故障**

FPGA的配置信息包含了各類邏輯資源的配置狀況、電壓標(biāo)準(zhǔn)、連線情況和用戶設(shè)計(jì)的使用情況 ^[14]^ 。借助配置控制指令,即可通過(guò)專用的配置讀寫(xiě)接口(Internal Configuration Access Port,ICAP)訪問(wèn)FPGA的配置信息 ^[15]^ ;同時(shí)也能將其中某一位數(shù)據(jù)進(jìn)行翻轉(zhuǎn)(如0到1或1到0),再把修改后的配置信息寫(xiě)回FPGA以實(shí)現(xiàn)故障注入;最后持續(xù)讀取配置信息還可監(jiān)控故障注入后對(duì)電路造成的影響。

基于重配置的故障注入流程如圖1所示,按照配置范圍的大小,F(xiàn)PGA重配置技術(shù)可以進(jìn)一步分為全局重配置和部分重配置 ^[16-17]^ 。全局重配置對(duì)整個(gè)FPGA芯片進(jìn)行重新配置。在配置過(guò)程中,F(xiàn)PGA由于原始配置信息被清除而處于非正常工作狀態(tài),直到配置信息重新完整寫(xiě)入,F(xiàn)PGA才能正確工作。因此,從時(shí)間軸上看,F(xiàn)PGA工作是不連續(xù)的。全局重配置的優(yōu)勢(shì)在于配置過(guò)程的實(shí)現(xiàn)十分簡(jiǎn)單,不需要分析待測(cè)電路所使用的硬件資源,同時(shí)其電路評(píng)估速度比軟件仿真要快幾個(gè)數(shù)量級(jí)。

全局重配置的方式也存在重大缺陷,由于每次故障注入時(shí)都需要重新配置全部信息,會(huì)引入一定的時(shí)間開(kāi)銷(xiāo),而且時(shí)間開(kāi)銷(xiāo)和配置信息的大小成正比。以Xilinx Zynq 7020為例,配置文件的大小為32.5 Mbit,在工作頻率為100 MHz時(shí),單次配置全部配置信息所需時(shí)間為32 ms ;如果對(duì)32.5 Mbit里每個(gè)比特位均進(jìn)行一次故障注入測(cè)試,總計(jì)時(shí)間為284 h。

部分重配置則克服了以上缺陷,可選擇部分配置信息進(jìn)行重配置,未重配置的電路不受影響,對(duì)應(yīng)的功能仍然可以正常運(yùn)作。由于部分重配置大幅減少了讀寫(xiě)的配置信息,可顯著縮短重配置時(shí)間。

文獻(xiàn)[19]使用Xilinx Virtex系列FPGA作為測(cè)試平臺(tái),當(dāng)以全局重配置模式對(duì)電路注入故障時(shí),完成單次配置需要169.738 ms。而如果只修改和待測(cè)電路相關(guān)的8 frame配置信息,僅需0.424 ms。此外,對(duì)于FPGA設(shè)計(jì)的電路,F(xiàn)PGA的利用率一般不會(huì)達(dá)到100%,未使用的空閑配置位無(wú)需被注入故障,這可以進(jìn)一步減少時(shí)間開(kāi)銷(xiāo) ^[20]^ 。

基于重配置的故障注入技術(shù)的主要優(yōu)勢(shì)是基于FPGA的內(nèi)部功能實(shí)現(xiàn),因此不會(huì)對(duì)待測(cè)電路造成影響,不會(huì)產(chǎn)生額外的硬件資源開(kāi)銷(xiāo),實(shí)現(xiàn)成本極低,可適用于大規(guī)模電路,且電路評(píng)估速度也較為理想。但也存在不足之處,主要體現(xiàn)在3個(gè)方面。

其一是待評(píng)估的FPGA必須具備重配置功能,限制了FPGA硬件的選擇范圍。其二是每次執(zhí)行故障注入時(shí),需要訪問(wèn)、修改和重寫(xiě)配置信息,使得上位機(jī)和待評(píng)估FPGA之間會(huì)進(jìn)行大量的數(shù)據(jù)交互,相對(duì)于FPGA電路的運(yùn)行時(shí)間,交互過(guò)程產(chǎn)生的時(shí)間開(kāi)銷(xiāo)要高的多。以Xilinx Virtex系列FPGA為例,理論上配置全部比特位所需時(shí)間為9.9 ms,但實(shí)際通過(guò)計(jì)算機(jī)并口傳輸配置數(shù)據(jù)的過(guò)程需要20 s 。

部分重配置減少了信息交互的數(shù)據(jù)量,提高了評(píng)估效率,但整體測(cè)試的時(shí)間開(kāi)銷(xiāo)中數(shù)據(jù)交互過(guò)程仍占有較大比例。其三是主流FPGA的配置信息是加密的,雖然FPGA重配置技術(shù)能夠在電路中注入故障,但是電路出現(xiàn)故障后,由于無(wú)法解析主流FPGA的配置信息,所以很難定位到具體的電路節(jié)點(diǎn),給加固設(shè)計(jì)帶來(lái)了困難。

3

掃描鏈注入故障

掃描鏈源于可測(cè)性設(shè)計(jì)。在可測(cè)性設(shè)計(jì)中,首先將寄存器替換為掃描寄存器,然后將多個(gè)掃描寄存器相連以形成掃描鏈結(jié)構(gòu),最后以移位寄存器的工作方式將測(cè)試激勵(lì)寫(xiě)入掃描鏈的首端,或者將測(cè)試響應(yīng)從掃描鏈的末端讀出 。

可視作在普通寄存器結(jié)構(gòu)上添加了一個(gè)2選1數(shù)據(jù)選擇器。掃描寄存器有兩個(gè)工作模式,工作模式的切換由信號(hào)Scan_en決定。當(dāng)Scan_en不使能時(shí),掃描寄存器為正常工作模式,此時(shí)功能等同于常規(guī)的D寄存器,采樣輸入端D的電平并輸出。當(dāng)Scan_en使能時(shí),寄存器切換為掃描模式,此時(shí)可通過(guò)Scan_in輸入故障數(shù)據(jù)以模擬單粒子翻轉(zhuǎn)效應(yīng) 。

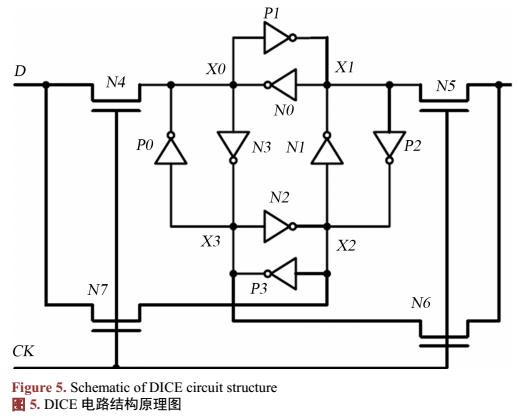

將當(dāng)前掃描寄存器的輸出端Q和下一級(jí)掃描寄存器輸入端Scan_in連接起來(lái),就構(gòu)成了掃描鏈。掃描鏈結(jié)構(gòu)如圖3所示,基于掃描寄存器的結(jié)構(gòu)和工作原理可推導(dǎo)出,Scan_en不使能時(shí),電路正常工作。Scan_en使能時(shí),可以通過(guò)移位將故障數(shù)據(jù)串行輸入到任意寄存器的Scan_in端,最終實(shí)現(xiàn)對(duì)任意寄存器注入故障以模擬單粒子翻轉(zhuǎn)效應(yīng)。

在實(shí)現(xiàn)掃描鏈注入故障電路時(shí),掃描鏈的結(jié)構(gòu)不是固定的,不同的掃描鏈電路產(chǎn)生的資源開(kāi)銷(xiāo)和故障注入速度也不同。文獻(xiàn)[23]設(shè)計(jì)了3種不同的掃描鏈電路來(lái)實(shí)現(xiàn)故障注入,其中開(kāi)銷(xiāo)最大的電路和開(kāi)銷(xiāo)最小的電路資源開(kāi)銷(xiāo)相差近3倍,但單次故障注入時(shí)間減少了數(shù)微秒,雖然速度區(qū)別不大,但在大規(guī)模電路測(cè)試中能節(jié)約的時(shí)間開(kāi)銷(xiāo)極為可觀。因此測(cè)試人員可根據(jù)測(cè)試平臺(tái)提供資源(寄存器和數(shù)據(jù)選擇器等)的大小和實(shí)際可達(dá)到的注入速度權(quán)衡使用合適的掃描鏈電路。

掃描鏈技術(shù)的優(yōu)勢(shì)在于可適用于任意規(guī)模電路的測(cè)試,也可用于ASIC電路的評(píng)估,同時(shí)不受FPGA測(cè)試平臺(tái)的限制。故障注入速度最快可達(dá)到微秒級(jí)別,相對(duì)于重配置技術(shù)有了進(jìn)一步的提高。由于掃描鏈的插入對(duì)象可以是任意觸發(fā)器,因此故障注入后電路敏感節(jié)點(diǎn)的定位精度也較高。其最主要的缺陷是會(huì)產(chǎn)生額外的資源開(kāi)銷(xiāo),且額外開(kāi)銷(xiāo)會(huì)隨著電路規(guī)模的增大而增加。此外,為了能夠正確定位電路對(duì)單粒子翻轉(zhuǎn)效應(yīng)的敏感區(qū)域,串行移位時(shí)鐘的頻率還不能較高,這樣使得掃描鏈串行移位的時(shí)間開(kāi)銷(xiāo)顯得頗為可觀,需要在掃描鏈長(zhǎng)度和評(píng)估速度上做出折衷。

最后,值得指出的是,掃描鏈技術(shù)在故障數(shù)據(jù)傳輸過(guò)程中存在和重配置技術(shù)一樣的問(wèn)題。文獻(xiàn)[24]中提到所設(shè)計(jì)掃描鏈的單次故障注入速度為1 μs左右,但受串口傳輸?shù)南拗疲看喂收霞?lì)數(shù)據(jù)的下發(fā)需要3.84 ms,因此接口的傳輸速率成為制約速度的主要因素。文獻(xiàn)[22]中每次注入故障時(shí)需要主機(jī)和FPGA進(jìn)行故障數(shù)據(jù)交互過(guò)程,頻繁地通信導(dǎo)致故障注入速度偏慢。文獻(xiàn)[23]針對(duì)數(shù)據(jù)通信過(guò)程進(jìn)行了優(yōu)化,將測(cè)試電路所需的故障激勵(lì)數(shù)據(jù)一次性全部發(fā)送到FPGA的存儲(chǔ)區(qū),隨后FPGA內(nèi)部自動(dòng)執(zhí)行全部測(cè)試過(guò)程,主機(jī)和FPGA只需在起始階段通信一次,減小了數(shù)據(jù)通信的時(shí)間開(kāi)銷(xiāo),故障注入速度相對(duì)于文獻(xiàn)[22]提高了2個(gè)數(shù)量級(jí)。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614639 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28669瀏覽量

233441 -

電平

+關(guān)注

關(guān)注

5文章

367瀏覽量

40439 -

器件

+關(guān)注

關(guān)注

4文章

334瀏覽量

28278

發(fā)布評(píng)論請(qǐng)先 登錄

單粒子翻轉(zhuǎn)引起SRAM型FPGA的故障機(jī)理闡述

理解FPGA中的單粒子翻轉(zhuǎn)

用SOI技術(shù)提高CMOSSRAM的抗單粒子翻轉(zhuǎn)能力

特征工藝尺寸對(duì)CMOS SRAM抗單粒子翻轉(zhuǎn)性能的影響

高速ADC的單粒子閂鎖和瞬態(tài)

如何對(duì)ADC、DAC、PLL進(jìn)行單粒子翻轉(zhuǎn)容錯(cuò)設(shè)計(jì)

隨機(jī)靜態(tài)存儲(chǔ)器低能中子單粒子翻轉(zhuǎn)效應(yīng)

ARINC659總線的單粒子翻轉(zhuǎn)識(shí)別

功率MOS器件單粒子柵穿效應(yīng)的PSPICE模擬

在芯片設(shè)計(jì)階段如何防護(hù)“單粒子翻轉(zhuǎn)”

有效容忍單粒子多點(diǎn)翻轉(zhuǎn)的加固鎖存器

航空電子設(shè)計(jì)之“單粒子翻轉(zhuǎn)”問(wèn)題

單粒子翻轉(zhuǎn)效應(yīng)的FPGA模擬技術(shù) (下)

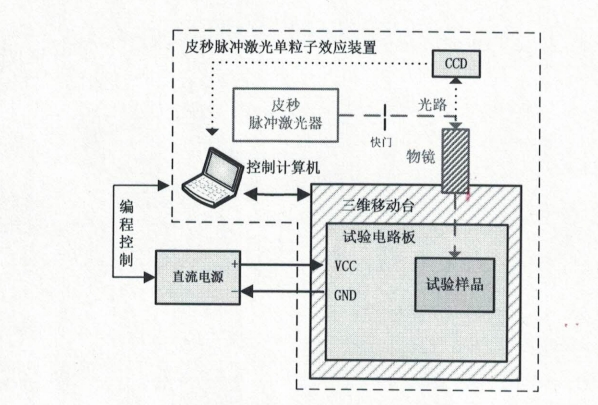

皮秒脈沖激光技術(shù)在AS32S601單粒子效應(yīng)評(píng)估中的應(yīng)用

單粒子翻轉(zhuǎn)效應(yīng)的FPGA模擬技術(shù) (上)

單粒子翻轉(zhuǎn)效應(yīng)的FPGA模擬技術(shù) (上)

評(píng)論