在具有一個主站和多個從站的典型SPI系統中,專用的片選信號用于尋址單個從站。隨著從站數量的增加,芯片選擇線路的數量也會增加。在這種情況下,系統的電路板布局可能會成為一個相當大的挑戰。

一種布局替代方案是菊花鏈。本文解釋了菊花鏈SPI系統的細節,并展示了如何使用軟件通過一串從站傳播命令。

標準SPI?/QSPI/? MICROWIRE?兼容微控制器通過3線或4線串行接口與其從器件通信。典型接口包括片選信號(/CS)、串行時鐘(SCLK)、數據輸入信號(DIN),偶爾還包括數據輸出信號(DOUT)。與I2C系統中通常一樣,可單獨尋址的設備與總線上的單個設備輕松通信。

基本串行通信接口

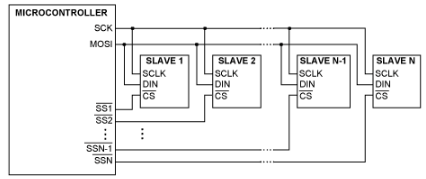

許多SPI器件無法單獨尋址。因此,這些設備與總線上的單個設備之間的通信需要額外的硬件或軟件組織。圖1顯示了一個微控制器與多個從設備通信的系統。

圖1.具有獨立芯片的微控制器為多個從設備選擇。

在上述系統中,微控制器使用一個串行時鐘輸出(SCK)和一個主輸出/從輸入線路(MOSI)來命令所有從機。微控制器為每個從設備分配一個獨立的從機選擇信號(/SS_),以便可以單獨對它們進行尋址。由于所有從機共享單個時鐘和數據線,因此只有/CS輸入置位為低電平的從機才會確認并響應串行時鐘和數據線上的活動。當系統中的從設備很少時,該系統易于實現。在具有許多從器件的系統中,微控制器需要的/SS_輸出與從器件數量一樣多。此體系結構增加了硬件和布局的復雜性。

菊花鏈替代品

硬件約束會使圖 1 中的方法變得不切實際且難以實現。串行接口應用的另一種方法是菊花鏈,它通過串聯的設備傳播命令。圖 2 顯示了采用菊花鏈配置的 N 器件系統。

圖2.具有多個菊花鏈從器件的微控制器。

單個/SS(或/CS)信號控制所有從機的/CS輸入;所有從站接收相同的時鐘信號。只有鏈中的第一個從站(SLAVE 1)直接從微控制器接收命令數據。網絡中每隔一個從站從鏈中前一個從站的DOUT輸出接收其DIN數據。

為了使菊花鏈成功工作,從機必須能夠在給定的命令周期內在DIN上輸入命令(由一個命令中時鐘所需的時鐘脈沖數定義),并在隨后的命令周期內在DOUT上輸出相同的命令。簡單地說,有一個命令周期的 DIN 到 DOUT 延遲。此外,從機必須只執行在/CS的上升沿寫入它的命令。這意味著只要/CS保持低電平,從機就會忽略該命令,并在下一個命令周期的DOUT上輸出該命令。如果/CS在給定的命令周期后變為高電平,則所有從站執行剛剛寫入其各自DIN輸入的命令。如果/CS變為高電平,則數據不會在DOUT輸出。此過程使鏈中的每個從站都可以執行不同的命令。只要滿足這些菊花鏈要求,微控制器只需要三個信號(/SS、SCK和MOSI)來控制網絡中的所有從站。

菊花鏈是如何實現的

在菊花鏈系統中(圖 2),SLAVE 1 直接從微控制器接收數據。該數據被時鐘輸入SLAVE 1的內部移位寄存器。只要/CS(或/SS)保持低電平,該數據就會傳播到SLAVE 1的DOUT輸出。SLAVE 1 的 DOUT 進入 SLAVE 2 的 DIN,因此當數據出現在 SLAVE 2 的 DOUT 輸出上時,數據將時鐘輸入 SLAVE 1 的內部移位寄存器。正如SLAVE 2從SLAVE 1接收數據一樣,微控制器可以同時向SLAVE 1發送另一個命令。此新命令將覆蓋 SLAVE 1 的移位寄存器中的先前數據。只要/CS保持低電平,數據就會在整個菊花鏈中傳播,直到每個從設備收到適當的命令。加載到每個從站移位寄存器的命令在/CS的上升沿執行。以下示例使用MAX5233和MAX5290演示菊花鏈。

示例電路 #1

圖3所示為三個MAX5233 IC,采用菊花鏈結構連接。MAX5233為雙通道、10位DAC(包含兩個DAC通道A和B)。RSTV 連接到 VDD,模擬輸出功率可達中間電平。

圖3.菊花鏈電路 #1。

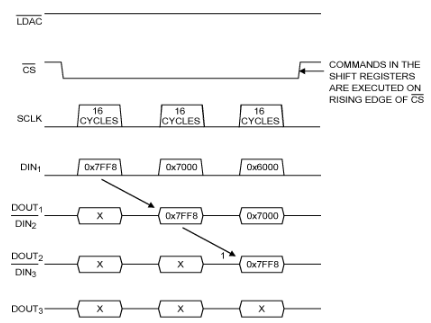

圖4顯示了將IC1(A1和B1)、IC2(A2和B2)和IC3(A3和B3)輸出分別設置為零、中和滿量程的命令序列。對于此示例,使用以下命令:

0x7FF8—用滿量程數據加載IC3 DAC寄存器,并將兩個輸出(A3、B3)設置為滿量程

0x7000—用中間電平數據加載IC2 DAC寄存器,并將兩個輸出(A2、B2)設置為中間電平

0x6000—用零電平數據加載IC1 DAC寄存器,并將兩個輸出(A1、B1)設置為零電平

圖4.電路 #1 — 命令序列 A。

在第一個命令周期(一組16個SCLK脈沖)中,0x7FF8被加載到IC1的移位寄存器中。當/CS保持低電平時,該數據通過IC1傳播,并在DOUT輸出1在下一個命令周期中。在第二個命令周期中,來自 DOUT 的數據1直接移動到 DIN2,0x7FF8被加載到IC2的移位寄存器中。同時,一個新命令0x7000被加載到IC1的移位寄存器中,從而覆蓋其先前的命令。

在第三個命令周期中,第一個命令0x7FF8加載到IC3的移位寄存器中。第二個命令 0x7000 加載到 IC2 中,IC1 接收新命令 0x6000。所有三個IC現在都有一個命令,它們通過移位寄存器中的菊花鏈接收該命令。當/CS變為高電平時,加載的命令將執行;A1 和 B1 設置為零電平,A2 和 B2 設置為中間電平,A3 和 B3 設置為滿量程。

圖 5 演示了一個更復雜的命令序列。使用以下命令(更多信息參見MAX5233數據資料):

0x3FF8—加載輸入寄存器A,滿量程數據,DAC寄存器和輸出保持不變

0x3000—加載具有中間量程數據的輸入寄存器A,DAC寄存器和輸出保持不變

0x2000—加載輸入寄存器A,具有零電平數據,DAC寄存器和輸出保持不變

0xBFF8—加載輸入寄存器B,滿量程數據,DAC寄存器和輸出保持不變

0xB000—加載輸入寄存器B,其中量程數據、DAC寄存器和輸出保持不變

0xA000—用零電平數據加載輸入寄存器B,DAC寄存器和輸出保持不變

0x0000 - 無操作

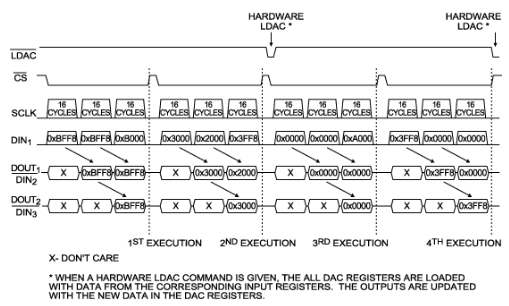

圖5.電路 #1 — 命令序列 B。

在前三個命令周期中,菊花鏈中的三個IC中的每一個都在其移位寄存器中接收一個命令。IC1、IC2 和 IC3 的命令分別為0xB000、0xBFF8和0xBFF8。這些命令在/CS的上升沿執行(第一次執行)。首次執行后,IC1、IC2和IC3的輸入寄存器B分別加載中間量程、滿量程和滿量程數據。此時,B1、B2、B3保持不變,因為每個IC的DAC寄存器B保持不變。

在接下來的三個命令周期中,僅加載輸入寄存器A的命令將寫入每個IC的移位寄存器。DAC寄存器A及其輸出保持不變。在/CS的上升沿,IC1、IC2和IC3的輸入寄存器A分別加載滿量程、零電平和中間電平數據。此時,A1、A2和A3保持不變,因為僅更新了輸入寄存器A,而不是DAC寄存器A。

第二次執行后的硬件/LDAC命令(驅動/LDAC低電平有效)加載所有DAC寄存器及其各自輸入寄存器中的數據。DAC輸出使用來自其相應DAC寄存器的數據進行更新。A1、B2 和 B3 進入滿量程。A2 降至零電平,A3 保持在中電平。

在第三系列命令周期中,IC2和IC3被賦予NO-OP命令(0x0000),而IC1接收0xA000命令,以加載其輸入寄存器B的零電平數據。第三次執行后,所有輸出保持不變。

在第四個命令周期系列中,IC1和IC2接收NO-OP命令,而IC3接收0x3FF8。第四次執行后,IC3的輸入寄存器A加載滿量程數據。另一個硬件/LDAC命令使用輸入寄存器中的數據加載DAC寄存器。這會導致 B1 從中間量程變為零電平,A3 從中間量程變為滿量程。所有其他輸出保持不變。

| 模擬輸出名稱 | 輸出狀態 | |||

| 上電后(RSTV = VDD) | 首款硬件低電平有效LDAC | 第二個硬件低電平有效LDAC | ||

| IC1 | A1 | 中檔 | 滿量程 | 滿量程 |

| B1 | 中檔 | 中檔 | 零刻度 | |

| IC2 | A2 | 中檔 | 零刻度 | 零刻度 |

| B2 | 中檔 | 滿量程 | 滿量程 | |

| IC3 | A3 | 中檔 | 中檔 | 滿量程 |

| B3 | 中檔 | 滿量程 | 滿量程 | |

示例電路 #2

圖6所示為三個采用菊花鏈配置的MAX5290雙通道、12位DAC。PU 連接到 DVDD,模擬輸出通電至滿量程。MAX5290沒有用于菊花鏈的專用數字輸出。相反,兩個UPIO(用戶可編程輸入/輸出)引腳中的一個必須由串行接口編程才能DOUTDC_模式。詳見MAX5290數據資料。

圖6.菊花鏈電路 #2。

圖7給出了命令序列示例,使用了以下命令(更多信息參見MAX5290數據資料)。

0xDFFF—用滿量程數據加載所有輸入和DAC寄存器,DAC A和B輸出更新

0xD800—使用中間量程數據加載所有輸入和DAC寄存器,DAC A和B輸出更新

0xD000—用零電平數據加載所有輸入和DAC寄存器,DAC A和B輸出更新

0xE400 — 將 DAC A 和 DAC B 置于關斷模式

0xE40F—使DAC A和DAC B退出關斷模式

0xFFFF - 無操作

圖7.電路 #2 示例命令序列。

加載到每個器件移位寄存器的命令在/CS的上升沿執行。在第一次執行時,所有DAC輸出都會更新。IC1的DAC輸出變為零電平,IC2的DAC輸出變為中間電平,IC3的DAC輸出變為滿量程。

在第二個命令周期中,IC2的DAC A和B都處于關斷模式,命令0xE400。無操作命令使IC1和IC3不受影響。在第三個命令周期之后,IC1的輸出變為滿量程,IC3的輸出變為零電平。當IC2的輸出保持關斷狀態時,數據在內部輸入和DAC寄存器中更新。IC2在最后一個命令周期內恢復到正常工作模式,輸出進入滿量程。

| 模擬輸出名稱 | 輸出狀態 | |||||

| 上電后(PU = VDD) | 首次執行后 | 第二次執行后 | 第三次執行后 | 第四次執行后 | ||

| IC1 | A1 | 滿量程 | 零刻度 | 零刻度 | 滿量程 | 滿量程 |

| B1 | 滿量程 | 零刻度 | 零刻度 | 滿量程 | 滿量程 | |

| IC2 | A2 | 滿量程 | 中量程 | 關閉 | 關閉 | 滿量程 |

| B2 | 滿量程 | 中量程 | 關閉 | 關閉 | 滿量程 | |

| IC3 | A3 | 滿量程 | 滿量程 | 滿量程 | 零刻度 | 零刻度 |

| B3 | 滿量程 | 滿量程 | 滿量程 | 零刻度 | 零刻度 | |

-

微控制器

+關注

關注

48文章

7922瀏覽量

153790 -

寄存器

+關注

關注

31文章

5424瀏覽量

123505 -

SPI

+關注

關注

17文章

1785瀏覽量

94879

發布評論請先 登錄

【分享】EasyGo 鏈式SVG系統的實時仿真應用

如何讀取ADS1299菊花鏈數據?

如何用ADS1271的SPI接口模式與STM32進行通信?

如何讓SPI額外發出一個時鐘?

STM32 與ads1271的SPI通信問題

可實現工業級精度和分辨率菊花鏈溫度傳感器包括BOM及原理圖

解決了合并單元對前端需求的模擬前端 (AFE)設計

FPGA菊花鏈下載時initialize chain識別不到器件

8片菊花鏈式WS2812B 8x8 RGB LED矩陣開源

TIDA-010076-通過單對以太網 (T1) 實現菊花鏈式電源和數據傳輸的PCB layout 設計

BQ79600(UART/SPI至菊花鏈網橋IC)的安全手冊

菊花鏈式SPI器件

菊花鏈式SPI器件

評論