cy68013

本教程是基于FPGA的cy7c68013a的USB雙向通信實驗,本教程主要內容:

1.cy7c68013a的固件編寫,以及生成iic固件和下載固件。

2.cy7c68013a的slave模式,以及他的讀寫時序

3.cy7c68013a的FPGA的上板測試,包括發送和接收兩部分

02開發過程

cy68013

01驅動

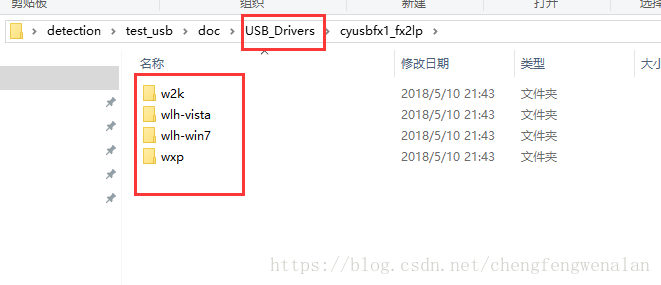

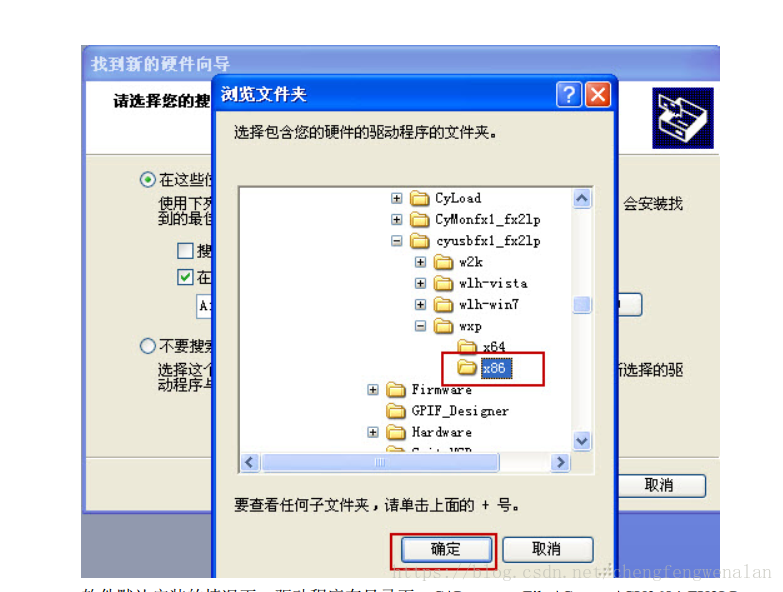

在進行試驗前要先安裝好Cypress提供的usb驅動,插上usb后,電腦就會檢測到未識別的設備,這時打開設備管理器,右鍵未識別的usb,然后手動選擇驅動。

在驅動會在本教程最后的鏈接中給出,如圖所示:

02固件

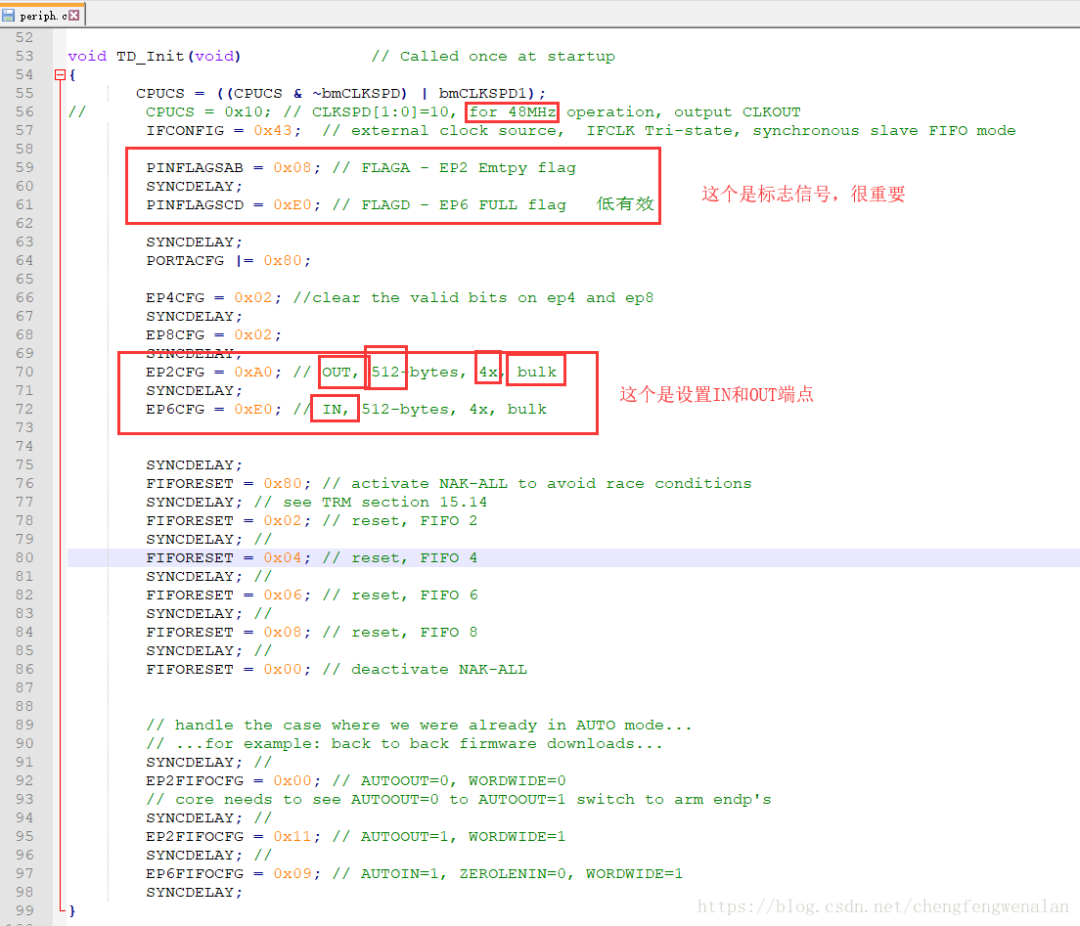

固件是在CY68013的FPGA內部有一個MCU,需要給MCU固化程序,固件的編寫主要是確定IN和OUT端點,以及一些標志信號。

固件只需要改這些參數即可,一般情況下不需要修改,很容易看出本教程中設置的時鐘是48MHz,然后設置EP2為OUT端點,512字節,4緩沖,bulk (注意OUT,IN都是相對PC來說的,OUT表示PC--->cy7c68013a,IN則相反)

EP6為IN端點,512字節,4緩沖,bulk

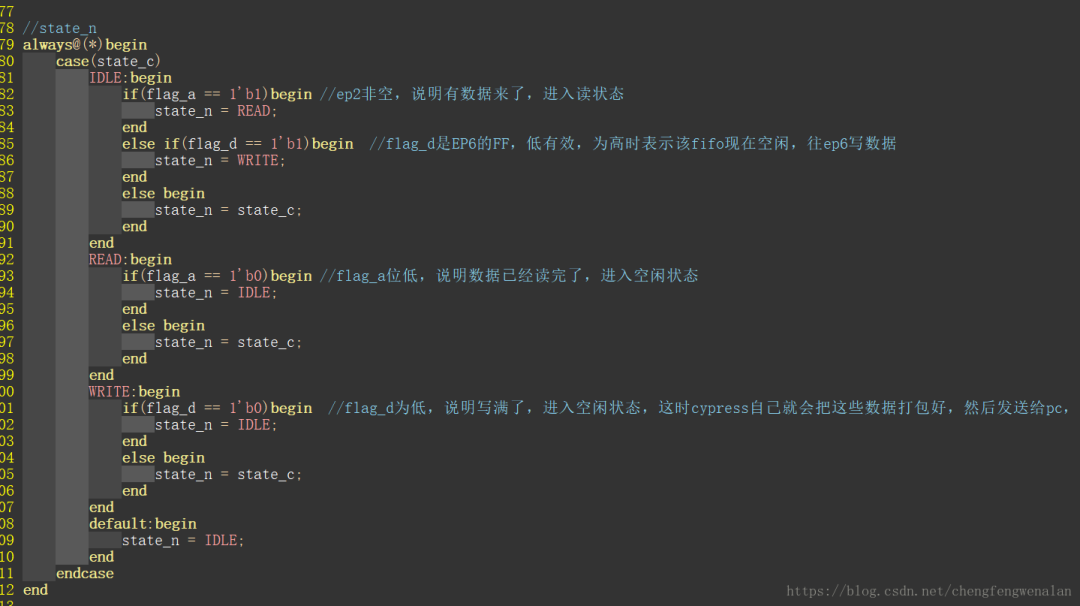

flag_a 為EP2的EF,也就是空標志信號,為低時表示空,也就是沒有數據過來,為高則表示有數據來了

flag_d 為EP6的FF,也就是滿標志信號,為低時表示寫滿了,這時再去寫就是無效寫了,為高則表示沒有寫滿,可以繼續寫。

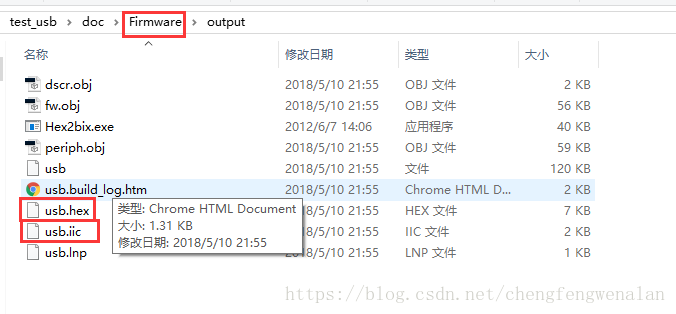

教程提供的固件所在文件夾:固件源碼什么的都在Firmware文件中

03時序

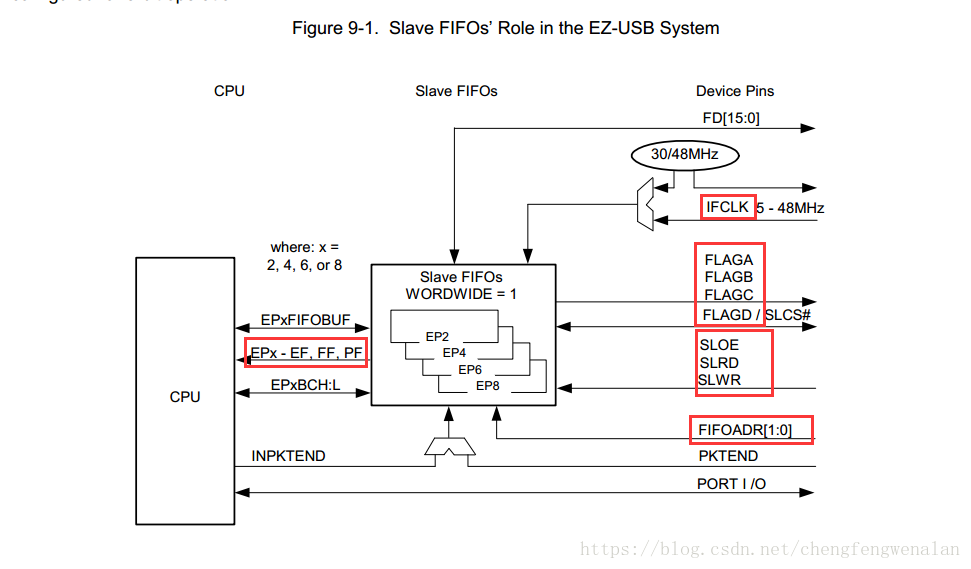

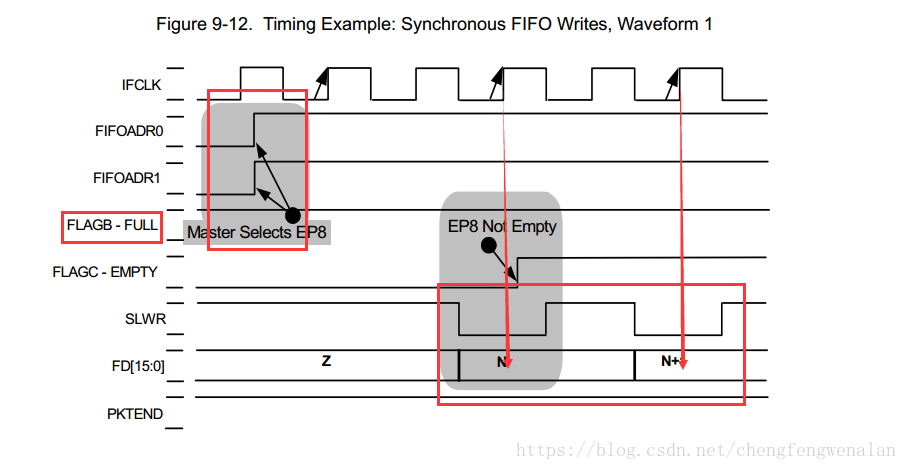

Slave FIFO的時序如圖所示。

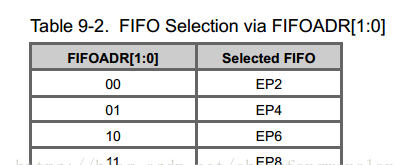

有圖很容易看出,再寫之前要先把FIFOADR確認好,這個決定了你寫的對象是誰

slave讀操作

然后在該fifo非滿時(相應的FF標志位高),才可以進行寫操作,這個時序很簡單,就是拉低slwr信號就可以了,注意FD要與slwr對齊。

注意:寫操作時,slwr與FD的數據都是FPGA來控制的,為了讓cy7c68013a更好的采樣,ifclk與clk反向之后再發送給cy7c68013a.

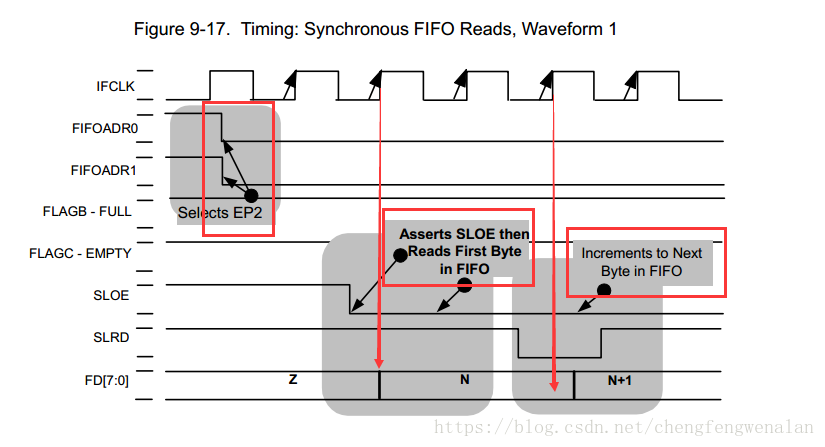

讀時序跟寫也是類似的,再讀之前先確定FIFOADR,然后拉低sloe,這時FD總線就會出現第一個數據,然后檢測到slrd為低時,FD就會顯示下一個數據。

04FPGA與cy7c68013a通信

前面主要是準備工作,現在正是進入測試:

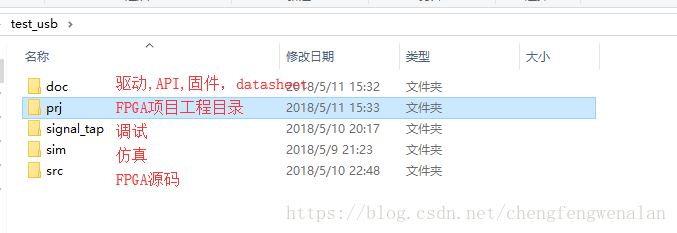

項目工程如下:

具體代碼都已經有了詳細注釋了,這里就不詳細解釋。

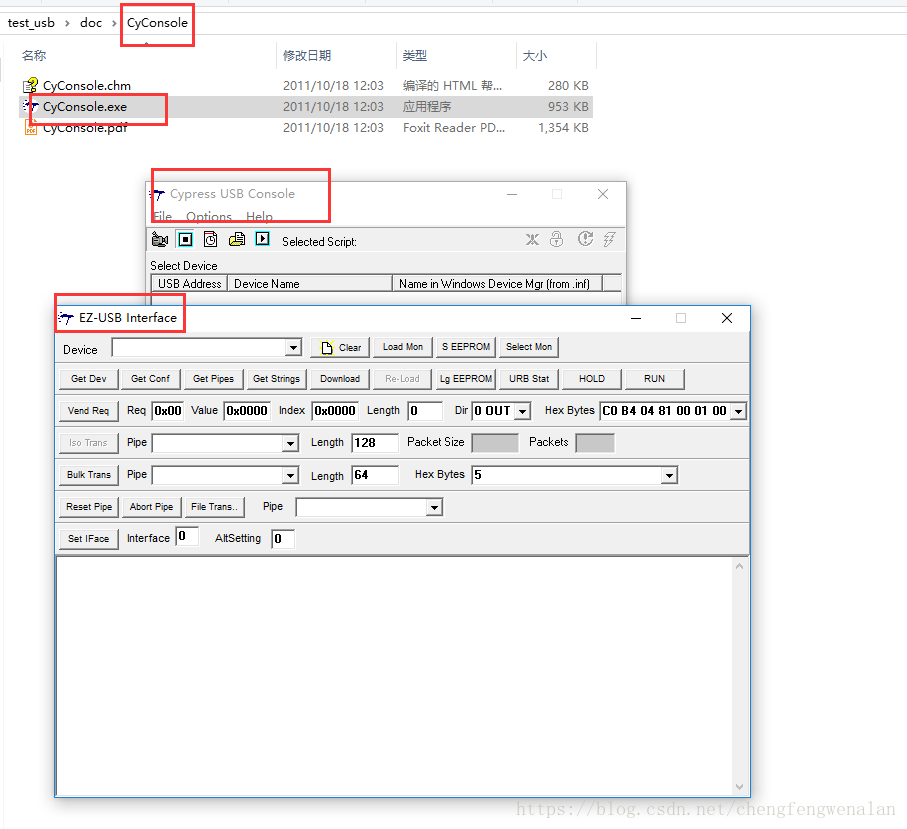

本教程所用的調試工具是官方的工具

03調試

Deep learnning

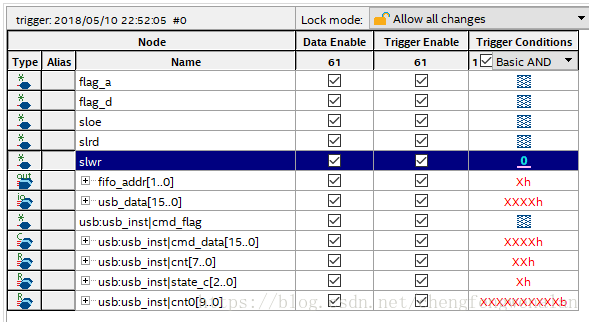

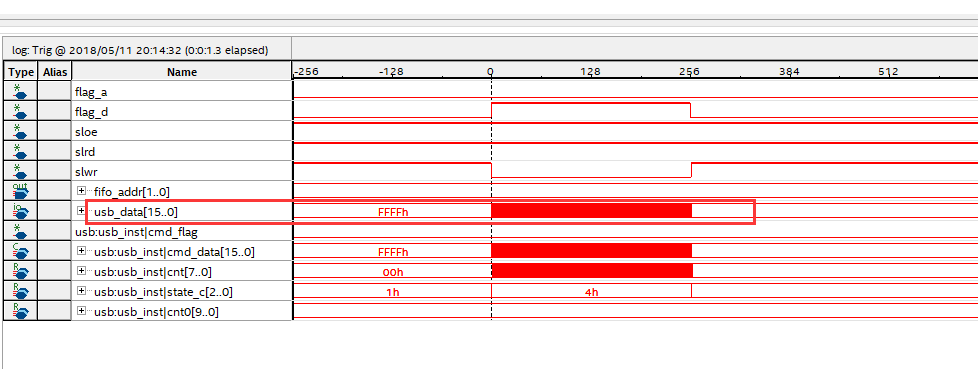

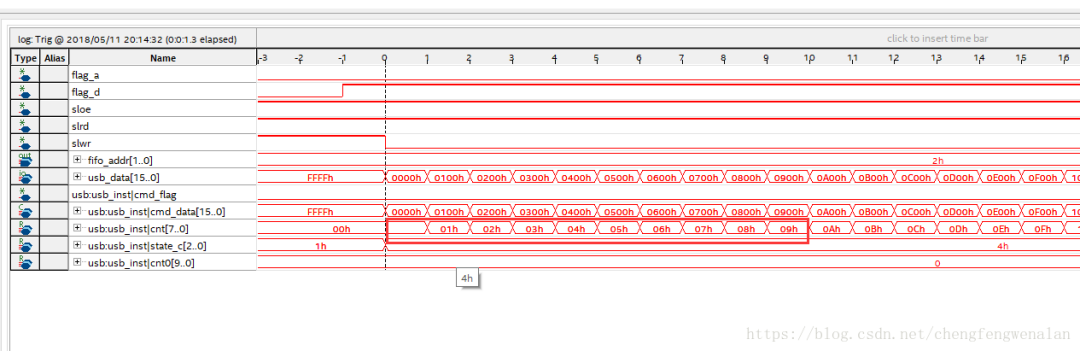

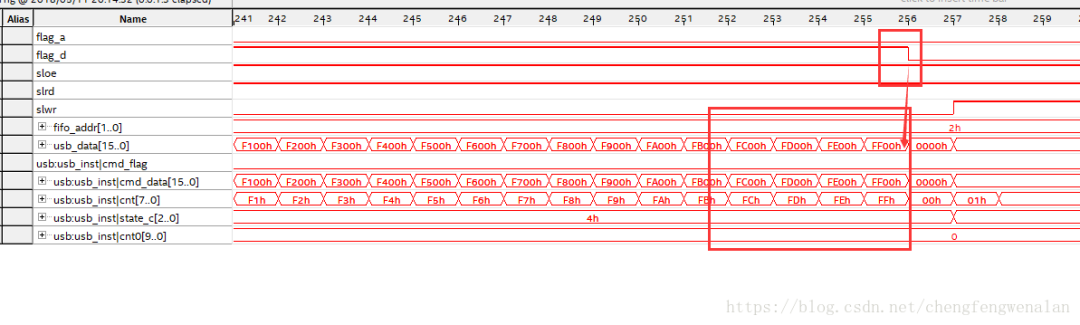

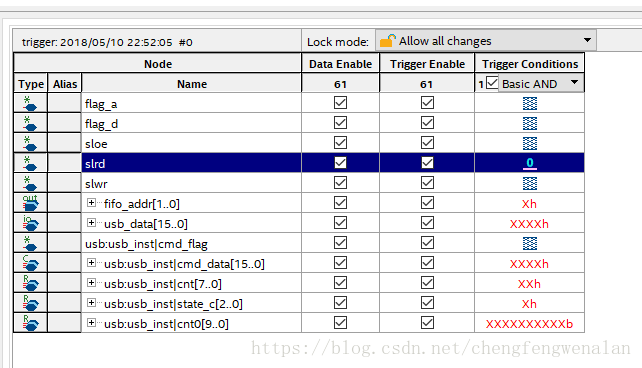

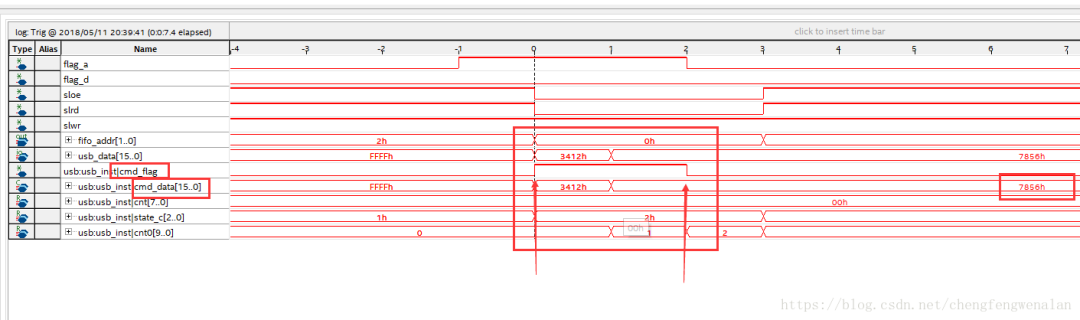

下面給出寫的signal tap 的調試截圖

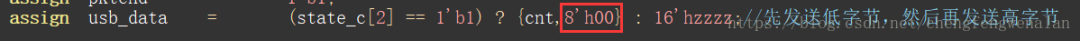

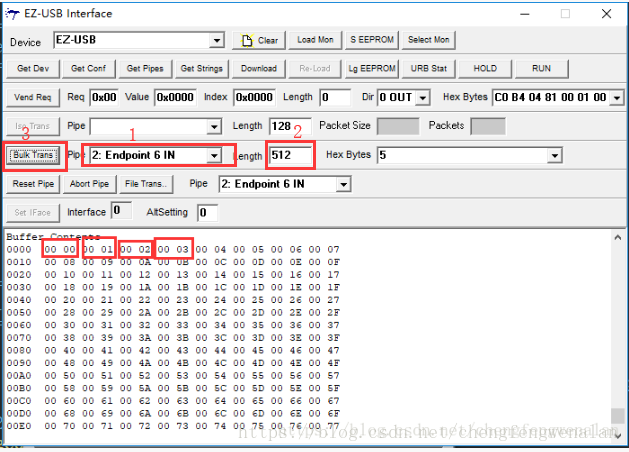

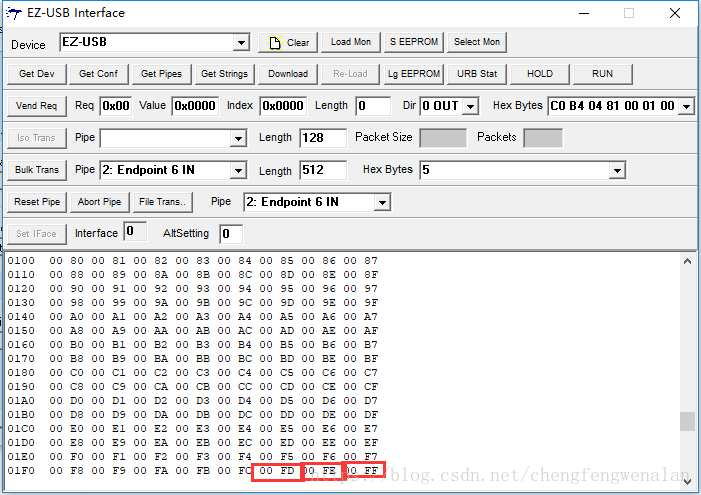

寫是一次寫512個字節數據,0-255,注意usb的fifo是一次發送16位的,也就是2個字節。先發送低字節,然后再發送高字節,這我直接把低字節給賦值為0了

前面局部放大圖

后面局部放大圖,注意只有在flag_d為高時,slwr為低才是有效寫,否則就是無效寫,因為當flag_d為低時,表示寫滿了,這時fifo就會丟棄后面寫的數據。

PC端接收到的數據要2個字節一起讀,因為usb是16位發送的,可以看出接收到的數據的確是0000-00FF。

注意:pc接收數據按照下圖標的編碼順序執行

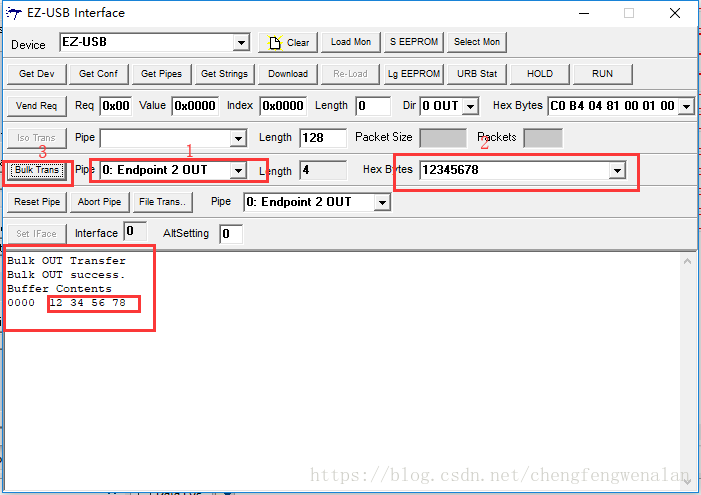

pc發送數據按1-->2-->3的步驟,可以看出我們發送了12 34 56 78 這4個字節

注意這里我是設置了cmd_flag標志信號的,只有cmd_flag為高時的cmd_data的數據才是有效的,也就是pc發送過來的數據

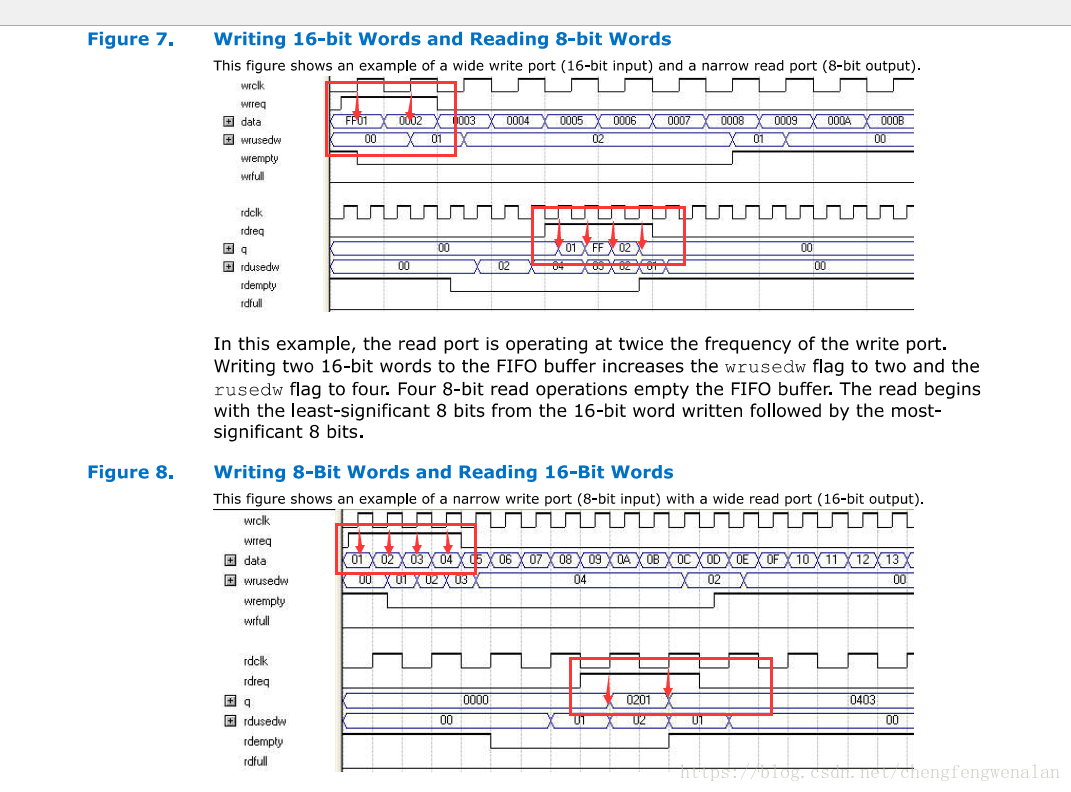

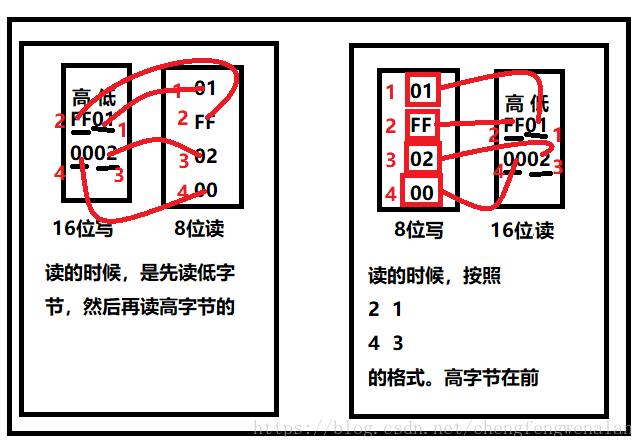

alter 的fifo ip 是可以讀寫位寬不一致的,具體看下面的圖。

由上圖可以看出這個和usb是一樣的格式,都是先發低字節,然后再發高字節。或者說先接收低字節,然后再接收高字節。

至此本教程就全部介紹完了,教程只挑了最關鍵的部分講述USB的開發,但是包括了固件,驅動和FPGA程序,一個完整的USB和FPGA開發的工程完全可以進行在此基礎上進行二次開發。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1645文章

22040瀏覽量

618171 -

usb

+關注

關注

60文章

8179瀏覽量

272739 -

Cypress

+關注

關注

11文章

137瀏覽量

83227 -

CY7C68013A

+關注

關注

2文章

20瀏覽量

21940 -

編寫

+關注

關注

0文章

29瀏覽量

8612 -

雙向通信

+關注

關注

0文章

13瀏覽量

8776

原文標題:基于FPGA的cy7c68013a雙向通信教程

文章出處:【微信號:gh_873435264fd4,微信公眾號:FPGA技術聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于FPGA的cy7c68013a雙向通信教程

基于FPGA的cy7c68013a雙向通信教程

評論