瑞薩電子采用 Verisium 平臺和應(yīng)用程序,可針對最新 R-Car SoC 汽車應(yīng)用設(shè)計中的特定錯誤,將糾錯效率提升 6 倍

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日宣布,瑞薩電子(Renesas Electronics)已采用全新的人工智能(AI)驅(qū)動的 CadenceVerisium驗證平臺,實現(xiàn)更高效的錯誤根本原因分析。基于全新的 Verisium 平臺,瑞薩顯著提高了糾錯效率,縮短其面向汽車應(yīng)用 R-Car 設(shè)計的上市時間。

Verisium 平臺及應(yīng)用包括 Versium AutoTriage、Verisium SemanticDiff、Verisium WaveMiner、Verisium PinDown、Verisium Debug 和 Verisium Manager,是 Cadence 整合企業(yè)數(shù)據(jù)及 AI(JedAI)平臺的組成部分,致力于實現(xiàn) AI 驅(qū)動的錯誤根本原因分析。從 IP 到 SoC ,單次或多次運行,該解決方案為用戶提供全面的糾錯解決方案,利用波形圖、原理圖、動因追溯和 SmartLog 技術(shù)建立快速、完整的交互式后處理糾錯流程,進一步提高糾錯效率。

“質(zhì)量和效率是確保 R-Car 設(shè)計按時交付的關(guān)鍵,”瑞薩設(shè)計越南(Renesas Design Vietnam Co., Ltd.)總裁阪本憲成先生表示,“Cadence Verisium Debug 平臺幫助工程師完成從 IP 到 SoC 設(shè)計的完整糾錯。全新的波形格式符合現(xiàn)代驗證的需求,并將仿真探測性能提高 2 倍。采用 AI 驅(qū)動的 Verisium 應(yīng)用,我們將糾錯效率提升至最高 6 倍,設(shè)計團隊也得以進一步縮短驗證周期。”

“AI 將重塑 EDA 領(lǐng)域的格局,”Cadence 高級副總裁兼系統(tǒng)與驗證事業(yè)部總經(jīng)理 Paul Cunningham 說道,“通過將驗證全流程輸入和輸出數(shù)據(jù)匯總到 Cadence JedAI 平臺,我們得以開發(fā)全新的基于 AI 的 Verisium 應(yīng)用,大幅提高了驗證生產(chǎn)力和效率。”

基于 AI 的 Verisium 驗證平臺是 Cadence 驗證全流程的一部分,其中包括 PalladiumZ2 硬件仿真加速系統(tǒng),ProtiumX2 原型驗證系統(tǒng),Xcelium仿真平臺,Jasper形式化驗證平臺和 HeliumVirtual and Hybrid Studio 平臺。Cadence 的驗證全流程可提供最高的驗證吞吐率,用最少的時間和資金投入找到缺陷。Verisium 平臺和應(yīng)用支持公司的智能系統(tǒng)設(shè)計(Intelligent System Design)戰(zhàn)略,旨在實現(xiàn) SoC 卓越設(shè)計。

審核編輯:湯梓紅

-

Cadence

+關(guān)注

關(guān)注

67文章

978瀏覽量

144584 -

eda

+關(guān)注

關(guān)注

71文章

2942瀏覽量

178547 -

AI

+關(guān)注

關(guān)注

88文章

35476瀏覽量

281207 -

瑞薩電子

+關(guān)注

關(guān)注

37文章

2929瀏覽量

73359

原文標題:Cadence Verisium 驗證平臺以 AI 助力瑞薩電子提高糾錯效率

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Banana Pi 最新邊緣 AI 系統(tǒng)模塊 BPI-AI2N 采用瑞薩電子 RZ/V2N

Cadence Conformal AI Studio助力前端驗證設(shè)計

芯華章以AI+EDA重塑芯片驗證效率

Banana Pi 發(fā)布 BPI-AI2N & BPI-AI2N Carrier,助力 AI 計算與嵌入式開發(fā)

Banana Pi 與瑞薩電子攜手共同推動開源創(chuàng)新:BPI-AI2N

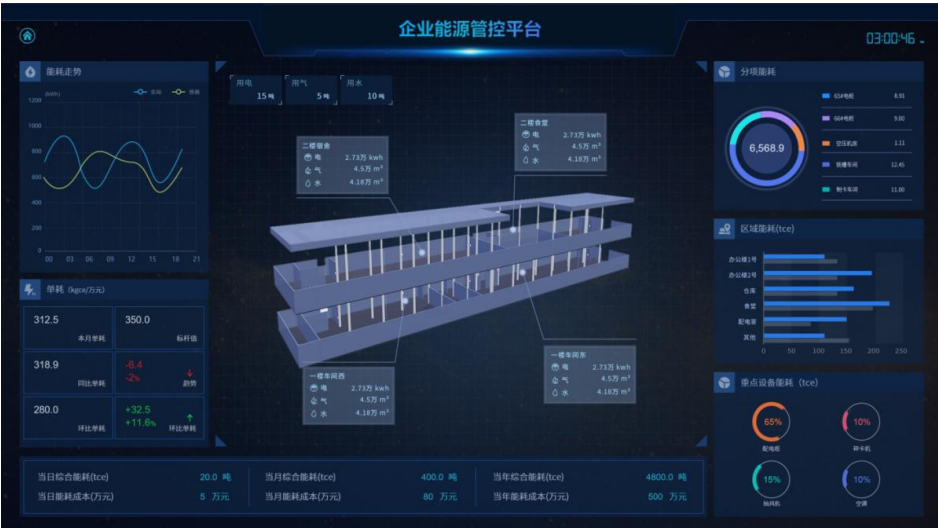

安科瑞緊跟時代潮流,推出AI企業(yè)能源管控平臺

Cadence Verisium Debug:統(tǒng)一調(diào)試平臺,加速SoC設(shè)計

瑞薩電子與伊世智能簽訂合作協(xié)議

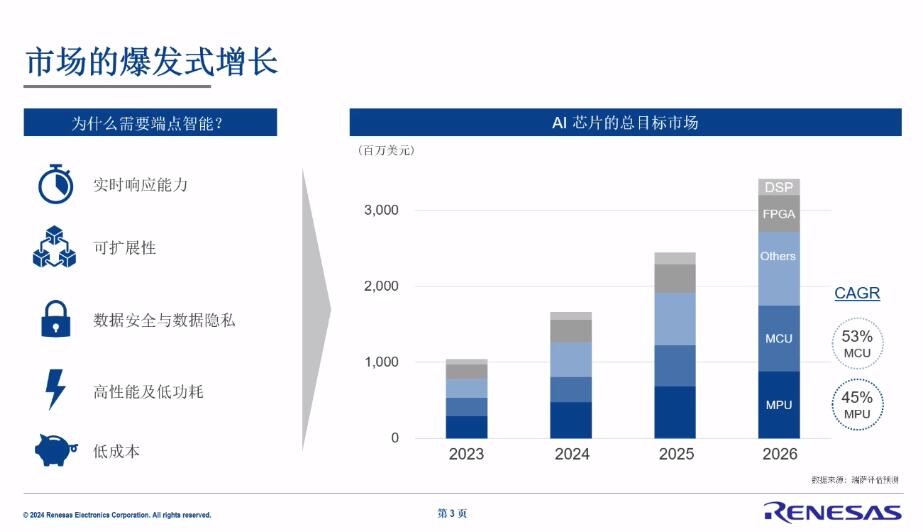

從工業(yè)機器視覺到協(xié)作機器人,瑞薩電子有哪些AI芯片的布局?

Cadence Verisium驗證平臺以AI助力瑞薩電子提高糾錯效率

Cadence Verisium驗證平臺以AI助力瑞薩電子提高糾錯效率

評論