了解模擬 IC 設計過程的基本步驟以及它與數字 IC 設計的比較。在本文中,我們將高層次地審視設計模擬 IC 的過程。

模擬 IC 設計與數字 IC 設計

模擬 IC 設計與數字 IC 設計有很大不同。其中數字IC設計在與確定的柵- /晶體管級放置和路由的具體系統和過程的抽象水平大多進行,模擬IC設計通常涉及更個性化的焦點到每個電路,甚至大小和每個具體晶體管。

此外,許多代工工藝主要是為具有模擬功能的數字 IC 開發的,這要求模擬 IC 設計人員處理更適合數字 IC 的工藝限制和功能。

設計規范

模擬設計團隊通常從一組規范和功能開始,就像數字 IC 設計一樣。從那里,各種功能的功能模型用于進一步縮小約束范圍,并導致對設備尺寸、類型和其他過程特征的決策。這可能包括晶體管選擇、高級布局規劃、電感器和電容器技術的包含以及 IC 和子電路的期望品質因數。

架構硬件描述語言 (AHDL),例如 VHDL-AMS,用于執行高級仿真并確定子塊的約束。在這個階段也可以開發一個測試平臺,稍后用于仿真,盡管模擬設計人員也經常為他們的子電路設計開發測試平臺。

子電路設計、物理布局和仿真

有了這些細節并根據模擬電路的復雜性,模擬設計團隊通常會將子電路設計分配給個人。進行理想化的宏觀測量,進一步確定子電路的約束和性能預期。

在此之后,這些宏觀原理圖被分解為具有從代工過程建模的電路元件的原理圖。對這些電路進行仿真和優化,然后開始物理布局過程。在寄生提取和布局后仿真之前完成布局和布線,然后是設計規則檢查 (DRC) 和布局與原理圖。

布局后模擬可能會揭示設計中的缺陷,可能需要重新設計、布局和模擬的迭代過程才能滿足最終設計目標并提交 IC 進行流片。子電路也可能在整個芯片布局和模擬之前經歷自己的設計、布局和模擬過程,盡管任何一種方法都可能導致需要在流片之前重新設計電路。

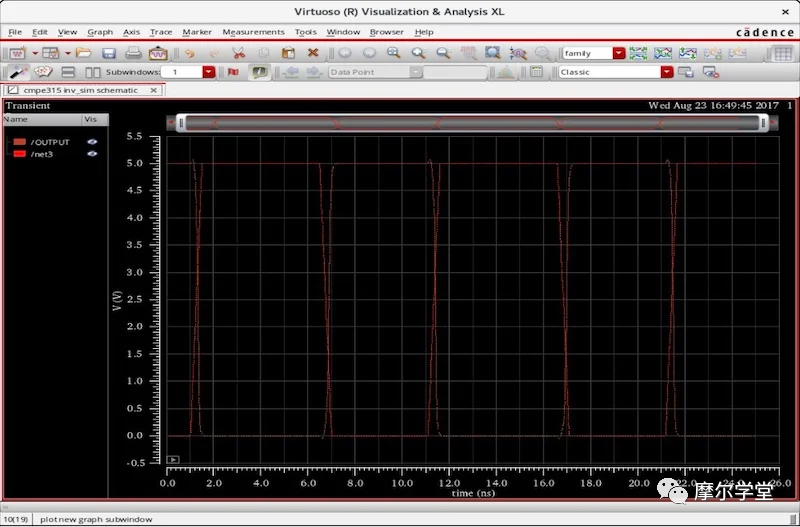

Cadence 模擬設計環境的波形窗口示例。截圖由 Saad Rahman 和 Chintan Patel通過馬里蘭大學巴爾的摩縣提供

模擬抽象級別

以下是模擬 IC 設計過程的抽象層次:

- 功能性

- 行為的

- 宏

- 電路

- 晶體管

- 物理布局

模擬 IC 設計流程

具體與模擬 IC 設計相關的步驟可細分如下:

- 設計規范

- 規格

- 約束

- 拓撲

- 測試臺開發

- 流程示意圖

- 系統級原理圖輸入

- 架構 HDL 仿真

- 塊 HDL 規范

- 電路級原理圖入口

- 電路仿真和優化

- 物理流

- 基于 PCell 的布局入口

- 設計規則檢查 (DRC)

- 布局與原理圖 (LVS)

- 寄生提取

- 布局后模擬

- 流片

-

電路

+關注

關注

173文章

6008瀏覽量

174066 -

模擬IC

+關注

關注

8文章

173瀏覽量

29710 -

晶體管

+關注

關注

77文章

9903瀏覽量

140104

發布評論請先 登錄

相關推薦

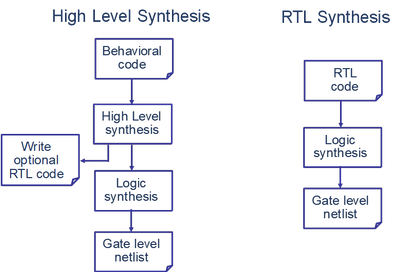

Vivado 高層次綜合

高層次綜合工作的基本流程

FPGA高層次綜合HLS之Vitis HLS知識庫簡析

利用Mentor高層次綜合技術快速實現復雜DSP算法

SOC設計中高層次功耗估算和優化技術

使用Vivado高層次綜合 (HLS)進行FPGA設計的簡介

揭示高層次綜合技術工作的基本概念

高層次綜合技術原理淺析

【開源硬件】從PyTorch到RTL - 基于MLIR的高層次綜合技術

使用Vivado高層次綜合(HLS)進行FPGA設計的簡介

高層次地審視設計模擬 IC 的過程

高層次地審視設計模擬 IC 的過程

評論