當前設計的一款ADC芯片,其具有數據串行輸出模式,由于串行輸出的數據不能夠直接后接理想DAC進行波形分析,因此不太方便。最好是能插入一個Serial_To_Parral的轉換模塊,將串行輸出的數據轉換為并行數據,再后接理想DAC產生模擬波形,如此就便于FFT分析了。

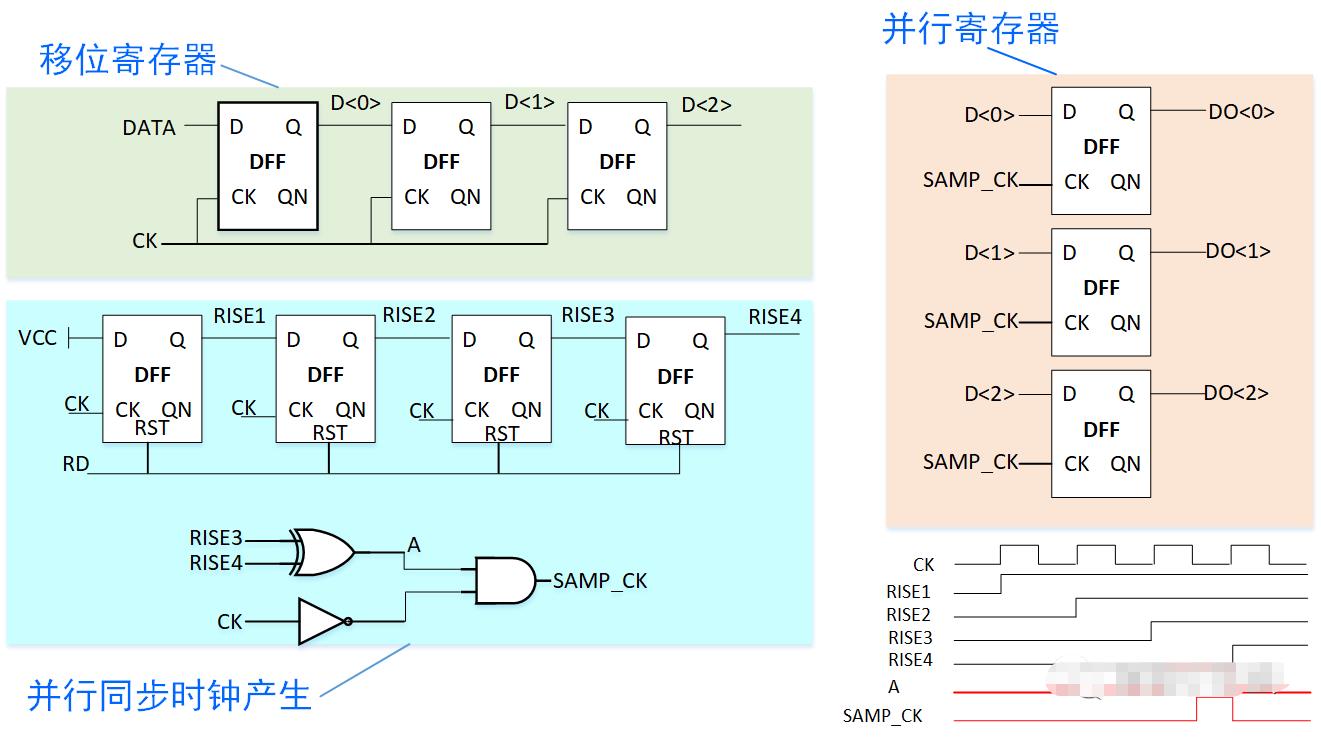

Serial_To_Parral:這里說的串并轉換電路,指可以實現串行數據轉并行數據的電路。本文提到的Serial_To_Parral模塊是用VerilogA基本組件搭建的,以一個3bit數據的轉換作為示例,其原理框圖如下圖所示:

圖1:Serial_To_Parral原理框圖

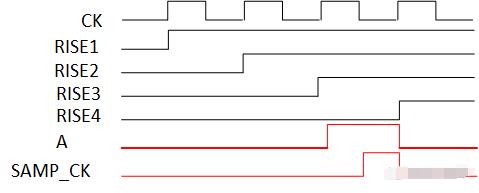

該電路的思路是:移位寄存器負責對DATA的每bit數據進行采樣并且向右移位,移位寄存器的每級輸出分別與右側并行寄存器的輸入相連。隨著CK最后一次上沿采樣完DATA數據后,在其后的半周期內將并行寄存器上的數據同步輸出。

圖2:相關時序圖

并行寄存器的同步采樣時鐘為“并行同步時鐘產生電路”產生。注意到,產生同步采樣時鐘的電路使用了RD信號對DFF進行復位。RD信號為ADC系統的讀取使能信號,RD=0時有效。因此在RD=1期間,DFF復位,SAMP_CK=0,并行寄存器上的輸出保持不變。

-

寄存器

+關注

關注

31文章

5424瀏覽量

123508 -

adc

+關注

關注

99文章

6649瀏覽量

548374 -

波形

+關注

關注

3文章

389瀏覽量

32146 -

轉換電路

+關注

關注

2文章

207瀏覽量

30847 -

串行數據

+關注

關注

0文章

54瀏覽量

16733

發布評論請先 登錄

如何使用其gearbox功能來實現不同的比率的串并轉換功能

FPGA設計思想與技巧之串并轉換和流水線操作

FPGA串并轉換實現問題

FPGA串/并轉換的思想相關資料推薦

串并轉換VHDL代碼

84調制解調程序(包括串并轉換,判決等等)

串并轉換 通過多通道串-并轉換器將多個同步串行數據流轉換為并

(18)FPGA串/并轉換的思想

串并轉換電路的實現方案

串并轉換電路的實現方案

評論