大俠好,歡迎來(lái)到FPGA技術(shù)江湖。本系列將帶來(lái)FPGA的系統(tǒng)性學(xué)習(xí),從最基本的數(shù)字電路基礎(chǔ)開(kāi)始,最詳細(xì)操作步驟,最直白的言語(yǔ)描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業(yè)學(xué)生、初入職場(chǎng)小白及打算進(jìn)階提升的職業(yè)開(kāi)發(fā)者都可以有系統(tǒng)性學(xué)習(xí)的機(jī)會(huì)。

系統(tǒng)性的掌握技術(shù)開(kāi)發(fā)以及相關(guān)要求,對(duì)個(gè)人就業(yè)以及職業(yè)發(fā)展都有著潛在的幫助,希望對(duì)大家有所幫助。本次帶來(lái)Vivado系列,本篇為FPGA零基礎(chǔ)學(xué)習(xí)之Vivado-LED流水燈實(shí)驗(yàn)。話不多說(shuō),上貨。

Vivado-LED流水燈實(shí)驗(yàn)

作者:李西銳校對(duì):陸輝

流水燈是大多數(shù)學(xué)習(xí)者接觸到的第一個(gè)實(shí)驗(yàn),也是非常經(jīng)典的一個(gè)實(shí)驗(yàn),在此,我們一起學(xué)習(xí)一下流水燈。

LED,又名發(fā)光二極管。LED燈工作電流很小(有的僅零點(diǎn)幾毫安即可發(fā)光),抗沖擊和抗震性能好,可靠性高,壽命長(zhǎng)。由于這些優(yōu)點(diǎn),LED燈被廣泛用在儀器儀表中作指示燈、液晶屏背光源等諸多領(lǐng)域。

發(fā)光二極管與普通二極管一樣具有單向?qū)щ娦浴=o它加上陽(yáng)極正向電壓后,通過(guò)5mA左右的電流就可以使二極管發(fā)光。通過(guò)二極管的電流越大,發(fā)出的光亮度越強(qiáng)。不過(guò)我們一般將電流限定在3~20mA之間,否則電流過(guò)大就會(huì)燒壞二極管。

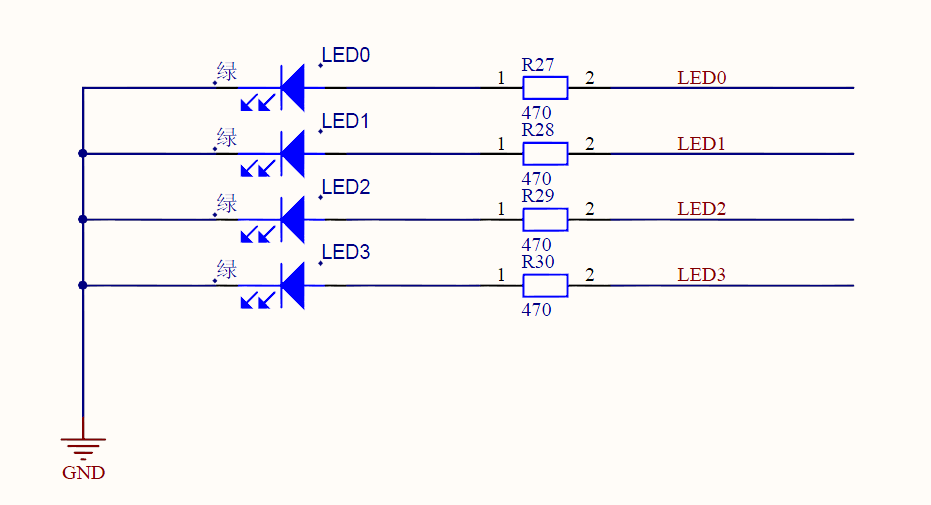

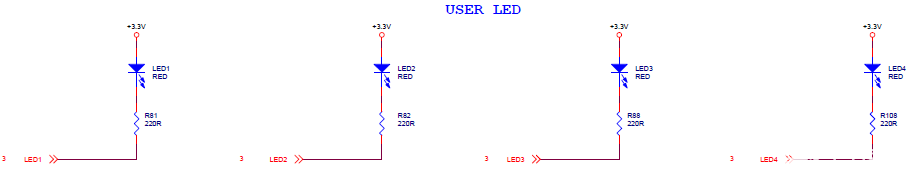

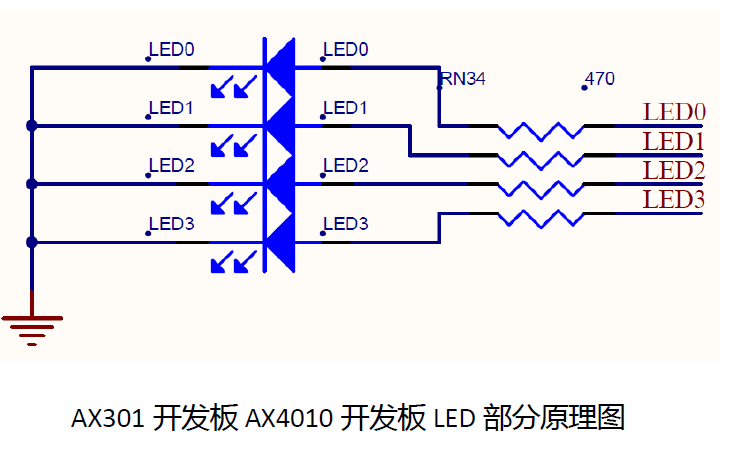

在我們的開(kāi)發(fā)板上有四個(gè)LED,設(shè)計(jì)邏輯為:FPGA 輸出高電平時(shí),LED 點(diǎn)亮;FPGA 輸出低電平時(shí),LED 熄滅。

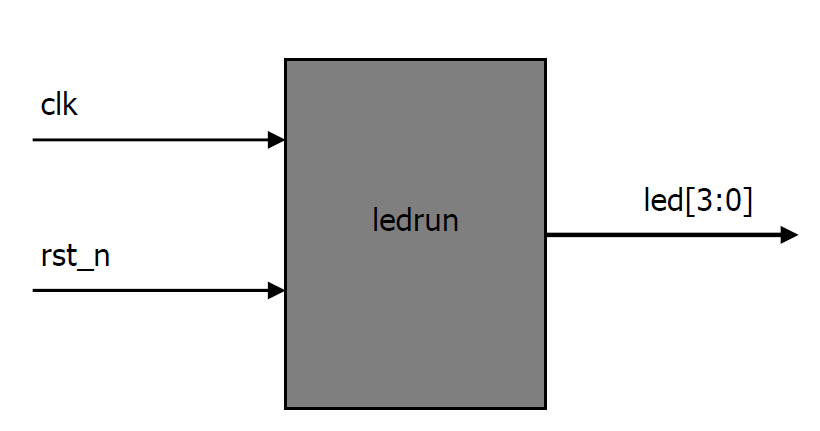

本次設(shè)計(jì)框架如上圖。

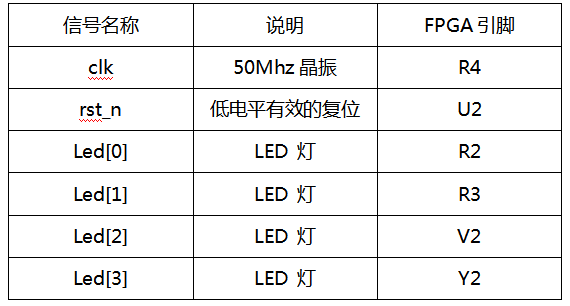

管腳說(shuō)明:

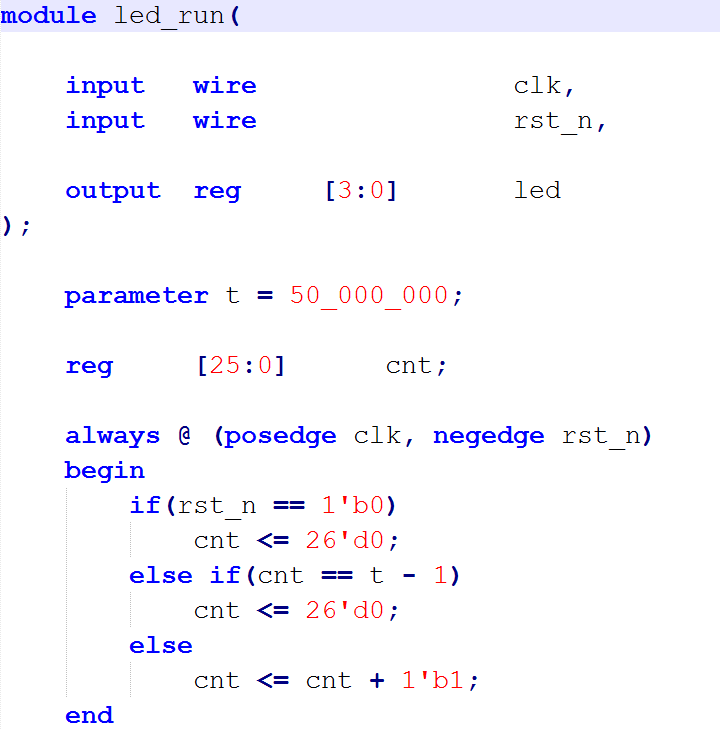

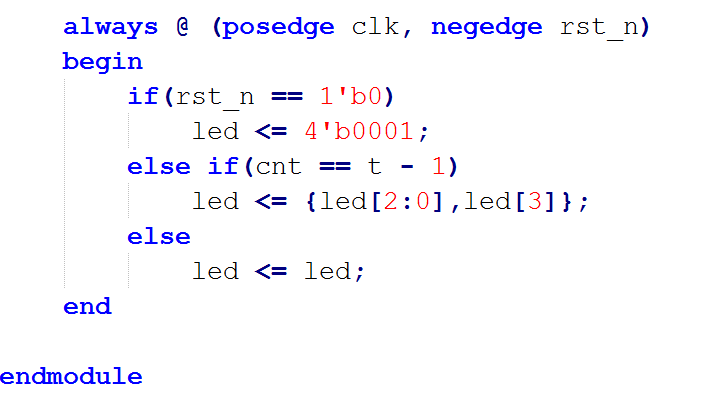

設(shè)計(jì)代碼如下:

parameter 可以定義一個(gè)參數(shù)(默認(rèn)是32 位)。在寫(xiě)代碼時(shí),對(duì)于某些數(shù)字,設(shè)計(jì)者經(jīng)常利用定義參數(shù)的方式進(jìn)行編寫(xiě),方便修改,也方便閱讀。

其中計(jì)數(shù)器,需要計(jì)數(shù)到1s所需的次數(shù),時(shí)間到了之后,LED燈切換點(diǎn)亮。按照此規(guī)則,實(shí)現(xiàn)LED的循環(huán)點(diǎn)亮。

在verilog 中,“{}”( 大括號(hào))的第一個(gè)特殊作用為位拼接。{a,b}相當(dāng)于將a 和b 拼接為一個(gè)整體,并且是高位為a,低位為b。當(dāng)led 輸出為4’b0001 時(shí),第一個(gè)led 點(diǎn)亮;經(jīng)過(guò)1 秒鐘,輸出4’b0010 時(shí),第二個(gè)led 點(diǎn)亮;經(jīng)過(guò)1 秒鐘,輸出4’b0100 時(shí),第三個(gè)led 點(diǎn)亮;經(jīng)過(guò)1 秒鐘,輸出4’b1000 時(shí),第四個(gè)led 點(diǎn)亮;經(jīng)過(guò)1 秒鐘,輸出4’b0001 時(shí),第一個(gè)led 點(diǎn)亮······按照上述的過(guò)程周而復(fù)始,就形成了流水燈。

不難發(fā)現(xiàn),led 的輸出,一直為3 個(gè)0,1 個(gè)1。并且1 的位置每1 秒鐘移動(dòng)一次,從頭到尾,然后又到頭。這種現(xiàn)象可以利用移位的思想進(jìn)行實(shí)現(xiàn)。即:led[3]<=led[2]; led[2]<=led[1];led[1]<=led[0]; led[0]<=led[3];如果將被賦值的組成一個(gè)整體,那就是led,賦值的組成一個(gè)整體就是{led[2:0], led[3]}。

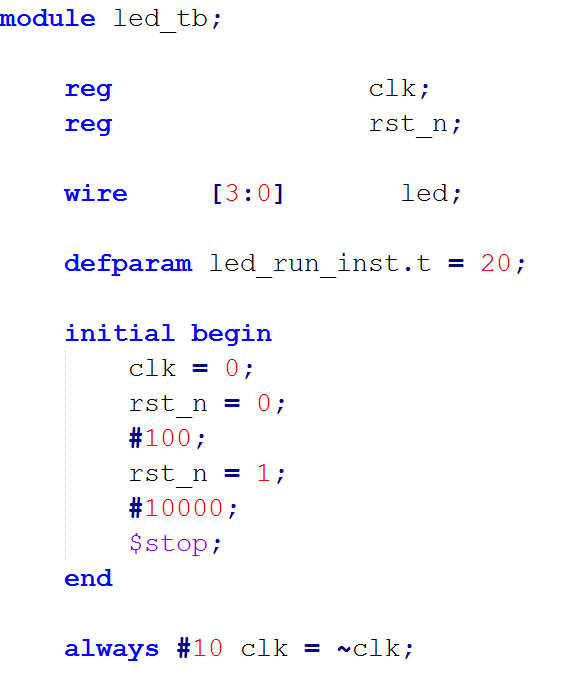

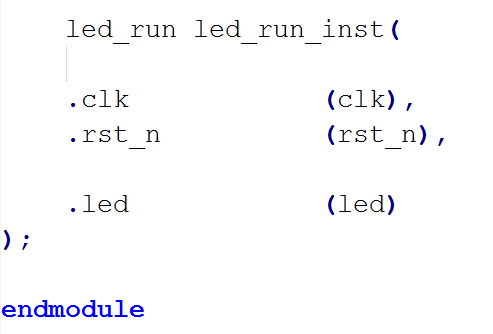

仿真代碼:

$stop 是一個(gè)系統(tǒng)任務(wù),功能為將仿真工具的仿真停止。運(yùn)行分析綜合后,打開(kāi)RTL 仿真。

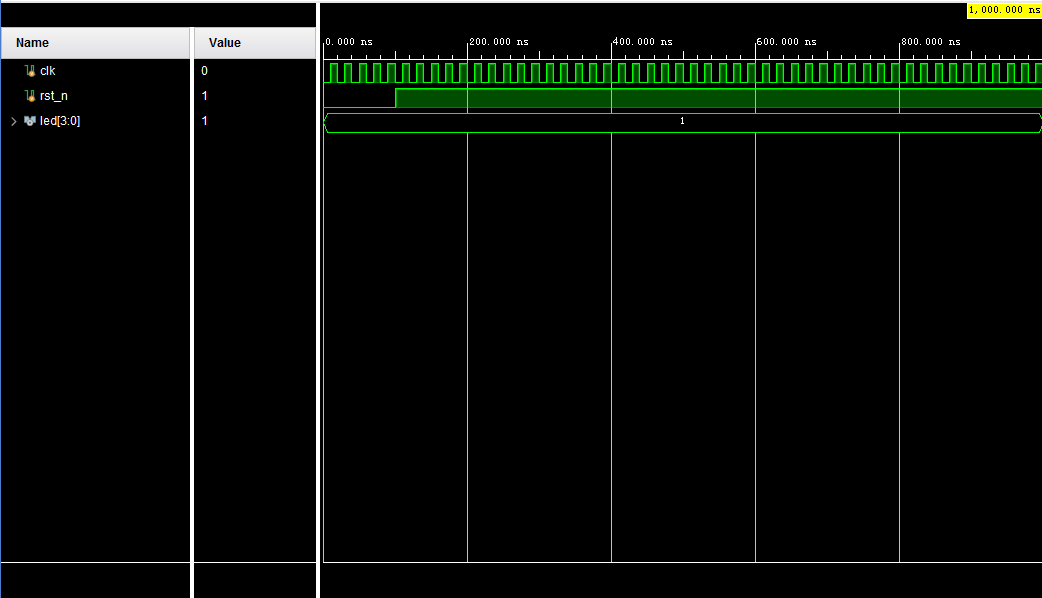

點(diǎn)擊Run Simulation,打開(kāi)仿真器。可以看到如圖所示波形。

由于我們?cè)O(shè)計(jì)的流水燈是每1 秒鐘流動(dòng)一個(gè),在上述的仿真中,led 數(shù)值是不會(huì)變化的。如果仿真幾秒鐘的話,仿真的時(shí)間會(huì)比較長(zhǎng)。在此不建議仿真幾秒鐘的時(shí)長(zhǎng),有可能會(huì)導(dǎo)致電腦卡住。

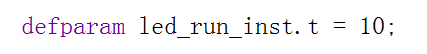

仿真時(shí),可以將t 的值,改成一個(gè)較小值。例如:10。然后在此編譯仿真。改的時(shí)候我們可以在仿真文件中加入一句話:

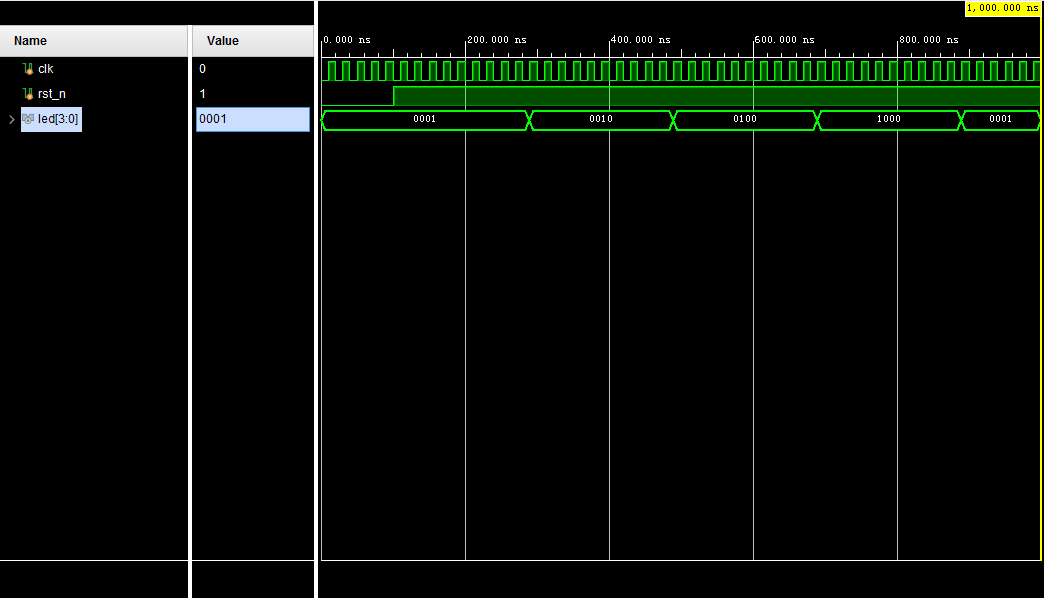

修改后我們重新運(yùn)行仿真工具,可以看到如圖所示波形:

這樣我們可以清楚的看到輸出變化的過(guò)程。另外,我們這樣做還有一個(gè)省事的地方,就是我們下板不需要再修改t的參數(shù)。

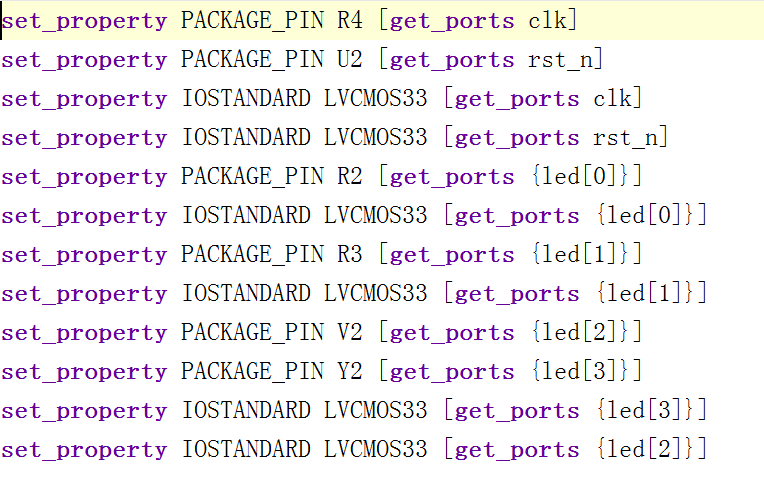

接下來(lái)我們分配引腳,生成下板文件。

分配好之后,點(diǎn)擊Generate Bitstream。

生成完成之后,點(diǎn)擊open Hardware Manager。下板即可。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21983瀏覽量

614689 -

led

+關(guān)注

關(guān)注

242文章

23742瀏覽量

671454 -

流水燈

+關(guān)注

關(guān)注

21文章

434瀏覽量

60340 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1637瀏覽量

81645 -

Vivado

+關(guān)注

關(guān)注

19文章

831瀏覽量

68326

原文標(biāo)題:FPGA零基礎(chǔ)學(xué)習(xí)之Vivado-LED流水燈實(shí)驗(yàn)

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

【紫光同創(chuàng)國(guó)產(chǎn)FPGA教程】【第二章】LED流水燈實(shí)驗(yàn)及仿真

FPGA流水燈實(shí)驗(yàn)

【Runber FPGA開(kāi)發(fā)板】配套視頻教程——LED流水燈實(shí)驗(yàn)

如何上手FPGA實(shí)現(xiàn)簡(jiǎn)單的流水燈效果

LED流水燈實(shí)驗(yàn)的相關(guān)資料推薦

基于FPGA Vivado的流水燈樣例設(shè)計(jì)資料分享

FPGA零基礎(chǔ)學(xué)習(xí):LED流水燈設(shè)計(jì)

FPGA零基礎(chǔ)學(xué)習(xí)之Vivado-LED流水燈實(shí)驗(yàn)

在Quartus下實(shí)現(xiàn)LED流水燈實(shí)驗(yàn)的資料說(shuō)明

詳解基于FPGA的數(shù)字電路對(duì)流水燈的實(shí)驗(yàn)

C51單片機(jī)實(shí)驗(yàn)——LED流水燈

【FPGA Vivado】基于 FPGA Vivado 的流水燈樣例設(shè)計(jì)

【教程分享】FPGA零基礎(chǔ)學(xué)習(xí):LED流水燈設(shè)計(jì)

HME FPGA入門(mén)指導(dǎo):HME-P(飛馬)系列開(kāi)發(fā)板實(shí)驗(yàn)教程——LED流水燈

FPGA零基礎(chǔ)學(xué)習(xí)之Vivado-LED流水燈實(shí)驗(yàn)

FPGA零基礎(chǔ)學(xué)習(xí)之Vivado-LED流水燈實(shí)驗(yàn)

評(píng)論