創(chuàng)建盡可能靈活的小芯片已經(jīng)吸引了半導(dǎo)體生態(tài)系統(tǒng)的想象力,但來(lái)自不同代工廠的小芯片的異構(gòu)集成將如何發(fā)揮作用仍不清楚。

半導(dǎo)體生態(tài)系統(tǒng)中的許多公司仍在弄清楚他們將如何適應(yīng)這個(gè)異構(gòu)的小芯片世界以及他們需要解決哪些問(wèn)題。雖然幾乎每個(gè)人都同意小芯片是未來(lái)設(shè)計(jì)的重要組成部分,但仍有許多障礙需要克服。

Rambus產(chǎn)品管理高級(jí)總監(jiān) Frank Ferro 表示:“大公司一直在使用自己的定制解決方案在內(nèi)部開(kāi)展此類(lèi)技術(shù)。” “他們?cè)缙谝庾R(shí)到的一些優(yōu)勢(shì)現(xiàn)在正在引起其他沒(méi)有資源自己做的公司的興趣。”

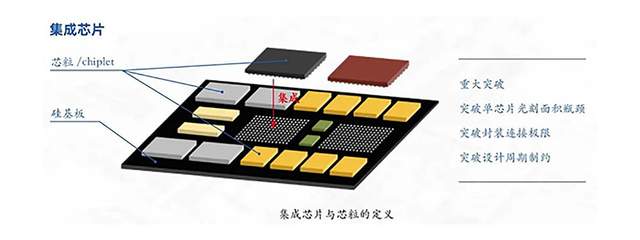

小芯片的優(yōu)勢(shì)之一是能夠?qū)⑹褂貌煌圃旃に囬_(kāi)發(fā)的技術(shù)融合在一起。“例如,一個(gè) I/O 芯片可以由一個(gè)代工廠制造,核心處理器可以由另一個(gè)代工廠制造,然后這些可以放在一個(gè)小芯片中,”Ferro 說(shuō)。“所以從這個(gè)意義上說(shuō),混合和匹配技術(shù)具有潛力。你可以說(shuō),‘我從 Foundry A 那里得到了一個(gè)很好的價(jià)格,我必須與 Foundry B 打交道,但現(xiàn)在我可以將它們混合在一起,’因?yàn)樾⌒酒瑤缀蹩梢员徽J(rèn)為是獨(dú)立的芯片。”

然而,今天,它并不是那么簡(jiǎn)單。如果多個(gè)芯片來(lái)自多個(gè)地方,第一步是確定每個(gè)芯片的引腳間距。

Cadence的 IC 封裝和跨平臺(tái)解決方案產(chǎn)品管理組總監(jiān) John Park 表示:“標(biāo)準(zhǔn)封裝有一個(gè)選項(xiàng),它具有倒裝芯片 125 微米或 130 微米的引腳間距,而不是內(nèi)插器上的東西。” . “這可能低至 35 微米間距。這是挑戰(zhàn)之一。如果引腳間距降至 40 微米或 50 微米,我必須使用硅中介層或某種互連橋來(lái)做到這一點(diǎn)。這會(huì)增加成本,這也是為什么有標(biāo)準(zhǔn)封裝版本的原因,因?yàn)槿绻惆阉袞|西都放在 125 微米左右的倒裝芯片間距上,你可以在傳統(tǒng)的層壓封裝上做到這一點(diǎn),這比去硅中介層或嵌入式橋接技術(shù)。”

Park 說(shuō),一旦互連被整理出來(lái),并且封裝類(lèi)型已經(jīng)確定,放下互連就不是很有挑戰(zhàn)性了,因?yàn)樗?lèi)似于需要 45o 角的 PCB 和層壓型布線的封裝風(fēng)格。“在某些情況下,需要所有角度。在金屬進(jìn)入焊盤(pán)的地方需要圓角。在 [相位] 控制中,差分對(duì)必須相互匹配。還需要屏蔽。這些都是 PCB 工具已經(jīng)完成的事情,而不是做這些巨大的金屬片,我們要縮小到一兩微米。PCB 工具可以對(duì)其進(jìn)行擴(kuò)展,因此布線的最大挑戰(zhàn)就是所需的時(shí)間。在封裝中,我們習(xí)慣于處理幾千個(gè)信號(hào)連接,盡管電源和地線連接的數(shù)量要多得多。

混合晶圓chiplet 生態(tài)系統(tǒng)

Synopsys科學(xué)家 Mike Borza認(rèn)為,從長(zhǎng)遠(yuǎn)來(lái)看,將會(huì)有一個(gè) mixed-foundry chiplet 生態(tài)系統(tǒng)。“在那之前,大部分集成系統(tǒng)將由一家供應(yīng)商提供,而該供應(yīng)商既是小芯片的制造商,也是整個(gè)封裝的集成商。”

可能有一些來(lái)自外部供應(yīng)商的具有小功能甚至大功能的特定小芯片。“如果外部小芯片供應(yīng)商之間存在競(jìng)爭(zhēng),則需要對(duì)接口進(jìn)行標(biāo)準(zhǔn)化,或者集成商需要能夠處理提供相同接口的不同封裝。人們這樣做,但這并不方便。為標(biāo)準(zhǔn)功能提供標(biāo)準(zhǔn)引腳輸出要方便得多,而且您可以為每個(gè)供應(yīng)商使用相同的節(jié)點(diǎn),”Borza 說(shuō)。

這就是為什么如此關(guān)注 UCIe 標(biāo)準(zhǔn)的原因。“無(wú)論您是 Foundry A 還是 Foundry B,都必須遵守封裝技術(shù)要求,”Synopsys IP 產(chǎn)品線高級(jí)組總監(jiān) Mick Posner 說(shuō)。“假設(shè)您正在進(jìn)行基于中介層的高級(jí)設(shè)計(jì)。中介層是連接兩個(gè)芯片的基板,通常定義特定的引腳間距。如果它們要跨恰好在上面的基板進(jìn)行封裝,那么兩個(gè)芯片都必須從根本上遵守這一點(diǎn)。也就是說(shuō),從理論上講,沒(méi)有什么能阻止客戶(hù)在臺(tái)積電開(kāi)發(fā)芯片并在另一家代工廠開(kāi)發(fā)芯片,從另一家代工廠拉貨并將所有這些封裝在一起。這是多管芯系統(tǒng)的主要優(yōu)勢(shì)之一。雖然今天大部分工作都是由單一供應(yīng)商完成的,

Chiplet 封裝技術(shù)要求

Posner 說(shuō),另外一個(gè) chiplet 要求來(lái)自封裝技術(shù)。“有一種有機(jī)基質(zhì),是的。另一端是中介層。然后中間有一大堆新的封裝技術(shù),包括 InFO(TSMC 的集成扇出)、RDL(再分布層)扇出等,所有這些都有自己的路徑要求。”

正在開(kāi)發(fā)多線程路由器來(lái)應(yīng)對(duì)這些更大的挑戰(zhàn),Cadence 的 Park 指出,進(jìn)行此類(lèi)設(shè)計(jì)的工程團(tuán)隊(duì)通常使用 PCB 式路由器進(jìn)行信號(hào)路由。“然后,在許多情況下,如果設(shè)計(jì)具有復(fù)雜的電源結(jié)構(gòu),就像您在 IC 工具中看到的那樣,他們實(shí)際上會(huì)將這些結(jié)構(gòu)混合在一起,從 IC 工具中獲取電源和接地布線,并將其與信號(hào)合并路由。因此,這實(shí)際上是系統(tǒng)世界和 IC 的融合——它們?nèi)诤显谝黄穑渲邪枰墓ぞ吆蛯?zhuān)業(yè)知識(shí)。但總的來(lái)說(shuō),布局是由習(xí)慣于進(jìn)行這種樣式路由的系統(tǒng)人員完成的。只是現(xiàn)在連接多了很多。這意味著路由方面存在更多瓶頸。”

小芯片還有其他好處。Imperas Software的 CEO Simon Davidmann 說(shuō):“如果這些芯片又大又貴,它就可以消除其中一些芯片的風(fēng)險(xiǎn)。”. “說(shuō)處理器搞砸了。把它取下來(lái),再裝一個(gè)。這真是一個(gè)好處。如果您有 SoC,則無(wú)法更改處理器。如果你有一個(gè)小芯片,你可以用所有其他塊構(gòu)建一個(gè)新的小芯片,它就像印刷電路板一樣。如果印刷電路板上有 1,000 個(gè)元件,其中一個(gè)壞了,你松開(kāi)它,插入另一個(gè),它就可以工作了。即使在現(xiàn)場(chǎng)出現(xiàn)故障,更換小芯片中的一個(gè)芯片仍然比扔掉電路板并重新設(shè)計(jì)一塊新電路板更便宜,如果我所做的只是重新設(shè)計(jì)那一點(diǎn)點(diǎn)的話。由于小芯片基本上是硬 IP 的大塊,所以發(fā)生的情況是,如果我正在構(gòu)建芯片,而不是獲得處理器的版本 3,獲得芯片,然后必須等待一年并在版本 4 出現(xiàn)時(shí)制作新芯片出來(lái),我可以改變小芯片,當(dāng)一個(gè)新塊出現(xiàn)時(shí),我可以使用我仍然擁有的所有其余部分。我只是將 chiplet 處理器從 3 更改為 4,然后繼續(xù)前進(jìn)。”

至于物理問(wèn)題,除了需要進(jìn)行更多模擬和驗(yàn)證之外,Davidmann 認(rèn)為沒(méi)有任何實(shí)際影響。

新的小芯片挑戰(zhàn)

目前,AMD 和英特爾等大公司使用內(nèi)部設(shè)計(jì)的小芯片,基本上將 SoC 或 ASIC 分解為不同的功能。

西門(mén)子高級(jí)封裝解決方案總監(jiān) Tony Mastroianni 表示:“要做到這一點(diǎn),由于沒(méi)有小芯片生態(tài)系統(tǒng),他們需要同時(shí)進(jìn)行多個(gè)芯片設(shè)計(jì),因?yàn)樗羞@些芯片都需要設(shè)計(jì)為協(xié)同工作以構(gòu)建一個(gè)完整的系統(tǒng)。”數(shù)字產(chǎn)業(yè)軟件. “如果它是一個(gè)大型 ASIC,你將它分解成分層塊。可重復(fù)使用的 IP 主要用于您的模擬和高速 I/O。使用 chiplet,現(xiàn)在您可以將“超級(jí) ASIC”分解為更小的 chiplet,但您不一定必須使用相同的過(guò)程,您可以利用它來(lái)發(fā)揮自己的優(yōu)勢(shì)。如果你有一個(gè)大處理器,你可以使用 5nm 或 3nm 工藝。如果你有模擬/混合信號(hào),你可以使用一個(gè)更便宜的過(guò)程,在這方面效果更好。也可能有專(zhuān)門(mén)的 IP 只能在非常昂貴的節(jié)點(diǎn)中使用。如果你只需要一個(gè)接口,為什么不把它構(gòu)建到一個(gè)小芯片中呢?”

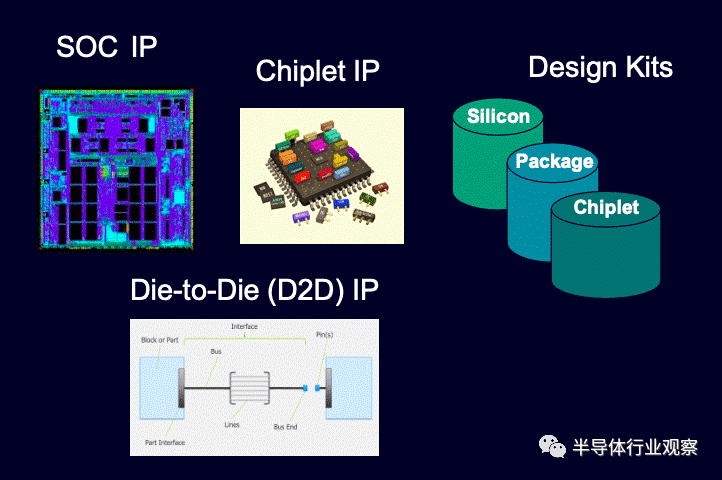

圖 1:chiplet 生態(tài)系統(tǒng)中的 IP

但當(dāng)涉及到由不同代工廠開(kāi)發(fā)的小芯片時(shí),情況就大不相同了。“你必須考慮這些標(biāo)準(zhǔn),并確保獲得所有正確的電壓,”Mastroianni 說(shuō)。“即使它來(lái)自同一個(gè)代工廠,你也必須擔(dān)心這一點(diǎn),因?yàn)樗鼈兊呐尾煌愿鶕?jù)定義,它們是兩種不同的芯片。這意味著有不同的角落,無(wú)論如何你都必須處理它。如果它們是在不同的工藝上制造的,那將使其更具挑戰(zhàn)性。其中很多是通過(guò) die-to-die 接口處理的——幾乎就像一個(gè) SerDes 接口——將它解耦,這些接口被設(shè)計(jì)成那樣。它更多的是其他信號(hào)的問(wèn)題,比如可能需要一些連接的低速 I/O,所以你必須擔(dān)心它。但通常,這些接口并不那么重要。這些標(biāo)準(zhǔn)協(xié)議涵蓋了高速 I/O。”

雖然 3D 設(shè)計(jì)有很多進(jìn)展,但尚不清楚這對(duì)商業(yè)小芯片是否有意義。“在 3D 中,布局布線工具將能夠支持不同的技術(shù),”他說(shuō)。“他們將處理這個(gè)問(wèn)題,這是一個(gè)非常 IC、以布局布線為中心的流程。無(wú)論您是否甚至需要為將要放在一起的每個(gè)小芯片建立模型,它們實(shí)際上都將作為一個(gè)整體設(shè)計(jì)在一起。你可能有一個(gè)可以作為小芯片出售的標(biāo)準(zhǔn),但那將是個(gè)例外。”

今天,今天大多數(shù)小芯片活動(dòng)都在2.5D中。“你可能在中介層和其他 ASIC 上有多個(gè) 3D 芯片,因?yàn)橥瑯樱词鼓阌?3D,由于熱限制,你可以堆疊的數(shù)量也有實(shí)際限制,”Mastroianni 說(shuō)。“當(dāng)你把它們疊起來(lái)時(shí),你不得不擔(dān)心熱量。這是更大的挑戰(zhàn)之一,同時(shí)受制于十字線尺寸。然而,您可以使用中介層或有機(jī)基板超越這一點(diǎn)。”

芯片/小芯片/系統(tǒng)架構(gòu)師如何與封裝技術(shù)團(tuán)隊(duì)和 ASIC 設(shè)計(jì)團(tuán)隊(duì)合作,以確定不同技術(shù)中可用的 IP 是小芯片設(shè)計(jì)的另一個(gè)重要方面。

“與 ASIC 設(shè)計(jì)相比,需要更多的架構(gòu)規(guī)劃,一旦你有了 ASIC 和規(guī)格,你只需轉(zhuǎn)動(dòng)曲柄,就可以做你的芯片了。小芯片不同。那里還涉及其他步驟。盡管如此,一旦你設(shè)計(jì)了 3D 芯片,它仍然可以作為小芯片重新使用。它只是一個(gè)三高或四高的小芯片,就像在 HBM 中一樣。在那里,您將需要將所有內(nèi)容集成到一個(gè)封裝中,”他說(shuō)。

Chiplet 通信

一個(gè) chiplet 究竟如何與另一個(gè) chiplet 通信是另一個(gè)需要解決的挑戰(zhàn),尤其是對(duì)于由多個(gè)代工廠開(kāi)發(fā)的 chiplet。這是許多標(biāo)準(zhǔn)工作的重點(diǎn)所在。

Intrinsic ID 的首席執(zhí)行官 Pim Tuyls 說(shuō):“如果你不能與來(lái)自其他地方的小芯片進(jìn)行通信,你就無(wú)法對(duì)它做任何事情。”“然后你需要另一個(gè)芯片,將一種類(lèi)型的通信轉(zhuǎn)換為另一種通信,這只會(huì)讓它變得更加復(fù)雜。它并沒(méi)有因此變得不那么復(fù)雜。與此相關(guān)的是安全。如果沒(méi)有鉤子和角,就無(wú)法保證安全。例如,如果小芯片沒(méi)有公鑰加密機(jī)制,您將無(wú)能為力。有時(shí)您可以使用軟件進(jìn)行修復(fù),但您必須為此做好準(zhǔn)備。小芯片的通信和安全級(jí)別的標(biāo)準(zhǔn)化將變得非常非常重要。”

是德科技首席應(yīng)用開(kāi)發(fā)工程師兼科學(xué)家 Matthew Ozalas表示,理想情況下,每個(gè)小芯片都被視為對(duì)物理封裝不敏感的獨(dú)立塊。然而,這并不總是一種選擇。

“例如,彼此靠近的小芯片可能會(huì)以熱、電磁或其他物理方式相互作用,”O(jiān)zalas 解釋道。“要對(duì)此類(lèi)交互進(jìn)行建模,您需要對(duì)小芯片內(nèi)部的布局結(jié)構(gòu)進(jìn)行分析。代工廠已經(jīng)在創(chuàng)建復(fù)雜的封裝模型,但這些封裝流程目前基于所有 IP 都包含在代工廠的“保護(hù)傘”中的假設(shè)。如果有來(lái)自多個(gè)代工廠的小芯片,更高級(jí)別的組裝和分析可能成為主要的絆腳石。電路、布局和基板的復(fù)雜模型都被認(rèn)為是敏感的。因此,標(biāo)準(zhǔn)化需要在小芯片內(nèi)實(shí)現(xiàn)低層結(jié)構(gòu)的協(xié)同仿真,同時(shí)通過(guò)適當(dāng)?shù)募用鼙Wo(hù)每個(gè)代工廠的個(gè)人 IP。除了這些 IP 和多物理問(wèn)題之外,還有更傳統(tǒng)的基于布局的組裝挑戰(zhàn),例如不同的堆疊、連接和跨小芯片的驗(yàn)證,這些問(wèn)題也必須以標(biāo)準(zhǔn)化的方式處理。”

但多代工廠方法的開(kāi)發(fā)速度還有待觀察。Flex Logix首席執(zhí)行官 Geoff Tate對(duì)生態(tài)系統(tǒng)充滿(mǎn)信心,但表示最初的實(shí)施將主要來(lái)自同一代工廠。“他們將采用不同的KGD方法,機(jī)械規(guī)格將不同,如果多小芯片設(shè)備上有一個(gè),誰(shuí)愿意自己弄清楚問(wèn)題是什么,”他說(shuō)。“很可能小芯片目前只會(huì)在一個(gè)代工廠的生態(tài)系統(tǒng)中使用。臺(tái)積電可能愿意混合來(lái)自多個(gè)工藝節(jié)點(diǎn)的自己設(shè)計(jì)/工藝的小芯片,因?yàn)樗麄兞私饧磳⒌絹?lái)的元素并希望最終客戶(hù)的業(yè)務(wù)。”

Tate補(bǔ)充說(shuō),這一切都不會(huì)在一夜之間發(fā)生。“沒(méi)有一套標(biāo)準(zhǔn)的小芯片可用于標(biāo)準(zhǔn)化接口,”他說(shuō)。沒(méi)有標(biāo)準(zhǔn)化的方法來(lái)測(cè)試和保證 chiplet 的制造可靠性(高溫和低溫測(cè)試已在芯片中得到驗(yàn)證,但正在為 chiplet 開(kāi)發(fā))。沒(méi)有一套經(jīng)過(guò)驗(yàn)證的自動(dòng)化設(shè)計(jì)工具可以將小芯片集成到基板上。沒(méi)有一個(gè)供應(yīng)商生態(tài)系統(tǒng)可以集成來(lái)自多個(gè)供應(yīng)商的小芯片。一個(gè)供應(yīng)商不信任另一個(gè)供應(yīng)商的流程。來(lái)自不同工藝的小芯片將具有不同的熱膨脹系數(shù),從而導(dǎo)致機(jī)械可靠性問(wèn)題/擔(dān)憂。如果組裝好的基板不起作用,誰(shuí)擁有問(wèn)題?在經(jīng)過(guò)驗(yàn)證的生態(tài)系統(tǒng)發(fā)展起來(lái)并且基板成本下降之前,小芯片對(duì)于主流來(lái)說(shuō)是不實(shí)用的,”Tate 補(bǔ)充道。

結(jié)論

小芯片即將到來(lái)。問(wèn)題是小芯片的采購(gòu)速度有多快、范圍有多廣,以及理想的應(yīng)用是什么。

可以肯定的是,設(shè)計(jì)和制造的各種過(guò)程中并沒(méi)有解決所有問(wèn)題,使公司能夠從選項(xiàng)菜單中進(jìn)行選擇,將這些設(shè)備集成到系統(tǒng)中,并確信它會(huì)按預(yù)期工作。這需要時(shí)間。但這個(gè)方向已經(jīng)牢牢確立——并被一些最大的芯片制造商證明是行之有效的——即使尚不清楚半導(dǎo)體行業(yè)的其他公司何時(shí)或如何到達(dá)那里,以及在此過(guò)程中會(huì)遇到什么樣的問(wèn)題。

審核編輯 :李倩

-

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

576瀏覽量

68485 -

生態(tài)系統(tǒng)

+關(guān)注

關(guān)注

0文章

707瀏覽量

21000 -

chiplet

+關(guān)注

關(guān)注

6文章

453瀏覽量

12914

原文標(biāo)題:Chiplet的新競(jìng)賽

文章出處:【微信號(hào):光刻人的世界,微信公眾號(hào):光刻人的世界】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

Chiplet與先進(jìn)封裝設(shè)計(jì)中EDA工具面臨的挑戰(zhàn)

淺談Chiplet與先進(jìn)封裝

Chiplet技術(shù)在消費(fèi)電子領(lǐng)域的應(yīng)用前景

奇異摩爾受邀出席第三屆HiPi Chiplet論壇

Chiplet:芯片良率與可靠性的新保障!

2.5D集成電路的Chiplet布局設(shè)計(jì)

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

Cadence推出基于Arm的系統(tǒng)Chiplet

Chiplet技術(shù)有哪些優(yōu)勢(shì)

2035年Chiplet市場(chǎng)規(guī)模將超4110億美元

IMEC組建汽車(chē)Chiplet聯(lián)盟

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺(tái)

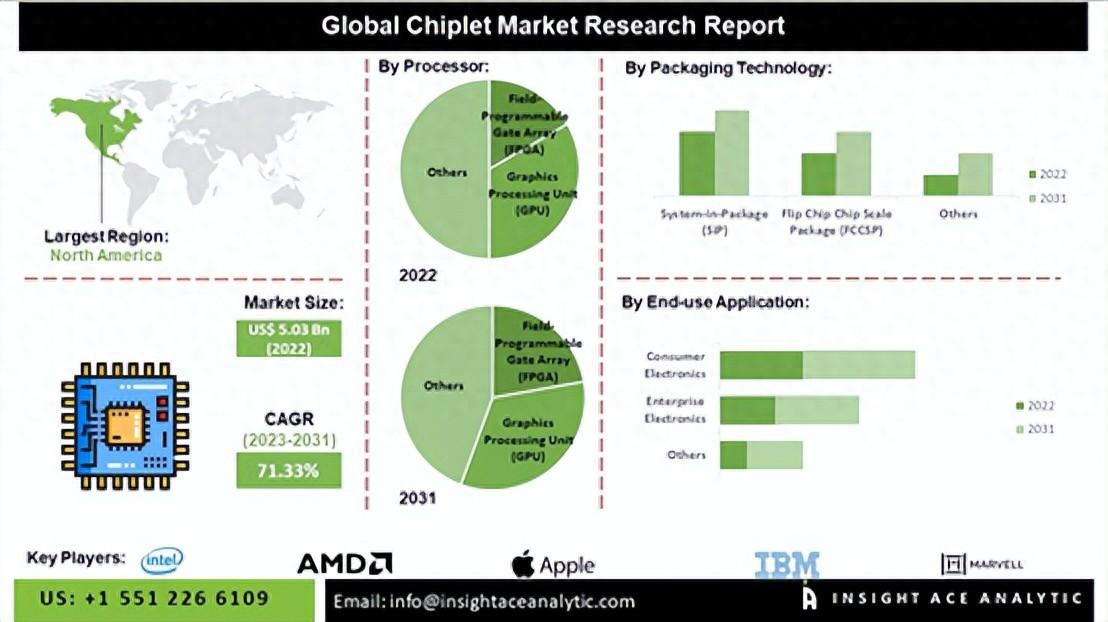

2031年全球Chiplet市場(chǎng)預(yù)測(cè)

Chiplet的新競(jìng)賽

Chiplet的新競(jìng)賽

評(píng)論