在上一篇文章芯片驗證反內卷,搭載ML技術的高級校驗工具讓你躺贏中,我們提到Linting是一項非常重要的技術,多年來也取得了巨大的進步。如今,當代芯片設計所涉及的功能錯誤和設計問題多種多樣,從RTL設計描述中的高風險編碼實踐,到設計投入生產后才會出現的復雜軟硬件交互錯誤,都會對產品質量產生重大影響。

為了避免出現代價昂貴而又費時的設計返工或改版,開發者們不僅需要智能的Linting工具來盡早發現盡可能多的RTL問題,更需要一套預定義的、值得推薦的基礎/高級版本Linting檢查,以備不時之需。這一理念正是新思科技GuideWare方法學的核心。

GuideWare是我們為設計團隊自主研發的一整套規則集,旨在加速完成Lint工作流程,幫助團隊每次都能按時完成設計,而且這套指導規則集已經被業內許多領先的半導體公司所采用。

在本期文章中,我們將深入探討以下幾個問題:

- 在汽車領域,是什么樣的設計挑戰推動了GuideWare的問世和研發?

- 新思科技VC SpyGlass Lint的GuideWare在RTL早期階段能夠發現哪些設計問題,從而避免讓開發者們等到綜合或邏輯等價性檢查階段再進行不必要的迭代?

- 重點介紹幾個可以通過新思科技VC SpyGlass功能Lint分析工具發現的高級問題

GuideWare:一針見血指出問題????????

大家都玩過樂高積木嗎?GuideWare方法學就相當于樂高的底座積木顆粒。通常我們要在開始拼搭結構前先選好底座積木,再選擇用來加強基礎結構的積木。使用GuideWare也是同樣的道理,不同領域的用戶可以在新思科技GuideWare規則集的基礎上修改并建立自己的Lint方法學,利用業界最全面的設計專業知識和最佳實踐知識庫,實現用戶指定的擴展。

當我們有一套可靠的設計方法學后,就相當于有了一個全面的分步Linting檢查流程。客戶在寫完RTL代碼后便可以立即使用。這種含有規則集的方法學文檔可以作為團隊的重要框架,確保他們在整個設計過程中保持風格前后一致,同時還能通過多核技術來加速運行時間。

不同應用的設計需求截然不同,所需的Linting檢查也千差萬別。以符合ISO 26262標準的汽車應用為例,汽車應用設計中需要確保不存在邏輯擁塞或大的多路選擇器或延遲的級數很深等不良做法,通常汽車開發者傾向于采用模塊化、可復用的設計方法學,而新思科技的GuideWare Lint Automotive正好可以滿足這一要求。

新思科技VC Spyglass Lint采用“左移”的識別方法學,能夠提前發現新思科技Design Compiler和Formality在實現流程中讀取設計階段報告的代碼問題。通過使用VC SpyGlass Lint,開發者可在RTL早期階段的等價性檢查中就識別出復雜的驗證問題,從而減少下游階段的迭代。此外,我們還開發了專用規則集來發現仿真與綜合之間的不匹配問題。

超越常規:功能Lint分析

功能驗證的目標是在開發過程中盡早地發現盡可能多的問題。面對棘手的可移植性挑戰,語義和語法檢查一直都起著關鍵作用。

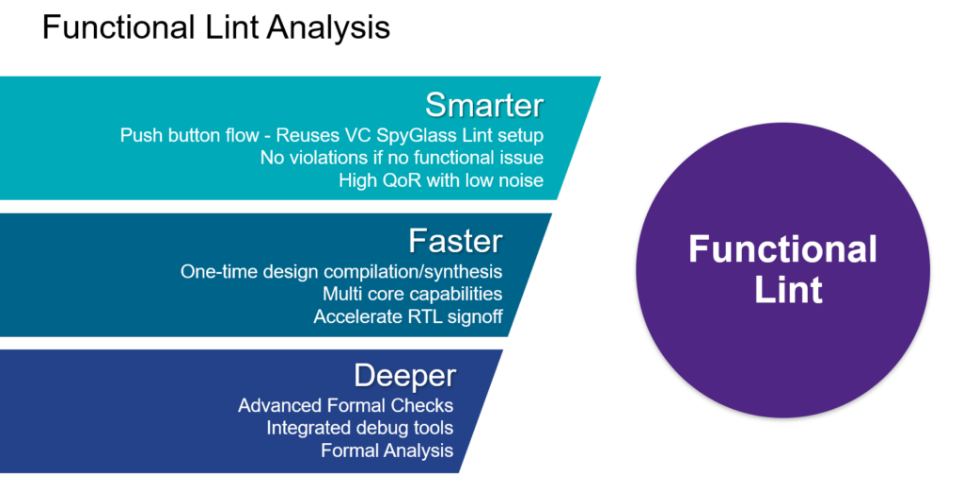

憑借深厚的專業知識和技能,新思科技在傳統Linting方法學的基礎上新增了功能Linting檢查。借助新思科技的VC SpyGlass Lint,開發者能夠以獨特的簡易流程,以更智能、更快速和更深入的方式開展功能Lint分析。用戶無需提供復雜的約束條件,也無需具備形式驗證方面的專業知識,便可利用新思科技的無縫混合流程加速RTL簽核。VC SpyGlass利用VC Formal原生技術,為解決位寬不匹配和越界檢查等RTL設計問題提供了一套綜合、易用、低誤報的方法學,從而實現違例報告更準確的高質量RTL。

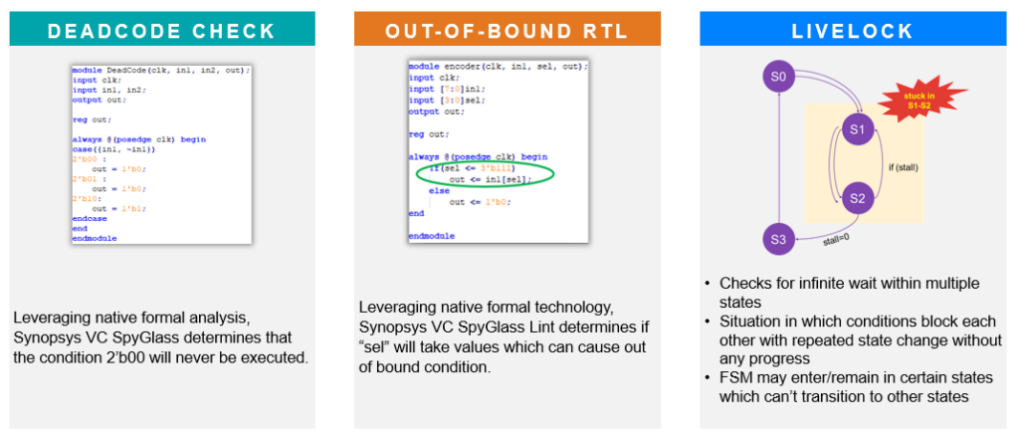

以DeadCode和FSM LiveLock為例,前者是用于識別不會被觸發的RTL代碼的關鍵檢查,后者則是針對多個狀態下無限等待的檢查。它們都無法被傳統的Linting檢查技術識別,因此需要使用新思科技的VC SpyGlass功能Lint技術。此外,簡單的調試功能,如波形查看器和帶有詳細注釋的原理圖查看器,也能進一步縮短驗證時間。代碼復雜性看板報告也能幫助管理團隊預估RTL的復雜性。這些獨特的功能能夠將潛在錯誤盡早暴露給開發者,從而避免它們在下游階段演變成更嚴重的問題。

新一代Linting技術

實現更智能、更快速、更深入的RTL簽核

Linting檢查讓開發者的工作更加輕松、編寫的代碼更加穩健,同時也更適合后續的驗證和實現流程。新思科技始終是Linting檢查技術領域的領導者和踐行者,始終致力于幫助客戶更早發現漏洞和其他設計錯誤。新思科技的VC SpyGlass包含CDC、RDC和Lint技術,作為新一代的RTL簽核平臺,已獲得各大公司的廣泛使用。意法半導體等公司通過使用VC SpyGlass將CDC/RDC的驗證速度最多提高了4倍。

無論是新思科技的GuideWare方法學,還是VC SpyGlass Lint中利用VC Formal原生技術的功能Lint流程,均已成為業界領先的ASIC/SoC公司的基本設計方法學,且已被各大半導體公司所采用。即便是初創的小型芯片設計公司也將VC SpyGlass作為他們的第一選擇并納入其RTL流程。

新思科技與全球排名前20的半導體客戶均有合作,因此我們能夠及時掌握最新行業標準,開發出完備的RTL簽核Linting工具。無論是設計覆蓋的深度,還是適配各種RTL場景和編碼風格的廣度,我們的工具都表現地十分出眾。

未來,我們將剖析在功能檢查中集成機器學習(ML)技術和RCA功能將如何更好地幫助開發者大幅縮短周轉時間,并介紹智能Linting檢查在未來幾年的發展趨勢。

-

新思科技

+關注

關注

5文章

856瀏覽量

51272

原文標題:新一代Linting技術:避免功能錯誤,更快完成芯片設計

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

MediaTek推出新一代Kompanio Ultra處理器

中星微發布最新一代AI芯片“星光智能五號”

新一代光纖涂覆機

比亞迪推出全新一代車規級碳化硅功率芯片

新思科技推出基于AMD芯片的新一代原型驗證系統

芯華章推出新一代高性能FPGA原型驗證系統

國產EDA公司芯華章科技推出新一代高性能FPGA原型驗證系統

先進機器人焊接技術:解析新一代焊接控制模塊的關鍵功能與應用實踐

英偉達新一代AI芯片過熱問題引關注

聯發科新一代天璣旗艦芯片針對谷歌大語言模型Gemini Nano優化

下一代高功能新一代AI加速器(DRP-AI3):10x在高級AI系統高級AI中更快的嵌入處理

雷森受邀參與新一代“車路云未來交通”技術沙龍活動

新一代超聲波清洗技術的優勢與發展前景

新一代Linting技術:避免功能錯誤,更快完成芯片設計

新一代Linting技術:避免功能錯誤,更快完成芯片設計

評論