從音頻輸入到輸出,現有的實時數字音頻系統很難實現低于 1ms 的時延。實際上,200μs 是到目前為止可實現的最佳時延。INSA(法國)的 Emeraude 研究團隊正在開發 Syfala 編譯器,該編譯器結合了 Faust (一種用于實時音頻 DSP 的領域特定語言)和 AMD Vitis HLS,使其為音頻 DSP 用戶提供非常高級的音頻合成工具。

Emeraude 采用基于 AMD Zynq 的FPGA 板卡、低時延音頻編解碼器和 Syfala 編譯器,在眾多簡單的 DSP 程序上實現了 11μs 的低時延。這項新技術適用于聲音合成和主動聲學控制。

01

項目挑戰

實時音頻數字信號處理( DSP )已經在廣泛的計算機架構上實現:采用馮?諾依曼架構的 CPU、多核 CPU、GPU、專用電路、FPGA 等。然而,實現超低時延(即小于1ms)的唯一方法是使用專用電路,如 ASIC 或 FPGA。

盡管如此,對于 DSP 程序員而言,使用 FPGA 幾乎是不可能的事情,因為他們沒有掌握硬件設計技能。

因此,該項目的主要挑戰在于設計出一款工具,允許音頻 DSP 程序員以極低時延(即小于 100μs)在 FPGA 上實現任意音頻 DSP 算法。

02

解決方案

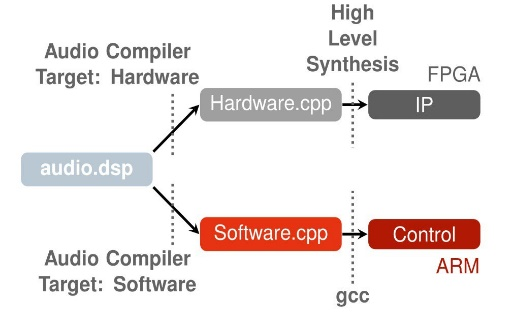

采用的解決方案是將音頻 DSP 語言編譯器(即 Faust)的輸出與 HLS 工具 Vitis HLS連接起來。Faust 編譯器不僅可處理軟硬件分區,而且還可隔離將在 FPGA 上實施的內核 DSP 算法,如圖 1 所示。

圖 1:從 Faust 程序到 FPGA 的 Syfala 編譯流程

Vitis HLS 用于實現該內核 DSP 的硬件,允許訪問外部 DDR 內存以及使用 ARM Zynq 處理系統驅動程序的硬件控制器。

INSA-LYON 的研究團隊主管 Tanguy Risset 表示:“Vitis HLS 允許我們直接重復使用 Faust 編譯器生成的 C++ 代碼,因此從 Faust 高級規范直至 FPGA 比特流都無需經歷手動設計流程。此外,Vitis HLS 與 AMD 的設計流程能夠很好地集成在一起,方便我們進行硬件/軟件的協同設計。”

03

設計成效

最終成效就是獲得一個新的編譯流程,可將任意音頻 DSP 程序自動編譯到基于 AMD Zynq 7000 的 FPGA 板卡(如 Digilent Zybo 或 Genesys)上。這樣一來,從模擬輸入到模擬輸出,所實現的程序的時延可低至 11μs。如此短的時延是前所未有的。該編譯器是開源的,目前用于實現主動聲學控制算法和 3D 音頻編解碼流程。

Risset 補充道:“Vitis HLS 使我們能夠精確控制 IP 的時延。特別是 Vitis HLS 能夠生成一個有一個樣本延遲時延的 IP。這對于實現我們在模擬與模擬之間實現的時延極為重要。”

Risset 表示,Vitis HLS IP 的調度視圖有助于我們了解 Vitis HLS 是如何引導并行化,以及內存訪問是如何對 IP 時延產生影響的。他補充道:“這促使我們在 Faust 生成的 C++ 代碼中對內存訪問進行優化,這是實現低時延的必要步驟。”

審核編輯:劉清

-

dsp

+關注

關注

556文章

8155瀏覽量

356696 -

FPGA

+關注

關注

1645文章

22021瀏覽量

617324 -

編解碼器

+關注

關注

0文章

273瀏覽量

24727 -

編譯器

+關注

關注

1文章

1661瀏覽量

50116 -

HLS

+關注

關注

1文章

133瀏覽量

24790

原文標題:Zynq 及 Vitis HLS 助力面向聲音合成和聲學控制的低時延技術

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

如何在Unified IDE中創建視覺庫HLS組件

使用AMD Vitis Unified IDE創建HLS組件

如何使用AMD Vitis HLS創建HLS IP

Actran聲學仿真解決方案:工業級聲學預測與優化的專業技術平臺

正點原子Z15I ZYNQ 開發板資料發布!板載PCIe2.0、SPFx2、MIPI CSI等接口,資料豐富!

正點原子Z20 ZYNQ 開發板發布!板載FMC LPC、LVDS LCD和WIFI&藍牙等接口,資料豐富!

聲學技術如何重構人機交互生態

zynq通過什么接口去控制DLP?

使用AMD Vitis進行嵌入式設計開發用戶指南

Zynq及Vitis HLS助力面向聲音合成和聲學控制的低時延技術

Zynq及Vitis HLS助力面向聲音合成和聲學控制的低時延技術

評論