在SpinalHDL中使用之前已有的Verilog等代碼的時(shí)候需要將這些代碼包在一個(gè)BlackBox里面,但是如果這些代碼里面有時(shí)鐘和復(fù)位,我們需要怎么將時(shí)鐘和復(fù)位端口和SpinalHDL中已有的時(shí)鐘域連接起來(lái)呢?

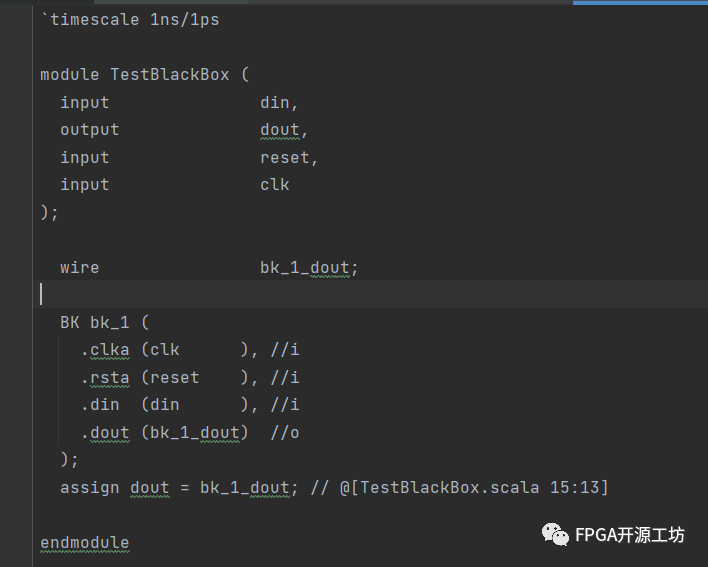

當(dāng)BlackBox中只有一個(gè)時(shí)鐘的時(shí)候可以直接使用mapClockDomain完成時(shí)鐘信號(hào)和復(fù)位信號(hào)的賦值。在mapClockDomain中如果沒(méi)有指定時(shí)鐘域的話(huà)就采用的是默認(rèn)時(shí)鐘域。

import spinal.core._ import spinal.lib._ class BK extends BlackBox{ val clka = in Bool() val rsta = in Bool() val din = in Bool() val dout = out Bool() mapClockDomain(clock = clka, reset = rsta) } class TestBlackBox extends Component { val din = in Bool() val dout = out Bool() val bk = new BK bk.din <> din bk.dout <> dout } object TestBlackBox extends App{ SpinalVerilog(new TestBlackBox) }

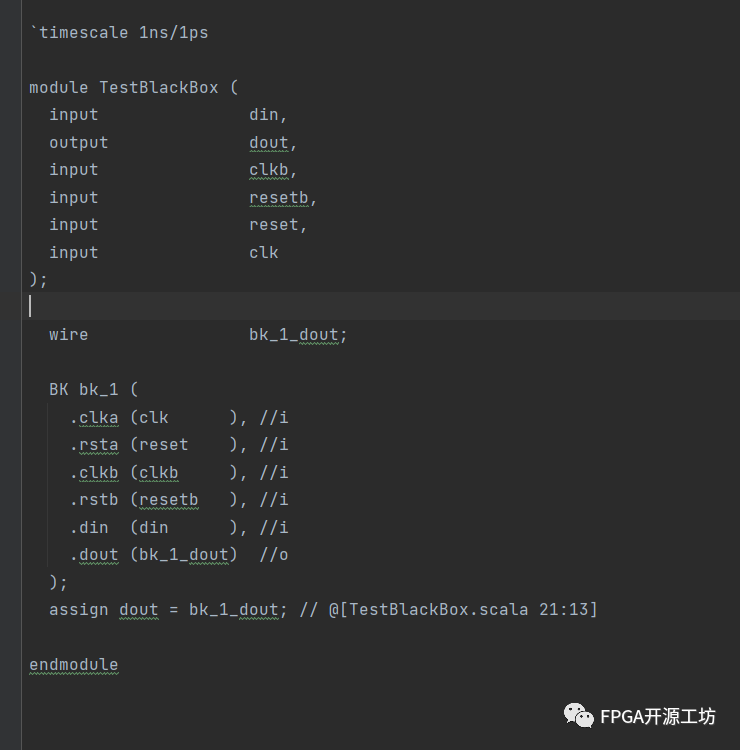

當(dāng)有兩個(gè)時(shí)鐘域的時(shí)候,就需要把時(shí)鐘域給指定一下了,在下面代碼中將時(shí)鐘域通過(guò)參數(shù)的方式傳了進(jìn)來(lái)。

import spinal.core._

import spinal.lib._

class BK(clockDomaina: ClockDomain, clockDomainb: ClockDomain) extends BlackBox{

val clka = in Bool()

val rsta = in Bool()

val clkb = in Bool()

val rstb = in Bool()

val din = in Bool()

val dout = out Bool()

mapClockDomain(clockDomaina,clock = clka, reset = rsta)

mapClockDomain(clockDomainb,clock = clkb, reset = rstb)

}

class TestBlackBox extends Component {

val din = in Bool()

val dout = out Bool()

val clkb = in Bool()

val resetb = in Bool()

val clockDomainb = ClockDomain(clock = clkb,reset = resetb)

val bk = new BK(this.clockDomain,clockDomainb)//默認(rèn)時(shí)鐘域和新建的時(shí)鐘域b

bk.din <> din

bk.dout <> dout

}

object TestBlackBox extends App{

SpinalVerilog(new TestBlackBox)

}

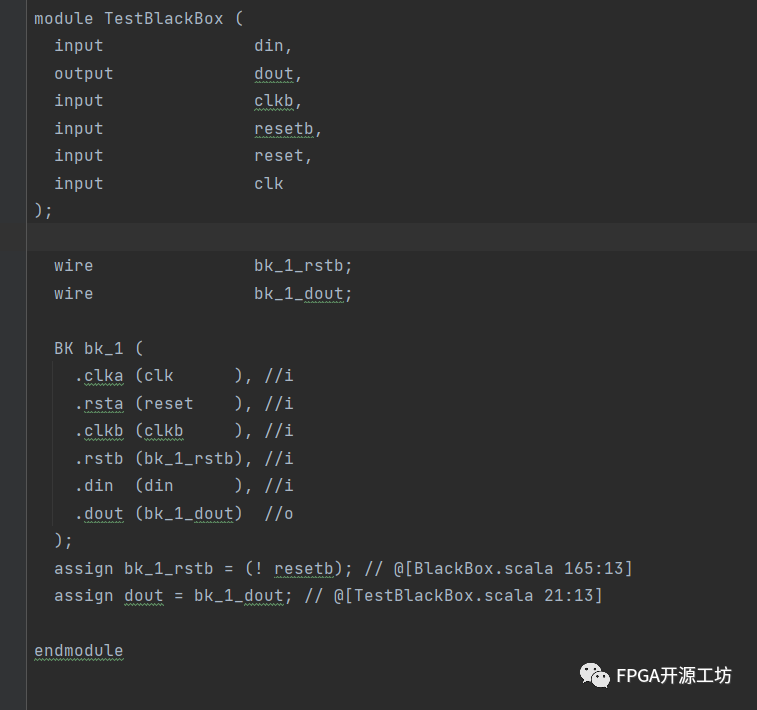

因?yàn)樵赟pinalHDL中默認(rèn)時(shí)鐘域是高復(fù)位的,但是我們已有的IP可能是低復(fù)位的,這個(gè)時(shí)候就需要在mapClockDomain中指定一下復(fù)位信號(hào)是HIGH還是LOW。在下面代碼中就將時(shí)鐘域b下面的復(fù)位指定為低復(fù)位。

import spinal.core._

import spinal.lib._

class BK(clockDomaina: ClockDomain, clockDomainb: ClockDomain) extends BlackBox{

val clka = in Bool()

val rsta = in Bool()

val clkb = in Bool()

val rstb = in Bool()

val din = in Bool()

val dout = out Bool()

mapClockDomain(clockDomaina,clock = clka, reset = rsta)

mapClockDomain(clockDomainb,clock = clkb, reset = rstb, resetActiveLevel = LOW)

}

class TestBlackBox extends Component {

val din = in Bool()

val dout = out Bool()

val clkb = in Bool()

val resetb = in Bool()

val clockDomainb = ClockDomain(clock = clkb,reset = resetb)

val bk = new BK(this.clockDomain,clockDomainb)

bk.din <> din

bk.dout <> dout

}

object TestBlackBox extends App{

SpinalVerilog(new TestBlackBox)

}

以上三種情況應(yīng)該足夠應(yīng)對(duì)一般情況下BlackBox的時(shí)鐘域的賦值了。

審核編輯:湯梓紅

-

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111916 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1886瀏覽量

132901 -

HDL

+關(guān)注

關(guān)注

8文章

330瀏覽量

47849 -

復(fù)位

+關(guān)注

關(guān)注

0文章

179瀏覽量

24586 -

時(shí)鐘信號(hào)

+關(guān)注

關(guān)注

4文章

466瀏覽量

29110

原文標(biāo)題:SpinalHDL BlackBox時(shí)鐘與復(fù)位

文章出處:【微信號(hào):FPGA開(kāi)源工坊,微信公眾號(hào):FPGA開(kāi)源工坊】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

在SpinalHDL里實(shí)現(xiàn)優(yōu)雅的添加待跟蹤波形信號(hào)

在SpinalHDL的設(shè)計(jì)中集成現(xiàn)有RTL設(shè)計(jì)(IP)的渠道——BlackBox

關(guān)于SpinalHDL仿真中信號(hào)驅(qū)動(dòng)那點(diǎn)事兒

聊一聊SpinalHDL 1.6.1引入的blackbox inline功能

談?wù)?b class='flag-5'>SpinalHDL中StreamCCByToggle組件設(shè)計(jì)不足的地方

如何在SpinalHDL里啟動(dòng)一個(gè)仿真

記錄一個(gè)在使用BlackBox中parameter踩到的坑

SpinalHDL設(shè)計(jì)錯(cuò)誤總結(jié)相關(guān)資料分享

SpinalHDL里時(shí)鐘域中的定制與命名

STM32電源管理、復(fù)位、時(shí)鐘

SpinalHDL里用于跨時(shí)鐘域處理的一些手段方法

原來(lái)SpinalHDL中BlackBox封裝數(shù)組接口如此簡(jiǎn)單

SpinalHDL BlackBox時(shí)鐘與復(fù)位

SpinalHDL BlackBox時(shí)鐘與復(fù)位

評(píng)論