晶圓鍵合技術正得到越來越多的關注。

先進封裝大概可以分為兩大類趨勢:一個是小芯片(chiplet)。

小芯片將傳統上較大型的集成電路分拆成許多較小的功能模組,先個別予以優化,再使用這些已優化的小芯片組織新的次系統。這樣可以重復使用IP,大幅加速產品設計的速度以及降低設計成本。

至于各個小芯片之間的連接,依靠底下中介層(interposer)內的金屬連線。此連線的密度當然遠高于傳統的線路板或封裝I/O所能支援的密度,大幅增加線路運作頻寬(bandwidth)、增大平行運算的操作空間。

另一個方向自然是異構集成(heterogeneous integration)。

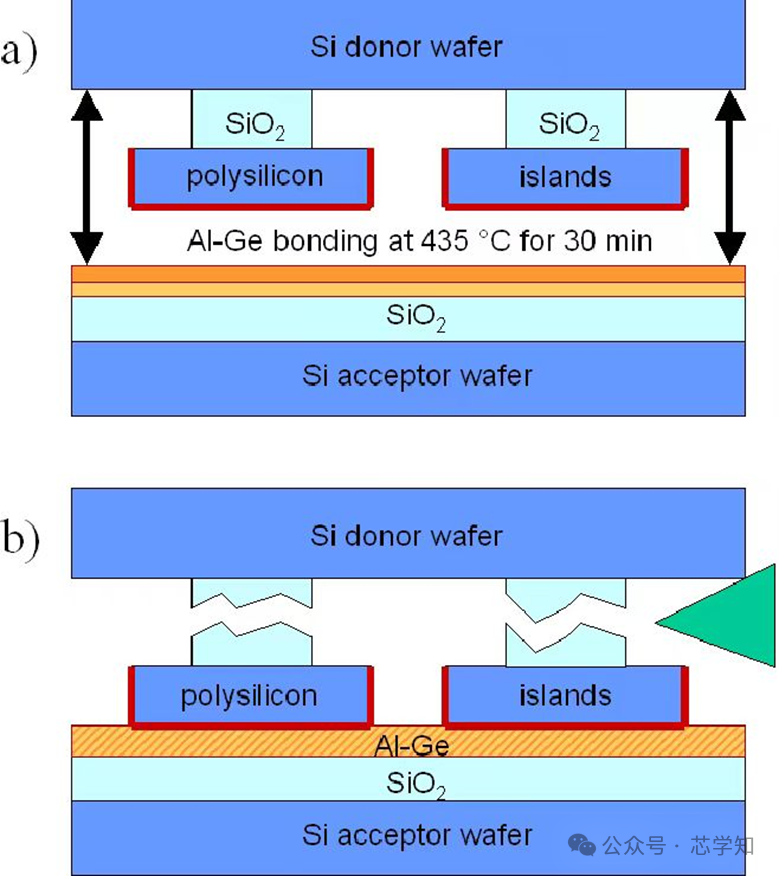

將不同制程或不同材料的芯片堆疊在一起,以整合方式提升、擴充組裝元件的功能。除了已經商業化的方法外,基本上有芯片-晶圓(Chip-on-Wafer;CoW)及晶圓-晶圓(Wafer-on-Wafer;WoW)等兩種鍵合形態。二者在鍵合后都需要再切割晶粒,但是也有例外。CoW程序較復雜,所以WoW可能早些普及。

晶圓間鍵合的技術又有很多種,現在已經進入商業化的技術之一是“銅-銅混合鍵合”(Cu-Cu hybrid bonding),這也是本文討論的主題。

銅-銅混合鍵合技術是將兩片欲鍵合在一起的晶圓,各自完成制程最后一步的金屬連線層,此層上只有兩種材質:銅及介電質。介電質可以是氧化硅或高分子材料,二者各有優缺點,使用何種物質依制程需要而定。由于晶圓鍵合時牽涉到銅及介電質兩種材料介面,所以稱之為混合鍵合。

兩片晶圓面對面鍵合時是銅金屬對銅金屬、介電值對介電質,兩邊鍵合介面的形狀、位置完全相同,晶粒大小形狀也必須一樣。所以使用混合鍵合先進封裝技術的次系統產品各成分元件必須從產品設計、線路設計時就開始共同協作。

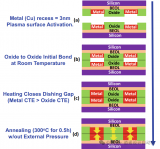

混合鍵合制造約略如下:兩邊晶圓在完成最上層的金屬制造后,經化學機械研磨(Chemical-Mechanical Polishing;CMP)及清洗后,兩片晶圓面對面對齊(alignment)。介電質先經離子活化(ion activation),兩邊介電質接觸后產生共價鍵。兩邊銅的表面原先較介電質稍低,在退火(annealing)時因膨脹系數較介電質為大而增高接合,兩邊銅離子因相互擴散(diffusion)進入對方而形成密切的永久性接合。

晶圓平坦化(planarization)不足、殘留粒子、對齊誤差及金屬介面孔隙(void)等均有可能影響元件特性或失效。

目前混合鍵合機臺已有多家設備廠商投入量產。如EVG、SUSS MicroTech、TEL、AML等,典型機臺如EVG的Gimini系列。由于現代設備廠商在銷售機臺時多附有機臺相關之基礎制程,混合鍵合制程的開發通常不算是嚴峻的挑戰。

目前銅混合鍵合的封裝制程良率已經可以到達一般后段封裝的典型良率99%以上。一部分原因是于此技術的累積發展與已經商業化的機臺設備同步,但是更重要的原因是兩邊芯片的設計團隊期前的設計溝通,在重復單元區留下適度的冗余(redundancy),當鍵合時發生缺陷時,有足夠的空間來使用。

混合鍵合的最大特色是芯片對外連接金屬墊(metal pad)的尺度是“半導體制程級”的。相較于之前用于中介板的微凸塊(microbump)間距40um,混合鍵合的鍵合間距可以小達1~2um,限制尺寸的原因主要來自于對齊的精確程度,還有進一步改善的空間。

這樣的鍵合間距代表每平方公分芯片面積可以承擔百萬個連接,這比任何既存的封裝方式都有幾個數量級的提升。

連線鍵合數目愈多意味著兩個芯片之間容許更高頻寬的溝通,有利于平行運算,也容許較高電流。功能模組之間的連線也較尋常方式更短,所以速度快、噪音低、功耗也較小。另外混合鍵合本來就是異構集成、3D堆疊先進封裝中的一種方法,所以二者的優點也自然都有。

商業應用混合鍵合的半導體產品,首先是Sony的CIS。CIS有幾個組成部分:畫素陣列(pixel array)、類比數位轉換器(Analog-to-Digital Converter;ADC)、影像訊號處理器(Image Signal Processor;ISP)。畫素陣列基本上是1層多晶硅(polysilicon)與5層金屬的制造;ADC與ISP則是1層多晶硅與10層金屬的制程,二者的制程差距甚遠,符合“異質”特征,應該分別制造。二者的3D芯片堆疊還能縮小鏡頭尺寸,所以Sony早在2016年就將分別制造的畫素陣列晶圓與ADC+ISP晶圓混合鍵合,替代原來在同一芯片的設計制造。

由于混合鍵合大幅增加金屬連線密度,使得ADC可以平行處理畫素,大幅提升畫面處理的能力,譬如全域快門(global shutter)、影片的每秒幀數(frame per second)等。目前的設計趨勢是向每個畫素都有獨立的ADC方向邁進。

進一步的工作是將DRAM也加入CIS的3D堆疊,做為畫素處理的緩沖存儲器(buffer memory)。Sony和三星電子(Samsung Electronics)都有此設計,只是DRAM堆疊位置不一。影像在車輛的應用,譬如用來偵測前方物體距離的時差測距(Time of Flight;ToF)的單光子雪崩探測器(Single Photon Avalanche Detector;SPAD);或在工業的應用,譬如機器視覺(machine vision),都可能需要再加入能執行邊緣計算(edge computing)芯片。CIS啟動混合鍵合的商業應用,歷史較長,較長遠的應用規劃也漸入視野。

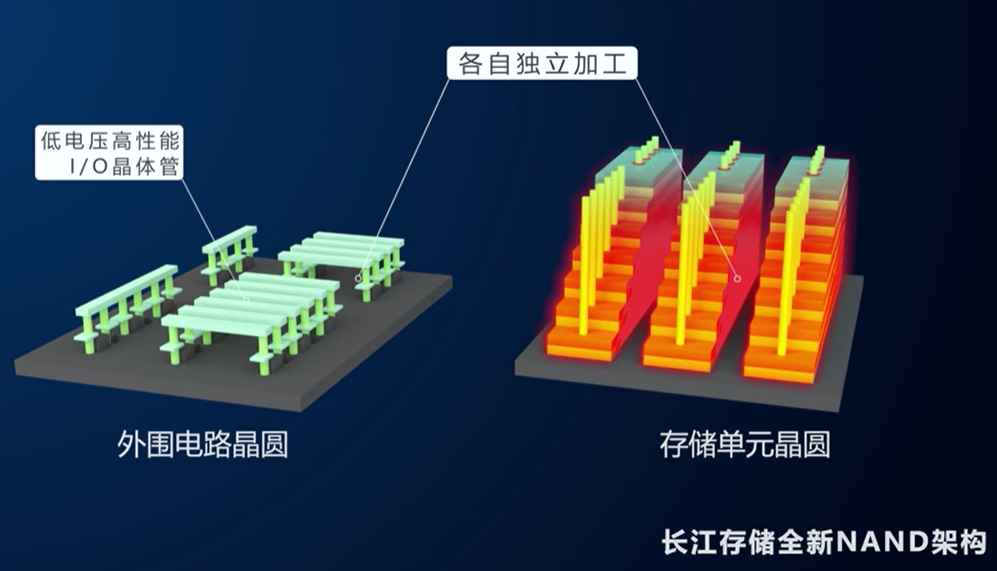

另外一個也進入商業量產的應用是3D NAND。平面NAND的存儲器細胞陣列(memory cell array)與其他邏輯線路-包括微控制器(microcontroller)、位址寄存器(address register)等,是放在同一芯片上的。

3D NAND 的存儲器細胞陣列持續往3D方向堆疊,但是邏輯線路上方卻空無一物,嚴重浪費珍貴的芯片內部空間(real estate)。

所以長江儲存首先以XtackingTM技術將邏輯線路部分以混合金鍵合方式置于存儲器細胞陣列之下,大幅提高芯片內部面積使用效率。其他公司后來也采取類似方法。不過在此例中,金屬墊的密度不需要特別地高。

混合鍵合技術的新應用中,最引人注目的當屬高效能計算(High Performance Computing;HPC)。HPC在晶圓代工的產能中占據最顯著的分量。

HPC架構主體主要含處理器和存儲器。處理器通常以最先進的邏輯制程制造,但是存儲器(DRAM)的制程進展較邏輯制程緩慢,這個就產生落差。

兩者之間溝通落差限制整體表現,而且制程也截然不同,屬于“異質”。

解決兩者之間效能落差的方法之一是利用平行處理。現在的處理器通常具有多個數量的內核(cores),每個內核需要支援其運作的個別存儲器。數量如此多的內核-存儲器之間的連線需要多個I/O節點以及高頻寬,這就是十年前開始出現高頻寬存儲器(High Bandwidth Memory;HBM)需求的驅動原因。

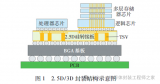

HBM是用2.5D封裝技術將CPU與超過8個DRAM堆疊封裝,其處理器與存儲器之間的連接是透過芯片的微鍵(microbond)連接底下中介層的金屬線至另外的芯片,如此一來I/O與連線的密度都可以大幅增加。

對于常用于AI常用的GPU芯片,其內核的功能比較專一,所以每個內核的面積較小,一個芯片里內核的數目動輒上千。每個內核所需要對應存儲器容量不需要很大,但是因為內核與存儲器的數目有數量級的提升,連線及I/O的數目要求更高,此時銅混合鍵合就能提供其所需要的效能。

這個應用也是目前多家代工廠、DRAM廠的技術及業務能力擴展方向。

2022年3月Graphcore發布于臺積電造的Bow IPU號稱是世界第一個3D WoW處理器,利用到的是混合鍵合的另一種優勢。兩片晶圓一邊是AI處理器及其協作的存儲器,主要包括1,47兩個IPU(Intelligent Processor Unit,Graphcore為其處理器的命名)以及與各IPU協作的獨立900MB的分散式SRAM;另一個芯片負責提供電源。如此結構設計,Graphcore宣稱可以提升效能40%以及節省功耗16%。

AMD最近的Ryzen系列也因為不同的原因采取混合鍵合技術,雖然使用的是CoW的技術,而非WoW。AMD將CPU中面積較大的L3 cache單獨拿出并擴增容量、單獨生產,在不增加CPU系統面積的情況下,增加可用的SRAM容量,減少一般數據處理必須傳送到DRAM的需求,因而提升速度、減少功耗。

其他混合鍵合的應用現在可預見的還包括無線通信、AIoT、PMIC等。在混合鍵合的制造成本下降后,應用領域還有可能延拓得更廣泛。從芯片異質整合、效能提升、減少功耗、縮小面積等的幾個優點考量,只要混合鍵合的成本下降至各優點的價值臨界點后,技術的采用將會一一浮現。學習已經商業化的、正在醞釀中的應用并且分析其得失,是尋找新應用的必要學習過程。

晶圓鍵合是近十幾年快速發展起來的新興半導體加工技術,在MEMS,CIS和存儲芯片等領域有著重要的應用,得到越來越多的關注。

審核編輯 :李倩

-

處理器

+關注

關注

68文章

19740瀏覽量

232852 -

芯片

+關注

關注

459文章

51927瀏覽量

433665 -

晶圓

+關注

關注

52文章

5078瀏覽量

129007

原文標題:銅混合鍵合的發展與應用

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

銅線鍵合IMC生長分析

閃存沖擊400層+,混合鍵合技術傳來消息

混合鍵合中的銅連接:或成摩爾定律救星

三維堆疊封裝新突破:混合鍵合技術揭秘!

銅混合鍵合的發展與應用

銅混合鍵合的發展與應用

評論