設計碼完代碼后,有時候想簡單調試一下基本的通路,此時還沒有驗證資源進來,可以仿照modesim仿真的方法,創建一個.v/.sv的頂層,里面例化DUT,里面加預期激勵;

下面是VCS/XRUN兩種仿真工具最簡單的demo,spi_slv.v是待測dut,tb_top.sv為頂層top,例化dut, 里面添加對應的激勵;

1.VCSdemo:

步驟一:c bash下設置工具對應的環境變量(如果已經設置好,則忽略)

|

setenvNOVAS_HOME $ENVDIR/apps/synopsys/verdi/2017.03 setenvVERDI_HOME $ENVDIR/apps/synopsys/verdi/2017.03 setenvLD_LIBRARY_PATH$VERDI_HOME/share/PLI/lib/LINUX64:$VERDI_HOME/share/PLI/IUS/LINUX64/boot:$LD_LIBRARY_PATH |

步驟二:編譯運行對應的.v/.sv 文件 + dumpfsdb所需要的pli

| vcs -full64 -R spi_master.v tb_top.sv +time_scale=1ns -debug_pp -LDFLAGS -rdynamic-P ${NOVAS_HOME}/share/PLI/VCS/LINUX64/novas.tab |

步驟三:例化頂層,添加fsdb dump 的系統函數, 添加激勵

|

moduletb_top; wire SDO; wire SDI; wireSCLK; wireCS; spi_slv m_spi( .CS(CS), .SDO(SDI), .SDI(SDO), .SCLK(SCLK) ); initial begin #10000;// simulation time //TODO ADD code here $finish(); end initial begin $fsdbDumpfile("test.fsdb"); $fsdbDumpvars(0,tb_top); end endmodule |

步驟四:打開波形: verdi -f filelist.f -ssf test.fsdb

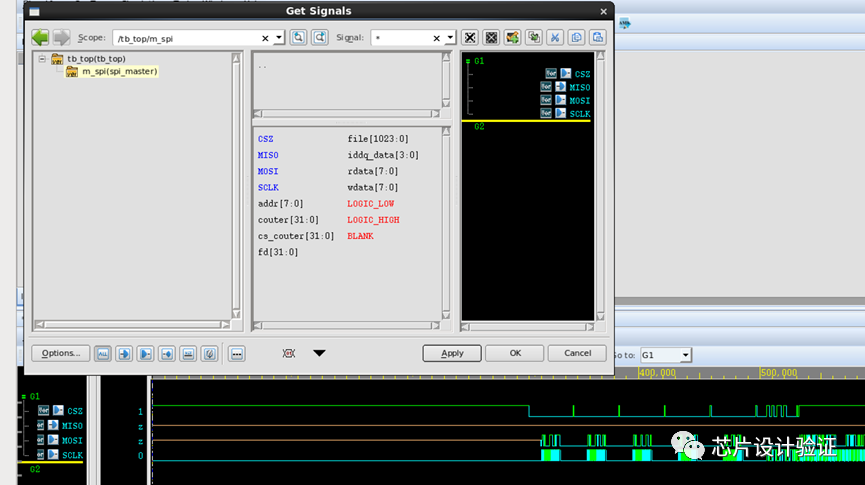

波形效果如下

2.XRUN demo:

步驟一:設置運行XRUN工具對應的環境變量

| 略 |

步驟二:編譯運行對應的.v/.sv 文件 + dump shm 波形

| xrun-sv-c-elaboratespi_master.vtb_top.sv-accessrwc&&xrun-R-inputwave_dump.tcl |

wave_dump.tcl 文件:

|

database-open waves -into test.shm -default -event probetb_top -all -dynamic -depth all -tasks -functions -all -memories -variablestb_top run exit |

步驟三:例化頂層,添加激勵

|

moduletb_top; wireSDO; wireSDI; wire SCLK; wireCS; spi_slv m_spi( .CS(CS), .SDO(SDI), .SDI(SDO), .SCLK(SCLK) ); initial begin #10000; //TODO ADD code here $finish(); end endmodule |

步驟四:打開波形:simvision test.shm

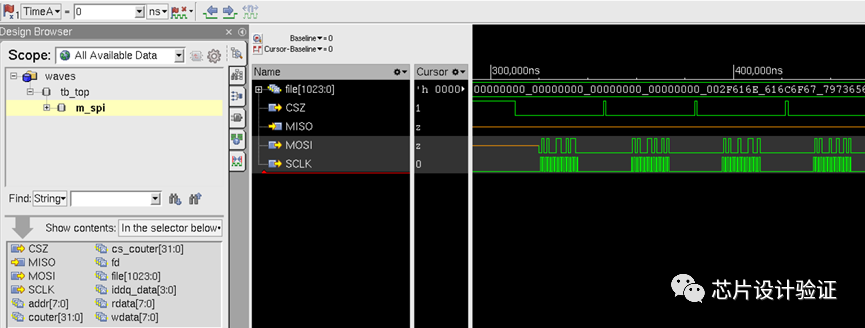

波形效果如下:

審核編輯:湯梓紅

-

仿真

+關注

關注

51文章

4192瀏覽量

134941 -

UVM

+關注

關注

0文章

182瀏覽量

19343 -

VCS

+關注

關注

0文章

80瀏覽量

9782 -

編譯

+關注

關注

0文章

672瀏覽量

33460 -

仿真環境

+關注

關注

0文章

4瀏覽量

5285

原文標題:VCS/XRUN如何創建一個非UVM的簡單仿真環境?

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

vcs和xrun搭配uvm1.1/uvm1.2版本庫的使用情況

IC驗證之UVM常用宏匯總分析(四)

IC驗證"一個簡單的UVM驗證平臺"是如何搭建的(六)

數字IC驗證之“搭建一個可以運行的uvm測試平臺”(5)連載中...

請問一下在UVM中的UVMsequences是什么意思啊

使用VCS仿真Vivado IP核時遇到的問題及解決方案

淺談VCS的兩種仿真flow

VCS獨立仿真Vivado IP核的一些方法總結

VCS/XRUN如何創建一個非UVM的簡單仿真環境?

VCS/XRUN如何創建一個非UVM的簡單仿真環境?

評論