引言:上一篇文章我們介紹了通過添加電阻器、場效應晶體管(FET)開關、電平轉換器甚至其他Xilinx FPGA等選項實現HP Bank IO與2.5V/3.3V外設對接的方法。本文介紹利用TI公司TXS0108實現FPGA IO Bank接不同外設IO接口電壓轉換。

FPGA與LVDS ADC外設互聯

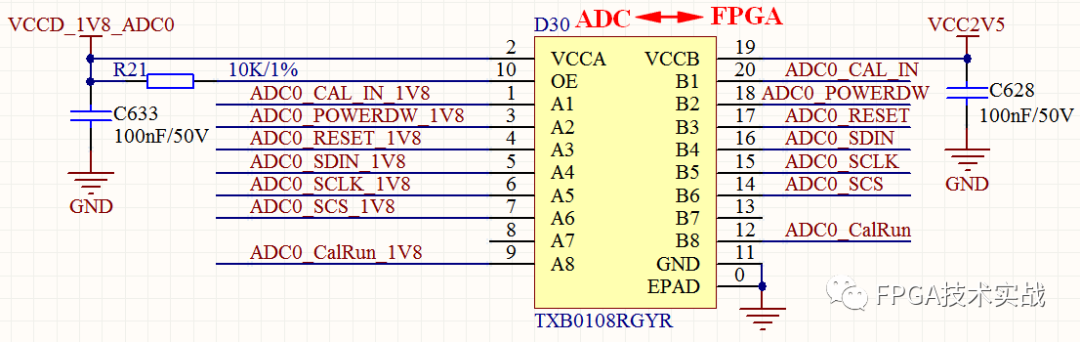

項目設計中采用了兩片高速并行LVDS ADC,單片ADC差分對有36對,采樣速率最大3Gbps,ADC與K7 FPGA的HR Bank互聯。由于Xilinx 7系列FPGA HR Bank的LVDS電平供電VCCO為2.5V,而ADC SPI控制接口電平為1.8V,此時,ADC數據輸出LVDS接口可以直接與FPGA互聯,而1.8V的SPI接口需要進行電平轉換才可與該BANK互聯。設計采用TI公司TXS0108芯片實現IO電平轉換。

圖1:采用TI公司TXS0108芯片實現ADC SPI IO電平轉換

2. FPGA與QSPI Flash外設互聯

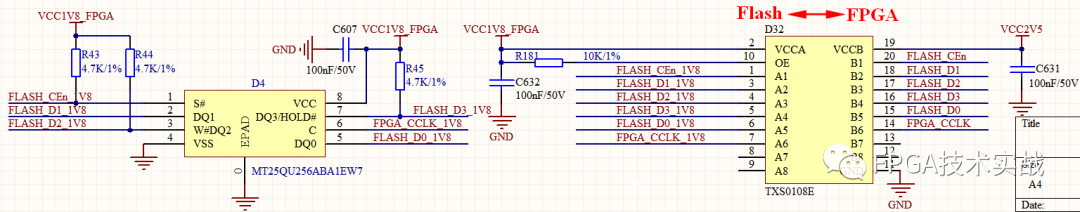

項目中選擇的QSPI Flash為MT25QU256ABA1EW7,供電電壓1.8V,由于FPGA專用Flash接口IO Bank由于其他外設原因VCCIO需要采用2.5V供電,此時同樣也需要考慮電平兼容問題,具體設計如下圖所示。

圖2:采用TI公司TXS0108芯片實現Flash IO電平轉換

3.需要注意的問題

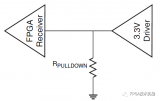

由于TXS0108或同類型器件的特點,該器件具有自動識別轉換方向的特點,無需控制信號方向。但該器件的缺點是具有非常弱的驅動能力,uA級別。如果線路上存在終端或其他重負載,可能會導致邏輯故障。終端和總線負載必須大于50 kΩ 以避免邏輯中斷。因此,I2C和1Wire等開漏總線與這種類型的電平轉換器不兼容。

-

FPGA

+關注

關注

1643文章

21983瀏覽量

614621 -

接口

+關注

關注

33文章

8961瀏覽量

153281 -

adc

+關注

關注

99文章

6650瀏覽量

548386

原文標題:利用TI公司TXS0108實現FPGA IO Bank接不同外設IO接口電壓案例

文章出處:【微信號:FPGA技術實戰,微信公眾號:FPGA技術實戰】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

用FPGA配置lmk04616,如果用電平轉換連接lmk04616的spi數字接口1.8V管腳,用什么轉換器合適?

ADC3663的SPI配置管腳連接至FPGA時遇到IO電平不匹配怎么解決?

TXS0108用于板間接口互連時輸出端出現震蕩

TXS0108E 8 位雙向電壓電平轉換器,適用于漏極開路和推挽應用

TXS0108E-Q1 TXS0108E-Q1 適用于漏極開路應用的 8 位雙向電壓電平轉換器

使用IO口檢測電源電壓的轉換邏輯

TXS0108雙向電平轉換芯片用于IIC時的問題

FPGA 結構分析 -IO 資源

Xilinx 7系列FPGA高性能接口與2.5V/3.3V外設IO接口設計

基于TXS0108實現FPGA IO Bank接不同外設IO接口電壓轉換

基于TXS0108實現FPGA IO Bank接不同外設IO接口電壓轉換

評論