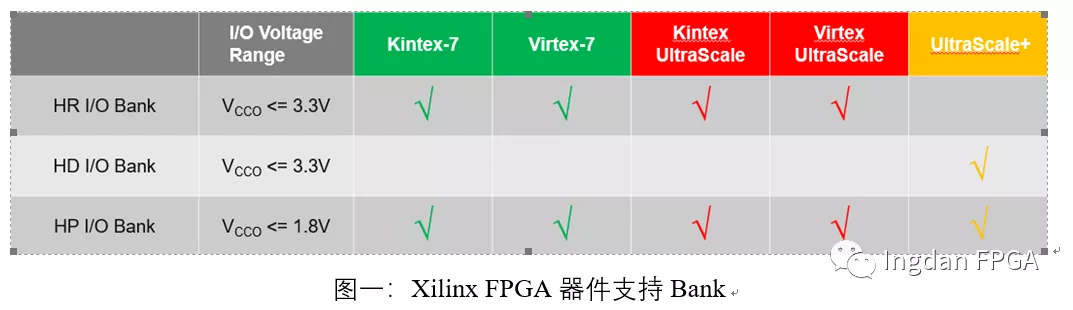

引言:Xilinx 7系列FPGA IO Bank分為HP Bank和HR Bank,HP IO接口電壓范圍為1.2V~1.8V,可以實(shí)現(xiàn)高性能,HR IO接口電壓范圍為1.2V~3.3V。當(dāng)HR Bank與2.5V或者3.3V外設(shè)互聯(lián)時(shí),需要考慮接口電平的兼容性。

根據(jù)性能需求、功能和信號(hào)類型(輸入、輸出或雙向),有不同的接口設(shè)計(jì)選項(xiàng)。本應(yīng)用說明探討諸如添加電阻器、場(chǎng)效應(yīng)晶體管(FET)開關(guān)、電平轉(zhuǎn)換器甚至其他Xilinx FPGA等選項(xiàng)。

1. 電阻分壓設(shè)計(jì)

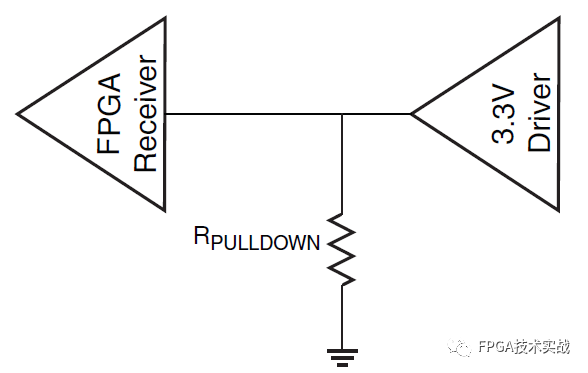

????一個(gè)簡(jiǎn)單的電阻負(fù)載可以將過多的信號(hào)擺動(dòng)截?cái)嗟紽PGA的可容忍水平。如圖1所示,通過從傳輸線到GND放置電阻器,只有驅(qū)動(dòng)高壓被衰減。這種解決方案可能導(dǎo)致信號(hào)完整性低于理想,因?yàn)橄吕娮杵魍ǔ2慌c傳輸線匹配。將該下拉電阻器放置在接收器附近有助于減少不必要的反射。

圖1:下拉電阻技術(shù) ????

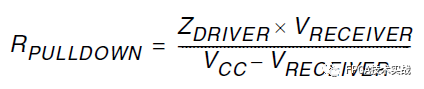

下拉電阻器可以通過知道輸出驅(qū)動(dòng)器阻抗/電阻和輸出驅(qū)動(dòng)電壓(VCC)來確定。在所需的接收器輸入電壓定義為VRECEIVER的情況下,下拉電阻器使用等式1以及圖2的有效示意圖進(jìn)行計(jì)算。

圖2:帶下拉電阻器的驅(qū)動(dòng)器驅(qū)動(dòng)邏輯1的有效示意圖

帶下拉電阻器的驅(qū)動(dòng)器驅(qū)動(dòng)邏輯1的有效示意圖

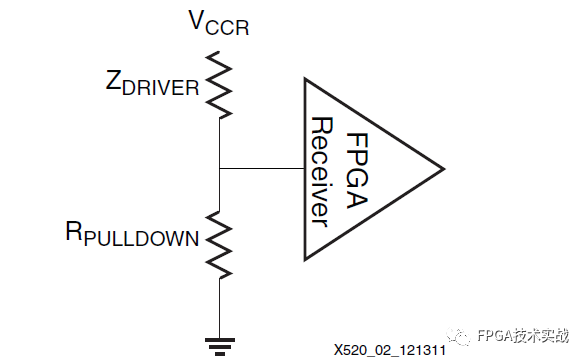

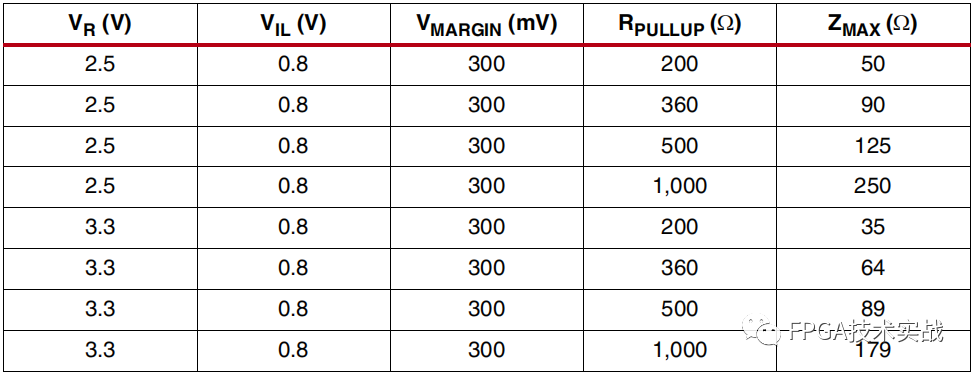

表1顯示了不同驅(qū)動(dòng)器阻抗/電阻上2.5V和3.3V驅(qū)動(dòng)器VCC的RPULLDOWN計(jì)算值。

表1:RPULLDOWN的計(jì)算值

????由于驅(qū)動(dòng)器的潛在非線性,建議通過HSPICE進(jìn)行模擬以將非線性考慮在內(nèi)。此外,由于阻抗不匹配,必須考慮過沖和反射。HP I/O組的VCCOMAX為2.1V。

2. 圖騰柱電阻分壓器設(shè)計(jì)

雙電阻圖騰柱解決方案允許端接與傳輸線匹配,以最大限度地減少反射,但代價(jià)是連續(xù)直流電流。

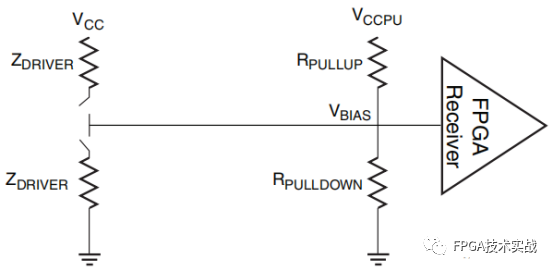

圖3:帶Thevenin并聯(lián)終端的驅(qū)動(dòng)器示意圖

電阻器的選擇必須使其組合并聯(lián)電阻盡可能接近Z0。此外,必須遵守接收器的VIH和VIL電平。如圖3所示,VBIAS點(diǎn)的概念確保輸入的高信號(hào)能夠以足夠的強(qiáng)度向下驅(qū)動(dòng),以匹配輸入的低信號(hào)的驅(qū)動(dòng)強(qiáng)度。知道這個(gè)VBIAS點(diǎn)可以計(jì)算上拉和下拉電阻值。將端接電阻器靠近接收器,以獲得最佳信號(hào)完整性。

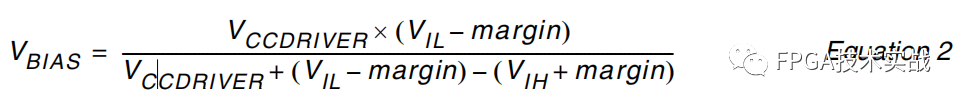

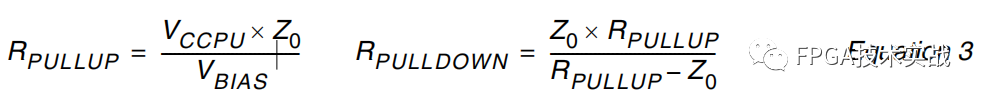

VBIAS(方程2)的計(jì)算更為復(fù)雜,并假設(shè)輸出高和低驅(qū)動(dòng)強(qiáng)度是平衡的。

在獲得VBIAS之后,可以計(jì)算RPULLUP和RPULLDOWN,如等式3所示:

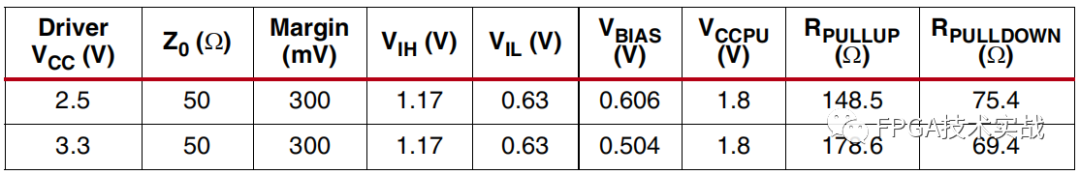

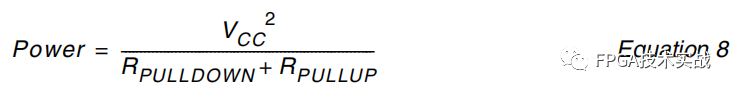

表2顯示了對(duì)于2.5V和3.3V的驅(qū)動(dòng)器VCC的RPULLUP和RPULLDOWN的計(jì)算值。

表2:RPULLUP和RPULLDOWN的計(jì)算值

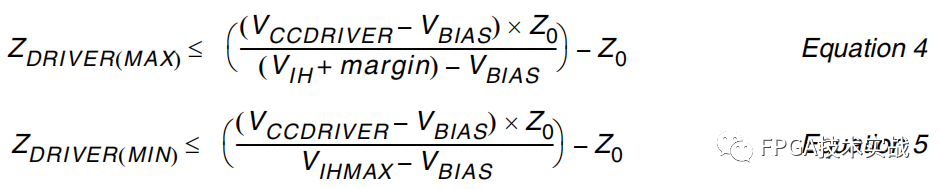

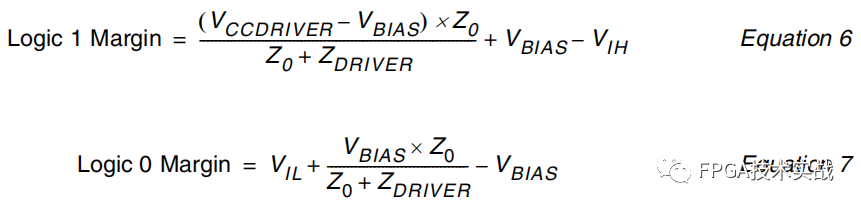

使用圖3中的拓?fù)鋱D,驅(qū)動(dòng)器的輸出阻抗必須足夠小,才能達(dá)到接收器的VIH和VIL閾值。此外,輸出阻抗必須足夠大,以免過驅(qū)動(dòng)接收器的推薦工作電壓(VIHMAX)。在7個(gè)系列FPGA中,LVCMOS18的VIHmax為2.1V。ZDRIVER(MAX)和ZDRIVER(MIN)的計(jì)算分別如方程4和方程5所示。

表3顯示了對(duì)于2.5V和3.3V的驅(qū)動(dòng)器VCC的ZDRIVER(MAX)和ZDRIVER(MIN)的計(jì)算值。

表3:ZDRIVER(最大值)和ZDRIVER(最小值)的計(jì)算值

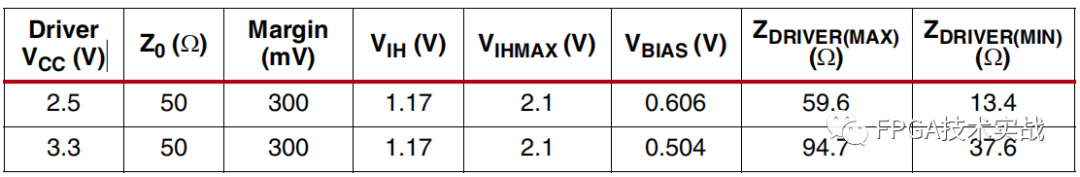

在ZDRIVER(MAX)處,邏輯1和邏輯0正好有300mV的裕度。隨著輸出阻抗的減小,邏輯1裕度的增長(zhǎng)速度快于邏輯0裕度。方程6和方程7根據(jù)實(shí)際驅(qū)動(dòng)器阻抗計(jì)算精確的裕度水平。

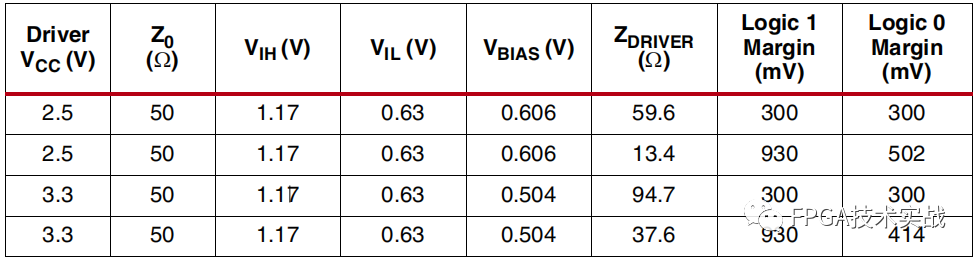

表4顯示了2.5V和3.3V的驅(qū)動(dòng)器VCC的邏輯0和邏輯1余量的計(jì)算值。

表4:邏輯0和邏輯1余量的計(jì)算

使用等式8計(jì)算圖騰柱終端每次I/O消耗的偏置功率,VCC表示上拉電壓。

表5:每個(gè)I/O的功率計(jì)算

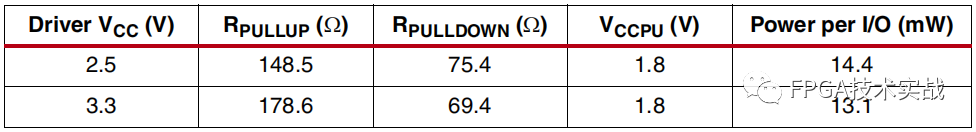

通過使用VBIAS的并聯(lián)端接,可以在沒有直流偏置的情況下實(shí)現(xiàn)相同的性能,而需要額外的電源導(dǎo)軌(圖4)。如果應(yīng)用程序具有大量輸入,則此解決方案可能是一個(gè)更節(jié)能的選項(xiàng)。

圖4:示例:VBIAS拓?fù)涞牟⑿卸私?/p>

3. 串聯(lián)FET開關(guān)

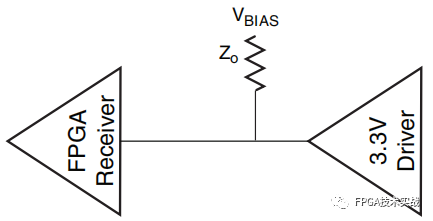

串聯(lián)FET開關(guān)可以保證從3.3V到1.8V的單向電壓轉(zhuǎn)換,并可以修改為從1.8V到3.3V工作。該器件的性能類似于與傳輸線串聯(lián)的NMOS晶體管,如圖5所示。

圖5:串聯(lián)FET開關(guān)

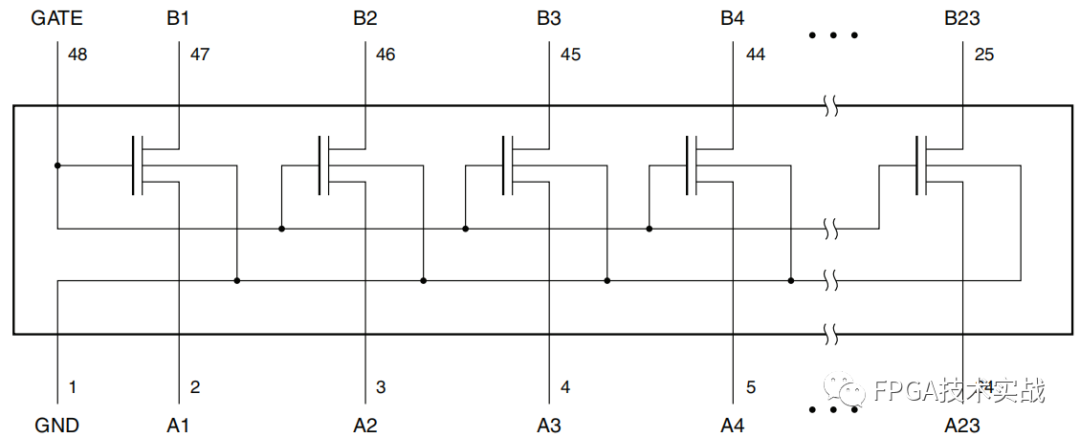

如果晶體管的柵極被設(shè)置為1.8V+VT,則來自3.3V驅(qū)動(dòng)器的信號(hào)僅高達(dá)1.8V傳遞到接收器。德州儀器SN74TVC16222ADGVR提供23個(gè)具有公共柵極的并聯(lián)NMOS傳輸晶體管,如圖6所示。

圖6:德州儀器SN74TVC16222ADGVR的簡(jiǎn)化示意圖

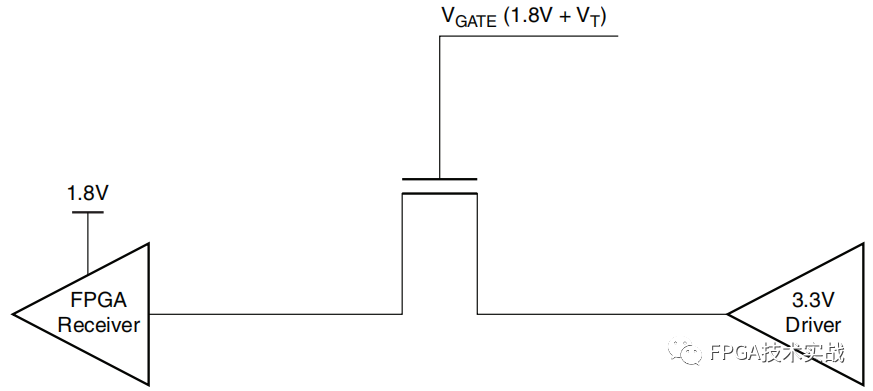

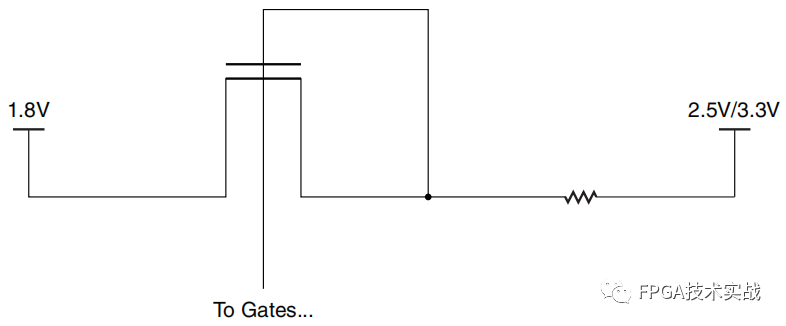

為了確保從2.5V/3.3V驅(qū)動(dòng)器通過的電壓不超過1.8V,可以使用23個(gè)NMOS晶體管中的一個(gè)作為參考晶體管,將所有柵極電壓偏置到1.8V+VT,如圖7所示。

圖7:1.8V參考晶體管示例設(shè)置

2.5/3.3V的電阻器應(yīng)足夠高(數(shù)百kΩ) 以限制到1.8V軌道的電流。

1.8V至2.5V/3.3V帶FET開關(guān)的接口

僅通過FET開關(guān)將1.8V驅(qū)動(dòng)到2.5V或3.3V接收器,留下非常少或沒有VIHmargin。例如,在1.8V驅(qū)動(dòng)到VIH為1.7V的Spartan-6 FPGA LVCMOS25接收器的情況下,只有100 mV的裕度可用。在1.8V驅(qū)動(dòng)到VIH為2.0V的Spartan-6 FPGA LVCMOS33接收器的情況下,根本沒有余量。

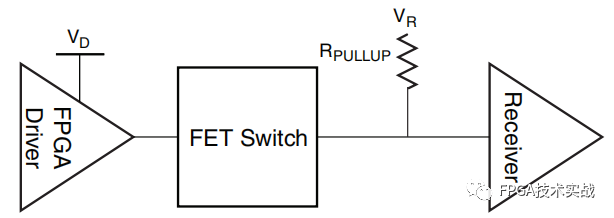

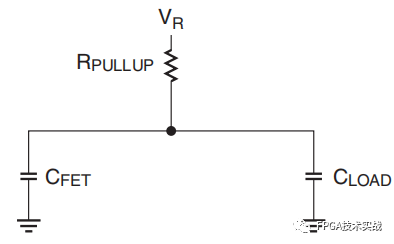

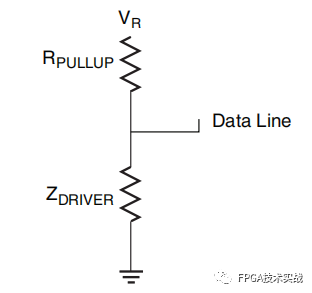

如圖8所示,接收器輸入端的上拉電阻器可用于為低至高轉(zhuǎn)換信號(hào)增加裕度。將RPULLUP放置在接收器附近,以獲得最佳信號(hào)完整性。

圖8:FET開關(guān)上拉拓?fù)?/p>

在確定該電阻器的尺寸時(shí)必須特別小心,因?yàn)槭蛊涓鼜?qiáng)有助于以犧牲高-低轉(zhuǎn)換信號(hào)為代價(jià)的低-高轉(zhuǎn)換信號(hào)。此外,該電阻器影響低到高和高到低轉(zhuǎn)換信號(hào)的定時(shí)。

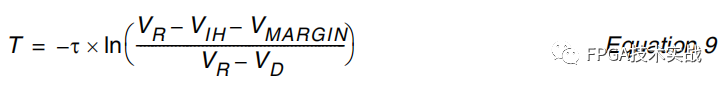

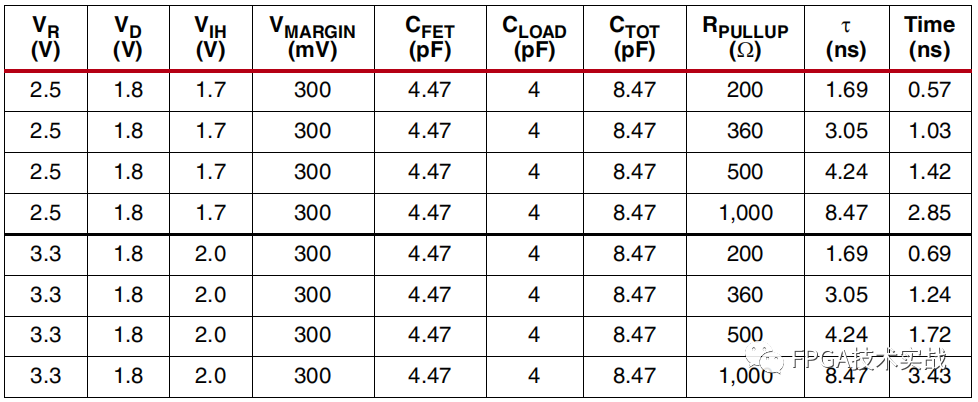

將線路從FPGA驅(qū)動(dòng)器的VCC充電到VIH所需的額外時(shí)間(T)(加上裕度)可以在等式9中合理估計(jì),拓?fù)鋱D如圖8和圖9所示。VIH是接收器的,并且Vm是高于VIH的期望裕度。t 是時(shí)間常數(shù)RPULLUP x(CFET+CLOAD)。

表6:通過上拉電阻器充電的額外時(shí)間

圖9:場(chǎng)效應(yīng)管3.3V側(cè)的示意圖

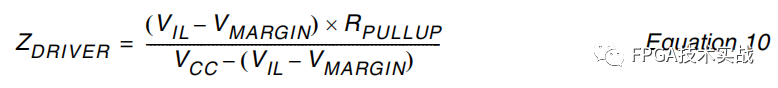

上拉電阻器的存在會(huì)影響高到低的轉(zhuǎn)換信號(hào),因此驅(qū)動(dòng)器阻抗必須足夠低,以確保仍然滿足VIL電平,減去一定量的裕度。公式10計(jì)算最大驅(qū)動(dòng)器阻抗,并使用圖10中的示意圖作為參考。

圖10:帶上拉電阻器的驅(qū)動(dòng)器驅(qū)動(dòng)邏輯0的示意圖

表7顯示了基于各種上拉電阻值的最大驅(qū)動(dòng)器阻抗值。

表7:最大驅(qū)動(dòng)器阻抗與上拉電阻器

I2C兼容性

使用具有適當(dāng)電阻器上拉值的FET開關(guān)可以成功地對(duì)I2C信號(hào)進(jìn)行電平轉(zhuǎn)換。

4. 自動(dòng)電平轉(zhuǎn)換器

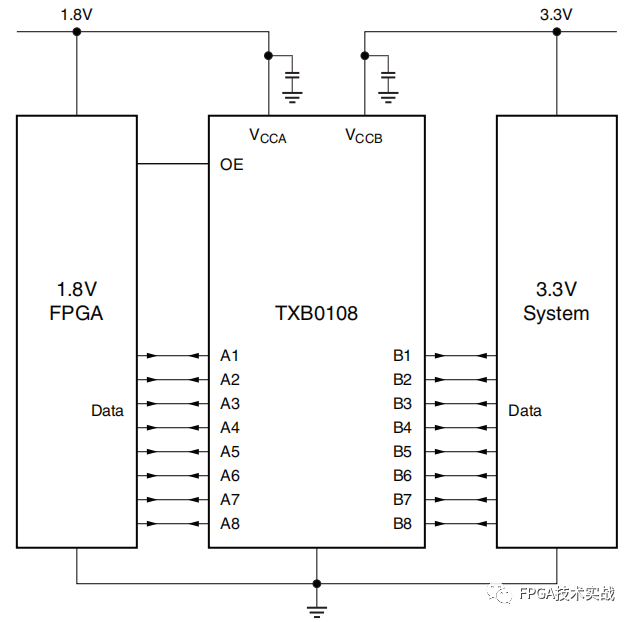

圖11中的德州儀器TXB0108框圖是一個(gè)自動(dòng)方向感測(cè)液位轉(zhuǎn)換器。自動(dòng)感知交通方向的能力使自動(dòng)級(jí)翻譯器很容易進(jìn)入雙向系統(tǒng)。沒有額外的控制信號(hào),因?yàn)槊總€(gè)比特都有一個(gè)獨(dú)立的方向傳感器。該設(shè)備加起來為7.6ns

電路的傳播延遲(3.3V至1.8V)。由于該設(shè)備的性質(zhì),如果線路上存在終端或其他重負(fù)載,可能會(huì)導(dǎo)致邏輯故障。終端和總線負(fù)載必須大于50 kΩ 以避免邏輯中斷。因此,I2C和1Wire等開漏總線與這種類型的電平轉(zhuǎn)換器不兼容。

圖11:自動(dòng)電平轉(zhuǎn)換器拓?fù)?/p>

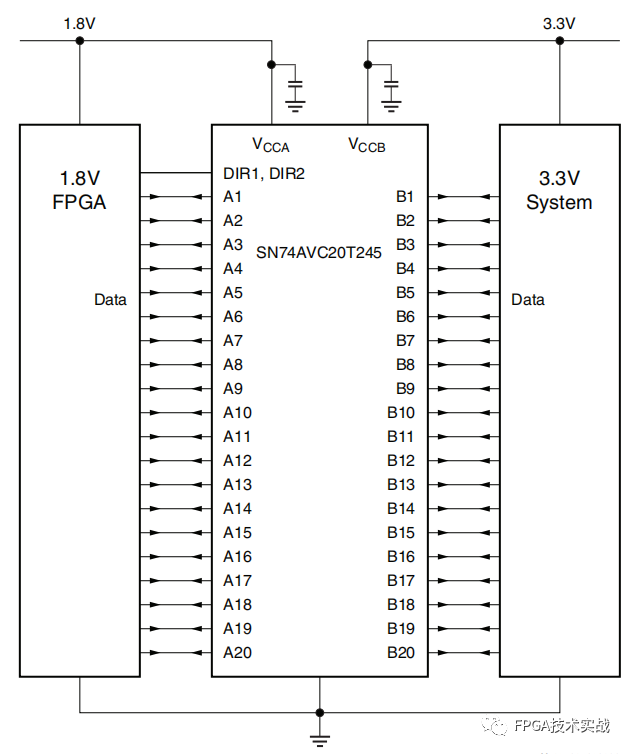

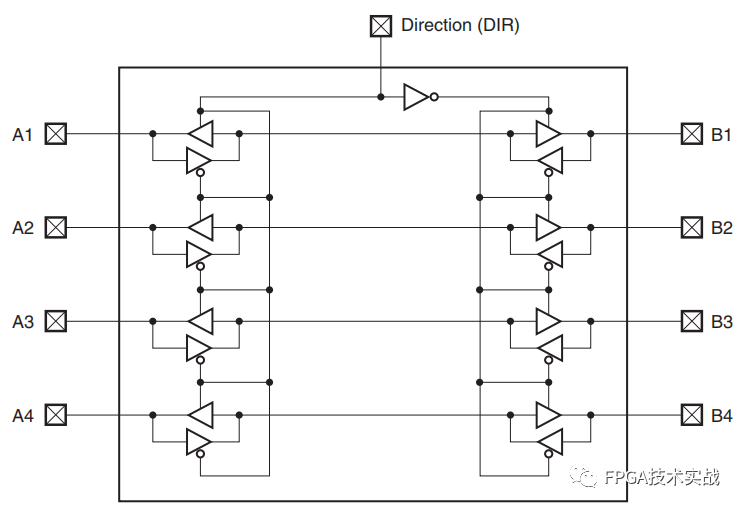

5.定向電平轉(zhuǎn)換器

德州儀器SN74AVC20T245是一個(gè)20位雙向電平轉(zhuǎn)換器,根據(jù)DIR的邏輯將數(shù)據(jù)從A電平轉(zhuǎn)換到B電平或從B電平轉(zhuǎn)換到A電平(圖12,第10頁)。

SN74AVC20T245分為兩條10位總線,每條總線具有獨(dú)立的DIR控制。每個(gè)塊還有一個(gè)輸出使能,用于將端口A與B隔離。通過設(shè)備存在高達(dá)4.6ns的引腳到引腳傳播延遲。

圖12:20位雙向電平轉(zhuǎn)換器拓?fù)?/p>

6. CPLDs and FPGAs轉(zhuǎn)換

各種Xilinx器件具有2.5V和3.3V的耐受性,可適用于雙向電平移動(dòng)應(yīng)用。Xilinx CPLD非常適合。

Xilinx CPLD非常適合在3.3V之間進(jìn)行電平轉(zhuǎn)換,并且可提供多達(dá)117個(gè)I/O,以支持多達(dá)58位的總線。Spartan-6 FPGA也非常適合3.3V電平轉(zhuǎn)換,可提供高達(dá)530個(gè)I/O。Virtex-6 FPGA也是可行的選擇,可以從2.5V切換到2.5V。非易失性Spartan-3AN系列是另一個(gè)可行的選擇。

使用CPLD或FPGA可以卸載7系列FPGA的其他邏輯和任務(wù)。通過Xilinx CPLD的引腳到引腳傳播延遲為5ns,而對(duì)于FPGA,這取決于通過設(shè)備的路由。

圖13:CPLD或FPGA設(shè)計(jì)示例示意圖

在CPLD或Spartan設(shè)備(圖13)中,IOBUF被實(shí)例化以與7系列設(shè)備接口,而另一個(gè)IOBUF用于與2.5V/3.3V邏輯接口。信號(hào)從7系列FPGA或3.3V邏輯引入設(shè)備,以識(shí)別業(yè)務(wù)方向。

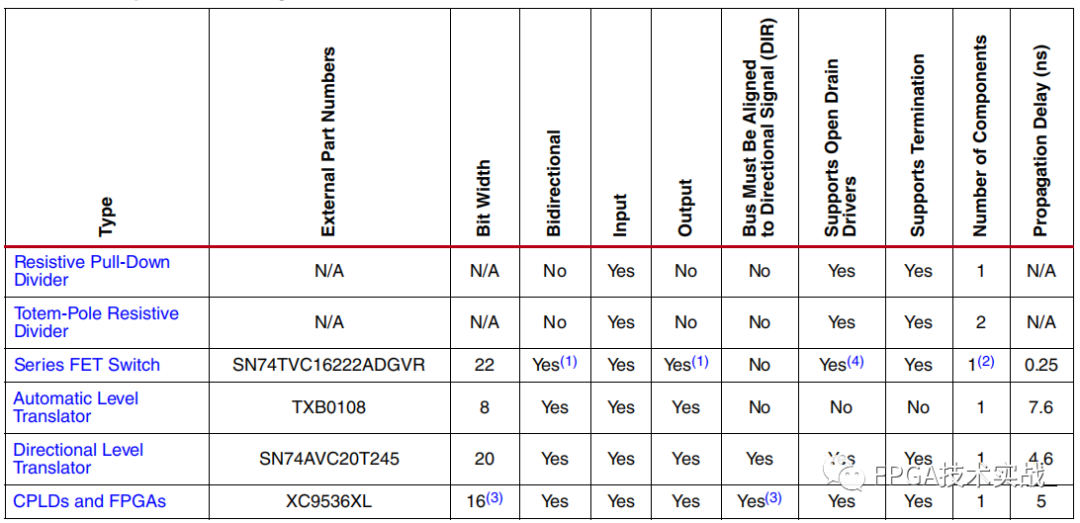

7.設(shè)計(jì)指導(dǎo)

表8給出了幾種電平轉(zhuǎn)換方法的比較。7系列FPGA中的高性能I/O組能夠通過一系列選項(xiàng)適應(yīng)更高電壓的接口,這些選項(xiàng)幾乎可以滿足所有設(shè)計(jì)、成本和性能需求。

表8:設(shè)計(jì)指南比較

審核編輯:劉清

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論