當(dāng)將SoC的代碼分割到多片FPGA的任務(wù)完成,并且所有FPGA的資源利用都很平衡,在建議的范圍50%到70%左右。此外,每個(gè)FPGA中被分配到的RTL設(shè)計(jì)的IO最小化,也就是說分割邊界的IO數(shù)量是最小的,但在如此好的工作之后,仍然有可能沒有足夠的FPGA引腳可用于連接所有設(shè)計(jì)IO,或者更準(zhǔn)確地說,一些FPGA之間沒有足夠的板載trace跡線。那這個(gè)時(shí)候的解決方案是在所用的FPGA之間復(fù)用設(shè)計(jì)信號(hào)。多路復(fù)用意味著多個(gè)兼容的設(shè)計(jì)信號(hào)通過相同的板載trace跡線被組裝和串行化,然后在接收FPGA處被解復(fù)用。可以簡(jiǎn)單理解為根據(jù)時(shí)鐘先按照并行轉(zhuǎn)換串行的方式,將多路信號(hào)通過單路傳輸?shù)搅硪唤邮盏腇PGA端,然后在接收的那一端轉(zhuǎn)換成并行信號(hào)與此FPGA中的設(shè)計(jì)相連接,形成完整的SoC系統(tǒng)功能。

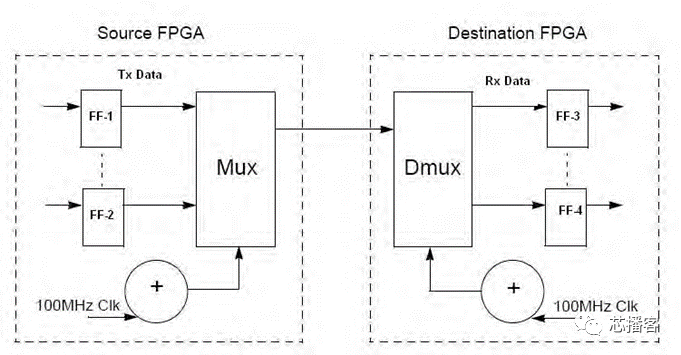

FPGA之間的兩個(gè)多路復(fù)用信號(hào)需要許多組件,包括多路復(fù)用器(mux)、解復(fù)用器(dmux)、時(shí)鐘源和保持所有這些相互同步的方法。

如果我們可以自由更改RTL,那么理論上,可以在每個(gè)FPGA邊界手動(dòng)添加這些元素。我們需要在分區(qū)之后添加復(fù)用元素,或者從一開始就將元素添加到RTL中,因此預(yù)先假設(shè)分區(qū)邊界的位置。在這兩種情況下,SoC團(tuán)隊(duì)的其他成員可能會(huì)認(rèn)為這與最初的SoC的RTL相距太遠(yuǎn),并引入了太多錯(cuò)誤機(jī)會(huì)。

大多數(shù)團(tuán)隊(duì)不會(huì)考慮對(duì)SoC RTL進(jìn)行如此廣泛的更改,而是依賴于自動(dòng)化的方式來添加復(fù)用,通過腳本化的直接編輯合成后網(wǎng)表,或者根據(jù)分區(qū)過程給出的方向在合成過程中進(jìn)行推斷。

無論采用何種方法引入多路復(fù)用,該方案的基本要求是在一個(gè)設(shè)計(jì)時(shí)鐘內(nèi)將IO數(shù)據(jù)值從一個(gè)FPGA傳輸?shù)搅硪粋€(gè)FPGA。為了實(shí)現(xiàn)這一點(diǎn),串行傳輸時(shí)鐘(也稱為多路復(fù)用時(shí)鐘或快速時(shí)鐘)必須比設(shè)計(jì)時(shí)鐘更快地對(duì)這些數(shù)據(jù)值進(jìn)行采樣,以確保在下一個(gè)活動(dòng)設(shè)計(jì)時(shí)鐘邊緣之前接收FPGA中的所有數(shù)據(jù)都可用。

例如,假設(shè)我們有四個(gè)IO數(shù)據(jù)值要在兩個(gè)FPGA之間傳輸,這兩個(gè)FPGA在單個(gè)板上連接上復(fù)用,即復(fù)用率為4:1。如果設(shè)計(jì)的這一部分以20MHz運(yùn)行,那么,為了在設(shè)計(jì)時(shí)鐘周期內(nèi)傳輸四個(gè)設(shè)計(jì)IO,我們需要比設(shè)計(jì)時(shí)鐘快至少四倍的傳輸時(shí)鐘。因此,傳輸時(shí)鐘必須至少為80MHz。實(shí)際上,對(duì)于4:1的多路復(fù)用,它需要快四倍以上,因?yàn)槲覀冃枰_保在數(shù)據(jù)到達(dá)傳輸時(shí)鐘,然后在設(shè)計(jì)時(shí)鐘上鎖存到下游邏輯之間滿足設(shè)置和保持時(shí)間。

在使用多路復(fù)用的大多數(shù)情況下,它會(huì)降低設(shè)計(jì)的總體速度,并且通常是整個(gè)系統(tǒng)速度的控制因素。串行傳輸速度受到通過FPGA IO的最大速度和通過板載軌跡的互連線的傳輸時(shí)間的限制。因此,由于這些物理限制,需要優(yōu)化復(fù)用方案,以允許原型以最大速度運(yùn)行。

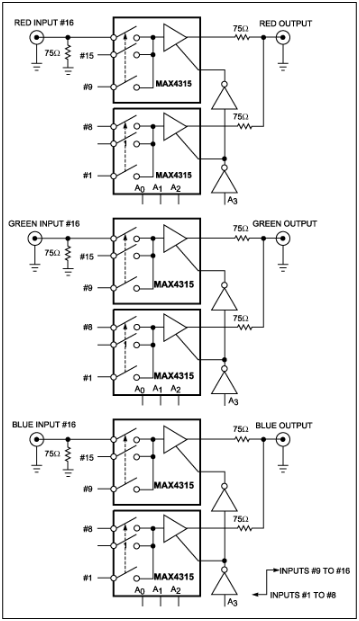

多路復(fù)用通常由插入多路復(fù)用器和多路復(fù)用器元件并用合適的信號(hào)填充分區(qū)工具支持。例如,有兩種不同類型的方案,采用LVDS傳輸或高速時(shí)域復(fù)用(HSTDM)。

根據(jù)傳輸時(shí)鐘和設(shè)計(jì)時(shí)鐘的關(guān)系,我們可以區(qū)分兩種類型的復(fù)用。異步復(fù)用,其中傳輸時(shí)鐘與設(shè)計(jì)時(shí)鐘沒有相位關(guān)系,以及同步復(fù)用,其中,傳輸時(shí)鐘相位與設(shè)計(jì)時(shí)鐘對(duì)齊,甚至可能從中導(dǎo)出。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21982瀏覽量

614568 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1886瀏覽量

132890 -

復(fù)用器

+關(guān)注

關(guān)注

1文章

753瀏覽量

28871

原文標(biāo)題:多片F(xiàn)PGA原型系統(tǒng):多路復(fù)用(TDM)科普

文章出處:【微信號(hào):于博士Jacky,微信公眾號(hào):于博士Jacky】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

一文掌握多片FPGA的多路復(fù)用

多路復(fù)用ICSP引腳如何控制開關(guān)?

時(shí)鐘信號(hào)切換可以用多路復(fù)用開關(guān)嗎

如何在Mx1051的FlexCAN1中配置簡(jiǎn)單信號(hào)多路復(fù)用和擴(kuò)展信號(hào)多路復(fù)用?

多路復(fù)用與數(shù)字復(fù)接

多路復(fù)用技術(shù)

非多路復(fù)用與多路復(fù)用總線轉(zhuǎn)換橋的設(shè)計(jì)與實(shí)現(xiàn)

時(shí)分多路復(fù)用(TDM),時(shí)分多路復(fù)用(TDM)的原理是什么?

什么是異步時(shí)分多路復(fù)用(ATDM)

時(shí)分多路復(fù)用(TDM),時(shí)分多路復(fù)用(TDM)是什么意思

8:1 多路復(fù)用放大器形成大型多平面多路復(fù)用器結(jié)構(gòu)

基于多片F(xiàn)PGA多路復(fù)用(TDM)科普

基于多片F(xiàn)PGA多路復(fù)用(TDM)科普

評(píng)論