CVD 篇

CenturaDXZ CVD

先進MEMS,功率器件和封裝中的應用驅動了對先進的150mm和200mmCVD技術的需求。為滿足這些技術的制造要求,需要超厚氧化物(≥20μm),低溫(180°C-350°C),保形的、低濕刻蝕速率的薄膜和折射率可調的摻雜薄膜。這些薄膜加入了Centura DXZ CVD系統上可用的廣泛工藝組合,從TEOS,基于硅烷的氧化物和氮化物到低k介電質,應變工程和可光刻的薄膜。該系統還產生各種摻雜(膦,硼和氟)和未摻雜的間隙填充溶液。這些過程處理諸如STI,PMD,ILD和IMD之類的應用程序。

碳化硅(SiC)是新興的用于高速應用的材料。然而,其透明性使得晶圓處理變得特別嚴苛。DXZ CVD系統配備了增強的功能,能可靠而細致地處理碳化硅(SiC)晶圓,包括從Loadlock的晶圓映射,到清晰的晶圓定向,再到晶圓放置。

Centura DXZ系統設計顯著優化了成本(例如零耗材的處理套件)、吞吐量、易維護性和可靠性。該系統采用單晶圓、多腔室架構,可提供高達80wph的正硅酸乙酯(TEOS)和碳化硅(SiC)吞吐量(3,000?PE 正硅酸乙酯和等離子硅烷)和高達35wph的非摻雜二氧化硅晶體(USG)吞吐量(2000?SACVD USG)。對稱的設計和較小的腔室容積可提高沉積和清潔化學品的有效氣體利用率,從而降低總體擁有成本。

Centura DxZ CVD 腔室采用了非消耗型電阻加熱器和陶瓷部件,可顯著改善成本、產能、易維護性和可靠性。DxZ 工藝套件也由零消耗部件組成。借助單晶圓多腔室架構,Centura DxZ 可提供高達 100WPH(3,000? PE TEOS 和硅烷等離子體)和 55wph (3000? SACVD USG) 的產能。對稱式設計和小腔室容量,對于沉積和清潔化學物可實現高效的氣體利用率,這有助于降低總體擁有成本。

CenturaUltima HDP CVD

應用材料公司的 Centura Ultima HDP CVD 200 毫米和 300 毫米系統提供高密度等離子CVD工藝制程。該系統一直是行業領先的主力設備,可提供高質量的介電質薄膜沉積和無孔洞間隙填充工藝。它的反應器可幫助客戶實現多代制造所需的產能、成本效益和可擴展性。

Ultima HDP 系統配備雙RF(射頻)線圈,具有覆蓋整個晶圓的出色間隙填充能力;其創新的靜電卡盤系統能帶來極佳的薄膜質量和均勻性;其遠程等離子清潔系統可提供卓越的缺陷預防性能,并可降低設備清洗頻率,增加晶圓產出(mean-wafer-between-clean, MWBC)。

該產品技術先進,既可沉積無摻雜薄膜,又可沉積摻雜薄膜,應用十分廣泛,包括沉積淺溝槽隔離層(STI)、金屬前介電質層(PMD)、層間介電質層(ILD)、金屬層間介電質層(IMD)和鈍化保護層。它功能多樣,可進一步拓展用于回蝕和高密度等離子處理,以提高薄膜質量。

EnduraVoltaW CVD

鎢的電阻率低,電遷移性極小,長期以來一直在邏輯和存儲器件中用作接觸孔和中段(最底層)連接線(將晶體管與集成電路其余部分相連)的首選填充材料。在早先的技術節點中,由于器件尺寸較大,因而可以使用共形 CVD 沉積法進行鎢填充集成。不過,在當前最先進的技術節點下,特征尺寸極其細微,而且還有凹形形貌,因而難以使用這種沉積法來確保對這些器件特征進行完好的無縫隙鎢填充。由于沉積期間超小開口頂部周邊會出現懸垂現象,使得共形工藝無法完好填充出無孔洞的特征;即便不產生孔洞,共形沉積法也不可避免會在中間留下縫隙。這些屬性使得極其細小的特征結構容易在化學機械拋光 (CMP) 期間遭到破壞;先進芯片設計中的高密度特征以及缺乏通孔冗余,意味著一個簡單的孔洞就會造成器件故障和成品率損失。

Centura iSprint ALD/CVD SSW 系統融合了應用材料公司在材料工程和金屬 CVD 接觸孔應用領域長期積累的專業能力和豐富經驗,利用獨特的“選擇比”抑制機制,自底向上進行填充,避免出現縫隙或孔洞。改進填充工藝的完整性,有助于提高鎢體積(有可能降低電阻),制造出更堅固耐用的特征結構,緩解對介電質和刻蝕開口步驟的要求,從而改善性能、器件設計和成品率。

鎢已廣泛用于邏輯接觸體、中端和金屬柵極填充應用中,因為它具有低電阻和保形批量填充性能。接觸體和局部互連線在晶體管和其余的電路之間形成了臨界電氣通路。因此,低電阻率對于穩健和可靠的器件性能至關重要。然而,隨著微縮繼續進行,互聯層尺寸開始縮小到某種程度,并成為實現最佳晶體管性能的障礙。

隨著互聯層的橫截面繼續減小,越來越多的體積被金屬阻擋層和成核層占據,為導電金屬填充所留的體積變小。此外,插塞中的每個額外的金屬界面讓接觸電阻更糟糕。Volta CVD W 系統通過腔體的硬件增強功能來緩解這些不利因素,該腔體能夠使用專業化學品來沉積 W 碳薄膜。這一獨特的材料能夠充當襯層和成核層。它可以強有力地粘合介電質,并可以避免在后續的大量沉積工藝中發生氟擴散。其電阻率比標準襯層(如 TiN)低 70%。此外,如果薄膜主要為 W 薄膜,它表現為批量 W 薄膜的成核基板。因此,界面膜的總厚度更薄,從而增加了可用于低電阻率 W 填充的體積。

根據關鍵尺寸和工藝流程,Volta CVD W 薄膜最高可將接觸孔電阻降低 90%。因此,它改善了設備的功率輸出、性能和效能,并為下一代器件擴展了 W 中端互聯插塞。更低的電阻也便于在給定的節點中更激進地微縮,從而能夠實現更高的器件密度。

Endura Volta

鎢因其低電阻率和體填充特性,已廣泛用作中段 (MOL)導線的間隙填充材料。MOL 導線在晶體管與互連器件之間形成關鍵的導電通路。因此,確保導線的低電阻率對于整個器件性能來說至關重要。

然而,隨著微縮的不斷發展,導線尺寸開始縮小到某種程度,使導線電阻成為實現最佳器件性能的障礙。隨著導線橫截面的縮小,金屬襯墊/阻擋層和成核層占據體積比例越來越大,為導電金屬填充所留的體積變小。另外,鎢塞中的多個電阻界面也進一步提高了導線電阻。

應用材料公司的Endura Volta 選擇性鎢化學氣相沉積 (Selective W CVD) 系統提供了一種集成材料解決方案(Integrated Materials Solution),緩解了伴隨二維微縮領域的突破帶來的不利影響。該系統包括表面處理腔室與選擇性鎢沉積腔室。選擇性沉積是通過沉積腔室的獨特工藝能力和各種表面處理來實現的,這些表面處理使用專門的化學制劑來制備接觸孔的底層金屬和介電質,從而實現自底而上的金屬對金屬沉積。這種選擇性工藝消除了襯墊/阻擋層和成核層,從而緩解了器件性能的瓶頸,并生成無空隙和無縫隙的填充。

由于所有的工序都是在超潔凈、連續的高真空環境中進行,這種整合材料解決方案確保了純凈的界面和無缺陷的導線填充。與傳統的襯墊/阻擋層導線制造相比,隨著導電金屬體積的最大化,導線電阻率得到了顯著改善。這種較低的電阻率有利于提高器件密度并延伸了二維微縮。

Volta CVD Cobalt

應用材料公司的 Endura Volta CVD Cobalt 系統使公司能夠在CVD領域保持技術領先地位,在超過 15 年的銅阻擋層/種子層 (CuBS) 開發中首次改變材料,以實現持續的高性能互連微縮。這種史無前例的技術可以沉積厚度不足 20? 的種子增強型襯層和選擇性蓋帽層,從而改善 2Xnm 及以下節點的互連線良率與可靠性。它是業界唯一基于真空的電遷移(EM) 解決方案,是在同一平臺上與預清洗、阻擋層和銅種子層工藝集成的唯一 CVD 鈷襯層產品。

在復雜移動技術需求的推動下,多組件系統芯片 (SoC) 設計在迅速激增,以便實現所需的功能和緊湊的形狀系數。而當代處理器偏于激進的節距微縮,進一步推動了電路密度的增加,而且對高性能互連線必不可少(這些互連線在多層器件中路徑長度近乎幾英里)。這些趨勢使實現器件運行所必需的覆蓋、粘附和無空隙銅互連線填充更具挑戰性。即便出現一個孔洞,也可能導致芯片的某些部分不可用。

Volta CVD Cobalt 系統為擴展銅互連技術推出新材料,將這一工藝帶入新時代。它通過改善銅浸潤來促進銅種子層覆蓋,從而能夠形成便于修復不連續形貌和形成健壯種子層的連續薄共形層。這種高品質層進而能夠在最先進的節點下促進無孔洞銅間隙填充。

此外,尺寸收縮會造成更高的電阻,而且更容易受到銅線路中電遷移失效的影響。銅與介電質阻擋層之間在界面層處的高質量接合,對避免電遷移失效至關重要。Volta 系統一流的 (>100:1) 選擇性金屬蓋帽工藝可強化銅介電質界面層處的粘附,從而能夠成數量級提升電遷移性能,而不會增加線路電阻,也不會削弱介電質層時變擊穿特性。

Volta CVD Cobalt 同時用于襯里和選擇性金屬蓋帽工藝,便于完全封裝銅線路,確保 2Xnm 及以下節點最穩健的互連可靠性。

Producer XP PrecisionCVD

Precision 腔室經過專門設計,可均勻地進行層間沉積,達到柵疊層所需的薄膜質量,從而能夠幫助芯片制造商從平面架構過渡到 3D NAND 生產。該產品具備調整多個工藝和腔室環境參數的獨特能力,是唯一使客戶能夠以嚴格的均勻性和極少的缺陷數沉積不同薄膜交替層的工具。

Precision 系統還能夠沉積新型硬掩膜薄膜,如 Saphira APF,它具有高選擇比、低應力和更高的透明度,非常適合生成新近業內流行的高深寬比和密集圖形化特征。這些薄膜能夠經受制造下一代 3D NAND(預計層數會不斷增加)以及先進DRAM的高深寬比特征所需的長刻蝕過程。

Producer XP Precision 系統采用模塊化結構,專為高效率制造而設計。它將經過生產驗證的 Producer 大型機架構和高速系統協議與更快速、更高效的 Precision 腔室處理技術相結合,可提供極佳的產能密度。

Producer PrecisionAPFPECVD

應用材料公司的 Producer PrecisionAPFPECVD系統能夠為關鍵圖形化工序生成一系列可剝除的無定形碳硬掩膜。

該系統是業界第一個商用 PECVD 沉積可灰化無定形碳薄膜圖形化系統,全球幾乎每一座先進的DRAM、NAND閃存和邏輯器件制造工廠都配備有該系統。業內領先的 APF 是實現多重圖形化集成方案的一種薄膜,可突破標準 ArF 光刻的物理極限進行微縮;并可以實現高深寬比 (HAR) 特征的圖形化。隨著 APF 應用的激增,APF 已從最初的單一薄膜發展成為一系列的專用薄膜。

StensarAPF 是該系列薄膜家族的最新成員,它將這些先進的硬掩模薄膜擴展應用于最前沿的技術。還有一些 APF 系列薄膜專用于物聯網、通信、汽車、電源和傳感器 (ICAPS) 市場。

Stensar

低應力 Stensar APF 可滿足制造 2納米邏輯器件對硬掩模的極端嚴苛要求(特別是針對超低缺陷率)。它比旋涂膜有更優良的選擇比,沉積速率低,有助于降低整體疊層厚度,從而減少線條邊緣粗糙度 (LER) 和線寬粗糙度,二者都是 2納米節點圖形化所面臨的重大挑戰。Stensar 支持全系列的SADP/SAQP和EUVL方案,以及處于半導體技術前沿的 HAR 特征蝕刻應用。表面工藝則可實現這些挑戰性工藝制程的無縫集成。

減少薄膜除氣過程,可以保持更清潔的腔室環境,從而延長正常運行時間,增加清潔間隔平均時間。Producer Precision 系統可以調整硬掩模的刻蝕選擇比,從而保持出色的工藝性能。

Saphira

Saphira APF 是一種高選擇比、低應力的透明硬掩膜,從而支持實現進一步的特征微縮。它便于集成,工藝簡潔,可減少圖形化復雜度。

APFe

APFe 在 APF 出色的刻蝕選擇比和 LER 的基礎上,比 APF 能沉積更厚的層(如用于存儲器件的電容構造和金屬接觸孔),同時還能保持刻蝕高深寬比 (HAR) 通孔所需的對準透明度。

APF

APF 廣泛用作小特征尺寸和高深寬比 (HAR) 結構的圖形層,與傳統光刻膠(PR) 相比,具有極佳的刻蝕選擇比,線條邊緣粗糙度 (LER) 更低。它具有類似傳統光刻膠的可灰化性,能快速集成到工藝流程中。無論是單獨使用,還是與應用材料公司的 DARC(抗反射電介質涂層)工藝一起使用,這種經濟高效的光刻薄膜可提供多晶硅、氮化物和氧化物高刻蝕選擇比,具有出色的 CD 控制和更低的 LER。

Producer AvilaPECVD

應用材料公司的 Producer AvilaPECVD系統的高品質氧化物和氮化物系列薄膜可滿足TSV(硅通孔)和其他先進封裝應用所需的低熱預算和高產量需求。

TSV 制造工藝需要減薄器件晶圓,然后將其粘結到由玻璃或硅制成的臨時載體上。由于一般粘結劑的熱預算約為 200oC,所以這些混合型晶圓的所有后續加工必須在非常低的溫度下進行。在低溫下沉積高質量的薄膜需要一定的RF功率級,在該功率級下,會在晶圓表面產生相當可觀的額外熱量。為保持一致的晶圓溫度,Avila 系統配備了主動冷卻功能,以實現低至 130oC 的穩定基板溫度。

Avila 系統的沉積工藝在經過生產考驗的 Twin ChamberProducerGT平臺上運行,該平臺最多可同時處理六個晶圓。該平臺不僅在處理粘接晶圓時表現出優越的性能,其靈活的架構還支持應用材料公司的所有 TSV 介電層工藝,從而能夠實施高效的集成開發。此外,Producer GT 平臺的低溫介電薄膜產能是市面上其他系統的兩到三倍,因此可大幅降低每個晶圓的擁有成本。

Producer Black Diamond

Applied Producer Black Diamond 3 擴展了應用材料公司在納米多孔低 K介電層技術領域的領先地位,以便微縮 28nm 及以下節點的先進互聯層。

Black Diamond II 納米多孔低 K 薄膜是 45/32nm 銅/低 K互聯層的行業標準,其 K 值約為 2.5。低k 制造納米多孔的低 K 薄膜分為兩個步驟,第一步為有機硅酸鹽玻璃“脊骨” PECVD 和熱不穩定有機相沉積,第二步為紫外線 (UV) 固化,該步驟可以除去不穩定相,從而誘導空隙形成,并重建和強化其余的二氧化硅矩陣,以形成最終的納米多孔薄膜。

新一代的 Black Diamond 3 薄膜將這一行業領先的技術擴展為超低 K (ULK) 薄膜 (k~2.2),以便縮放到 22nm 及更先進節點,提升器件速度。它還能提供最新的先進封裝方案所需的機械強度(硬度和彈性)。該薄膜具有出色的抗濕性和極佳的機械強度,在刻蝕和去除光刻膠后具有穩定的 k 值。

Black Diamond 3 薄膜通過使用經過生產驗證的高產能 Producer GT 平臺來完成沉積。

Producer Black Diamond 3 系統設計為可與應用材料公司的 Producer Nanocure 3UV 固化系統配合使用。Nanocure 3 系統通過使用高密度的紫外線源來固化和密化 Black Diamond 3 薄膜,以便提供最佳的機械與光學性能。

這種兩步式沉積和固化工藝所實現的機械強度比應用材料公司取得成功的第二代 Black Diamond 薄膜高一倍,從而能夠降低器件變異性,并提高芯片的成品率。

Producer BLOk(低 k 阻擋層)PECVD

應用材料公司的 Producer BLOk(低 k 阻擋層)PECVD系統可生成行業領先的超低 k 銅阻擋層和刻蝕阻擋層薄膜,用于鑲嵌互連應用。借助 Producer 的 Twin Chamber架構,在進行 BLOk 沉積前,每個晶圓都經過原位氧化銅消除工藝(專利技術),確保出色的銅或鈷粘附性,以減少電遷移。

BLOk 薄膜能夠大幅降低介電薄膜疊層的電容,同時還可以保持出色的刻蝕選擇比和電學性能,有利于進一步的 RC 縮放。久經驗證的表面預處理和初始層工藝使 BLOk 很容易與 Black Diamond 薄膜集成,從而確保順利向 45nm 及以下節點應用換代過渡。

經過生產驗證的高產能 Producer 平臺,最多可同時處理六個晶圓,系統可靠性高,可帶來卓越的生產效率,顯著降低擁有成本。該平臺具備可擴展性,使客戶能夠將 Producer 工具集應用于多個工藝節點。

ProducerCVD

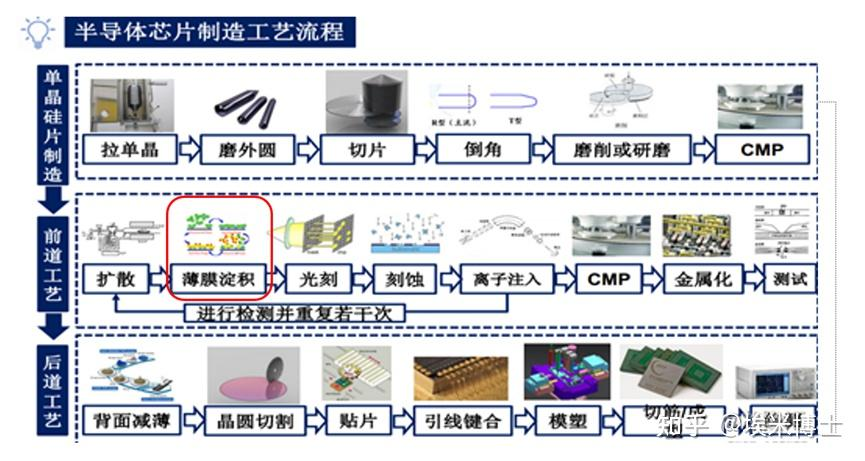

CVD技術在半導體加工工藝中至關重要,無論邏輯器件、DRAM、NAND,還是MtM細分市場中的MEMS、光電器件、物聯網和功率器件等技術,CVD 是所有半導體器件制造不可或缺的設備。應用材料公司的 Producer 平臺已成為多種薄膜開發的基礎平臺,每種薄膜都有其獨特的一系列工藝要求,而且要沉積在同樣形態不一的各種幾何結構(毯覆、間隙填充、共形)上,Producer 平臺可以很好滿足這些技術需要。

Producer 平臺能處理 150 毫米、200 毫米和 300 毫米晶圓,自 1998 年問世以來,跨越了10個結點的關鍵技術拐點(10 個結點),是有史以來最成功的平臺之一。其創新的 Twin Chamber雙腔室結構可同時處理多達六片晶圓,具有極佳的生產效率。借助陶瓷加熱器和腔室組件以及用于腔室清潔的遠程等離子體源,Producer 系統可將 CVD 膜的缺陷率降至最低。從裝載腔晶圓映射、到清晰的晶圓定向、再到晶片放置,該平臺能可靠而細致地處理各種 MtM 襯底(包括碳化硅晶圓)。

除了傳統的 PECVD(基于TEOS和硅烷的氧化物以及氮化物)和亞大氣壓的 CVD 膜外,Producer 系統還適用于低介電常數、應變工程、可光刻膜以及熱膜,高溫 PECVD 應用,硅鍺(SiGe)和非晶硅(a-Si)。它在 MtM 器件方面的一些應用示例包括較厚的膜(≥20μm),較低溫度的工藝(180°-350°C),更保形的膜及諸如低溫 PECVD 硅鍺(<50um)和非晶硅(a-Si)等新材料。

平臺的可擴展性使客戶可以將Producer工具組件用于多種設備類型和工藝節點。

Producer CeleraPECVD

應用材料公司的 Producer CeleraPECVD系統可以沉積可調壓縮和拉伸高應力氮化硅薄膜,用于 45nm 及以下節點的應變工程。

該系統將應力氮化物沉積與 UV 固化工藝相集成,可提供高達 1.7GPa 的拉伸應力,同時符合低熱預算要求。同一腔室可沉積壓縮應力高達 3.5 GPa 的薄膜。該工藝利用經過生產驗證的硅烷 CVD 技術,可提供出色的階梯覆蓋 (~70%),同時保持極佳的 SiN 刻蝕阻擋層性能和圖形負載結果。

應用材料公司的 Celera 沉積和 UV 固化工藝集成于經過生產驗證的高產能 Producer 平臺上,具有靈活的 Twin Chamber配置以及平臺可擴展性,使客戶能夠將 Producer 工具集應用于多個工藝節點。

ProducerDARCPECVD

應用材料公司的 ProducerDARCPECVD是行業領先的抗反射涂層薄膜,可在 90nm 及以下節點應用中,最大限度降低反射率、減少光刻膠中毒,提高光刻膠的附著力。

APF/DARC 薄膜疊層與應用材料公司的 APF(先進圖形化薄膜)可剝離 CVD 硬掩膜結合使用,可提升刻蝕優化解決方案的刻蝕選擇比、CD 控制和線條邊緣粗糙度。應用材料公司的 Producer DARC PECVD 提供廣泛的折射率和消光系數值精調范圍,可在多種應用中實現無與倫比的反射控制。這些薄膜可與其他 CVD 介電層原位集成,以實現高效率和低擁有成本。

DARC 193 廣泛用于傳統的柵極、多晶硅和鋁互連光刻應用,對低 k 介電薄膜具有出色的附著力,特別適合雙鑲嵌互連方案。

ProducerEternaFCVD

十多年來,應用材料公司在推動半導體間隙填充技術發展方面始終走在行業前列,Eterna FCVD 系統繼續保持了這一領先優勢。這些創新為客戶提供了獨特簡潔、經濟高效的解決方案,使其能夠應對多代芯片生產所帶來的挑戰。

芯片制造商在芯片設計上不斷縮小晶體管的尺寸,以提升單位尺寸的芯片功能。隨著晶體管的縮小,晶體管之間的空隙也在變小,彼此之間的物理隔離也變得日益困難。

使用高品質的介電質材料填充晶體管之間通常形狀不規則的微小空隙(間隙),變得越來越有困難,20nm 及以下節點的芯片設計需要新的解決方案。

應用材料公司新開發的 Producer Eterna Flowable CVD 系統可解決這一難題,是唯一可確保完全、無孔洞地填充這些臨界間隙的技術。

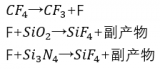

獨特的 Eterna FCVD 工藝可填充極端尺寸(深寬比高達 30:1)的間隙,包括高度不規則的間隙和具有復雜形貌的間隙。新工藝可在晶圓表面上沉積高品質的類流體態介電薄膜,使得薄膜能夠迅速流入間隙,完全填充間隙而不會留下孔洞或縫隙。采用的化學材料經過精心的挑選,可生成純度極高、穩定可靠、無碳的介電薄膜,以確保可靠的電氣隔離及與后續工序(如CMP)的兼容。

Eterna FCVD 工藝搭載于應用材料公司出色的 Producer GT 平臺之上,該平臺以其極佳的生產效率享譽業界。

ProducerHARP

應用材料公司的Producer HARP(高深寬比工藝)是一種非等離子體CVD熱氧化工藝,可滿足高級邏輯 FinFET和存儲器技術節點的STI(淺溝槽隔離層)和PMD(金屬前電介質層)等應用的嚴格間隙填充要求。

這一獨特的HARP工藝采用獲得專利的臭氧/TEOS化學技術,通過沉積應變誘導薄膜,顯著提高二維平面邏輯器件中晶體管的驅動電流,延長存儲器件中數據的保留時間,在不增加集成電路復雜度和成本的情況下,顯著提升晶體管性能。當 HARP工藝與其他應變誘導薄膜(例如應力氮化物和鍺硅外延)一起使用時,可帶來疊加的應變工程優勢。非等離子體沉積工藝還消除了等離子體引起的器件損壞,從而帶來出色的器件可靠性。

應用材料公司的HARP工藝在經過生產驗證的高產能Producer平臺上運行。憑借其創新的雙腔室架構,Producer平臺最多可同時處理六片晶圓,而且系統可靠性高,生產效率出色,顯著降低維護保養成本。該平臺具備可擴展性,使客戶能夠將Producer機臺應用于多種工藝節點。

ProducerInViaCVD

Producer InVia 系統提供CVD創新工藝,可在先通孔和中通孔TSV工藝中沉積高度共形且電學性能穩健的介電襯層。

對于想要開拓 TSV 業務的客戶,InVia 系統不僅提供一流的工藝,而且能夠在 TSV 制造工序中體現出集成價值。它是能夠滿足中通孔 TSV 的熱預算和共形性要求的唯一工藝。獨特的沉積工藝可帶來明顯優于標準規格的薄膜擊穿電壓和漏電流。

InVia 還是唯一能夠以大范圍的深寬比(6:1 到 11:1)沉積薄至 200nm 和厚至 1μm 襯層的沉積系統。

ProducerNanocure3 UV Cure

應用材料公司的 Producer Nanocure 3 專為與應用材料公司的 Producer Black Diamond3沉積系統配合使用而設計,以擴展應用材料公司在納米多孔低 k 介電層技術領域的領先地位,將先進互連結構的縮放推進到 28nm 及以下節點。

制造納米多孔的低 K 薄膜分為兩個步驟,第一步為有機硅酸鹽玻璃“脊骨” PECVD 和熱不穩定有機相沉積,第二步為紫外線 (UV) 固化,該步驟可以除去不穩定相,從而誘導空隙形成,并重建和強化其余的二氧化硅矩陣,以形成最終的納米多孔薄膜。

新一代的 Black Diamond 3 薄膜將這一行業領先的技術擴展為超低 K (ULK) 薄膜 (k~2.2),以便縮放到 22nm 及更先進節點,提升器件速度。它還能提供最新的先進封裝方案所需的機械強度(硬度和彈性)。該薄膜具有出色的抗濕性和極佳的機械強度,在刻蝕和去除光刻膠后具有穩定的 k 值。

這種兩步式沉積和固化工藝所實現的機械強度比應用材料公司取得成功的第二代 Black Diamond 薄膜高一倍,從而能夠降低器件變異性,并提高芯片的成品率。

有關 Black Diamond 3 工藝的更多技術信息,請訪問Producer Black Diamond PECVD頁面。

Applied ProducerXP PrecisionDracoCVD

當今全球的數字化轉型推動了對更低成本、更高密度DRAM芯片的需求,特別是在數據中心服務器應用領域。然而,物理上的設計局限限制了 DRAM 的縮放,無法跟上人工智能、5G、物聯網和其他數據密集型計算應用不斷增長的內存需求。

應用材料公司的 Producer XP Precision Draco硬掩模解決了 DRAM 存儲電容器縮放上的一個關鍵限制。

電容器為直徑約 30納米的超小型結構。它的電容與它的體積成正比。當電容器直徑隨著縮放而縮小時,必須增加其深寬比以保持電容不變。但是,隨著電容器通孔越來越深,高能離子在刻蝕通孔時也會刻蝕到硬掩模。深寬比越高,在完全形成電容器孔之前,硬掩模遭到腐蝕進而損壞器件的可能性就越大。

Draco 硬掩模采用一種新材料解決了這一問題,這種材料的選擇性比傳統 DRAM 電容器硬掩模高 30% 以上。它可以將沉積的硬掩模厚度減少 30%,從而縮小電容器的深寬比,降低刻蝕工藝的難度。

Draco 硬掩模與應用材料公司的的 CentrisSym3Y刻蝕系統一起協同優化,該系統經過特別調整以適合刻蝕這種新型材料,可將本地CD均勻性提高 50%,將橋接缺陷(短路)減少 100倍,從而提升良率。

-

晶圓

+關注

關注

52文章

5129瀏覽量

129238 -

邏輯器件

+關注

關注

0文章

88瀏覽量

20357 -

CVD

+關注

關注

1文章

76瀏覽量

10937

原文標題:Applied Materials產品庫----CVD篇

文章出處:【微信號:半導體設備與材料,微信公眾號:半導體設備與材料】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

CVD原理在睡眠時不起作用?

各種硬度計的原理、構造及應用與材料的關系

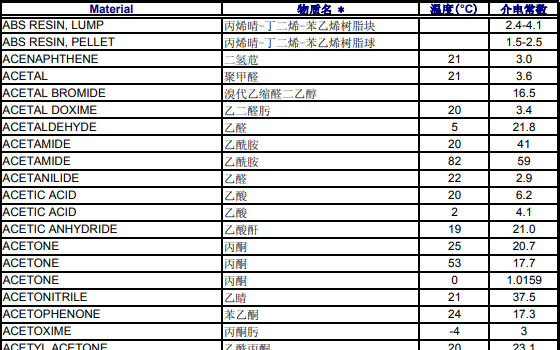

各種材料的相對介電常數詳細參考表免費下載

化學氣相沉積工藝(Chemical Vapor Deposition,CVD)

流量控制器在半導體加工工藝化學氣相沉積(CVD)的應用

拓荊科技:超高深寬比溝槽填充CVD產品首臺已通過客戶驗證

半導體FAB中常見的五種CVD工藝

用于半導體外延片生長的CVD石墨托盤結構

CVD薄膜質量的影響因素及故障排除

各種CVD材料介紹

各種CVD材料介紹

評論