1)LM3409是TI公司推出的一款LED恒流驅動芯片,芯片手冊和應用說明可以在官網查詢到參考資料,但是內部推導過程對于新手們可以參考一下介紹內容。

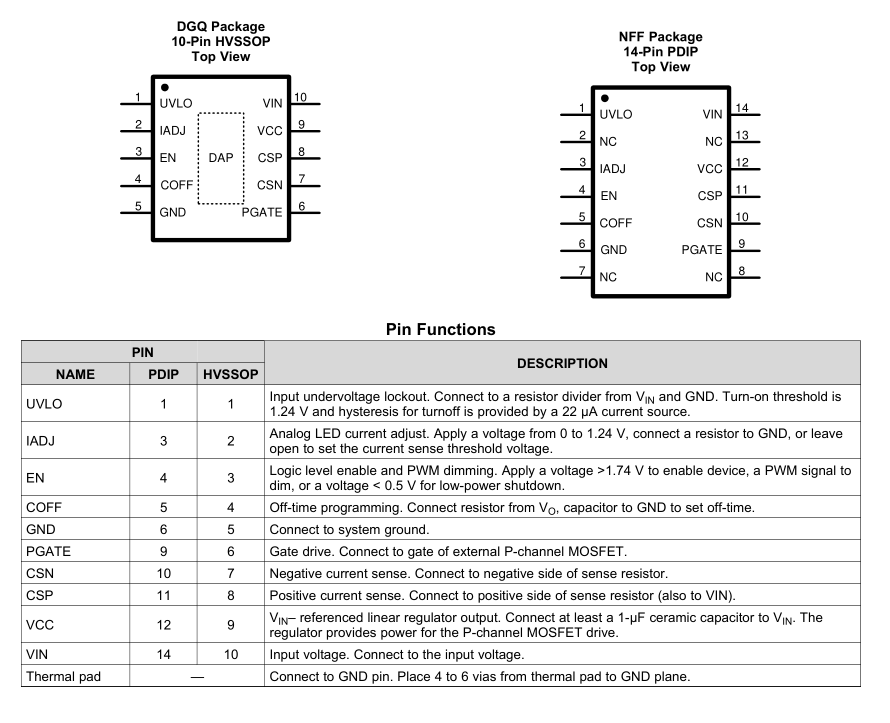

2)下圖是芯片的框圖和引腳介紹,尤其新手朋友們要先仔細閱讀手冊。

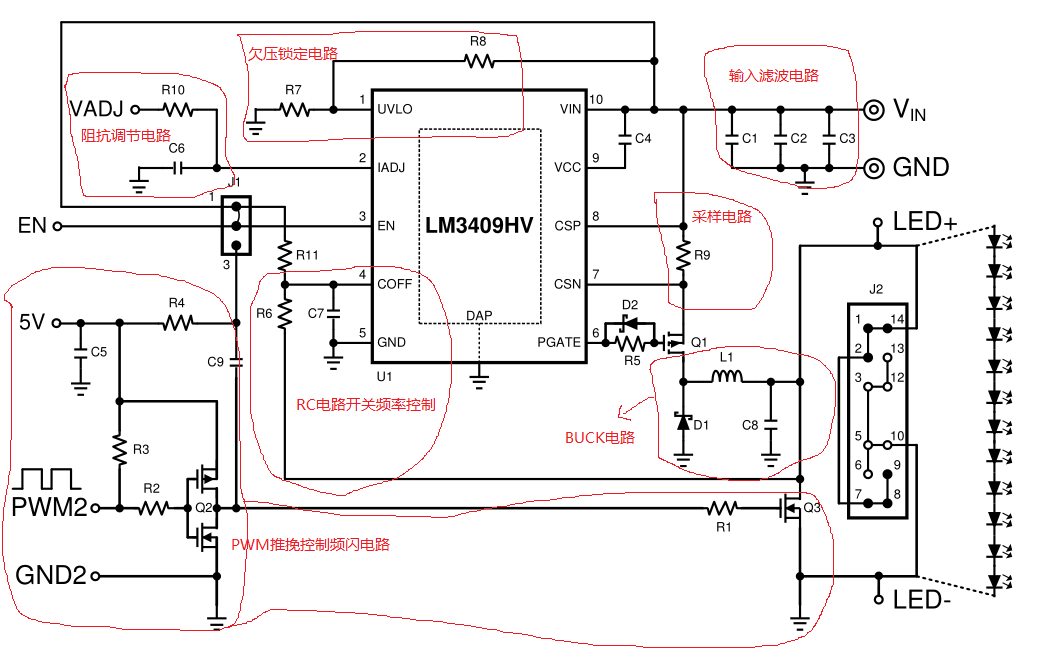

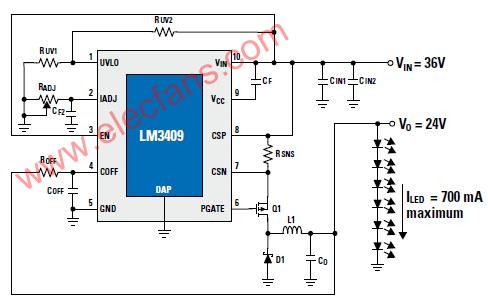

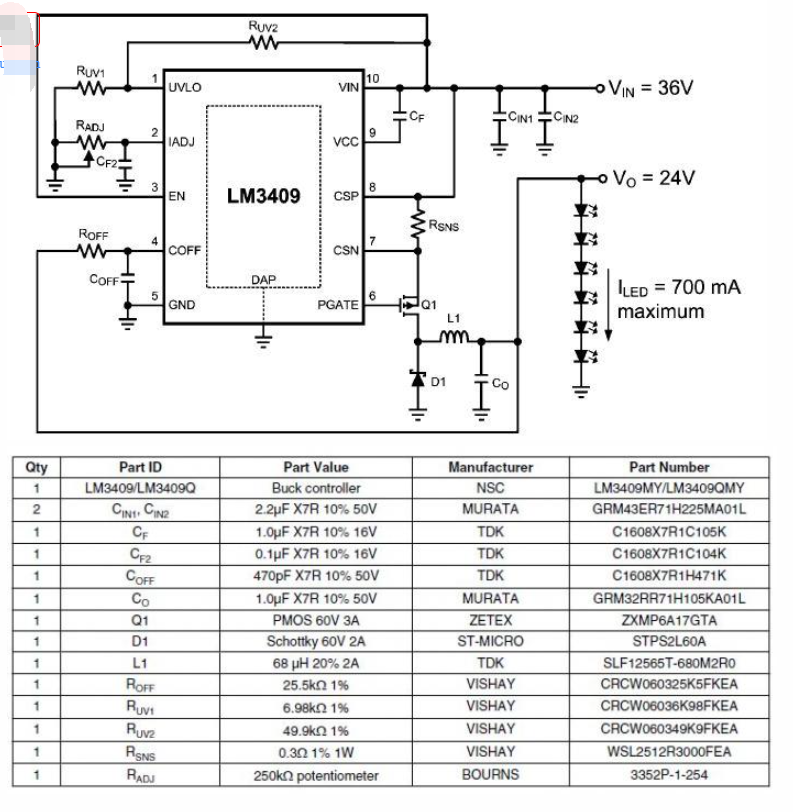

3)下面直接介紹應用電路及引腳中文描述,詳細電路推導接下來會介紹。

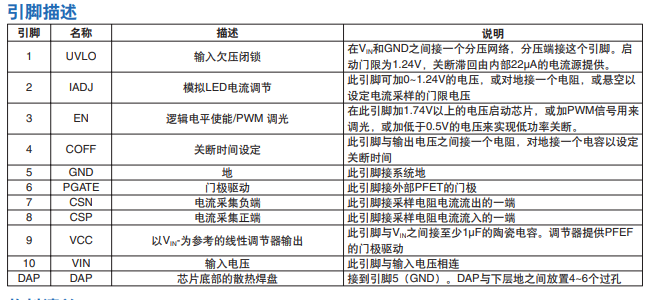

下圖為中文描述:

4)設計電路時必要知道的相關參數,此部分設計人員要提前規劃好。

VIN=48V;VIN-MAX=75V; 設定電路輸入標準電壓及最大輸入電壓;

VO=42V; 設定目標輸出電壓;

FSW=400kHz; 設定芯片開關控制頻率;

ILED=1.5A; 目標輸出電流;

△iLED-PP=△iL-PP=300mA; 設定輸出的紋波電流要求,峰峰值;

△VIN-PP=1.44V; 輸入的紋波電壓峰峰值;

η=0.97; 估算輸入電源效率;

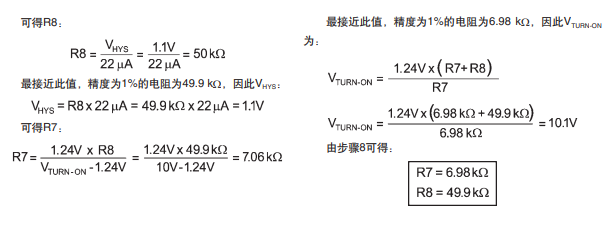

VTURN-ON=10V; VHYS=1.1V; 設定低壓保護值和遲滯電壓VHYS=1.1V;

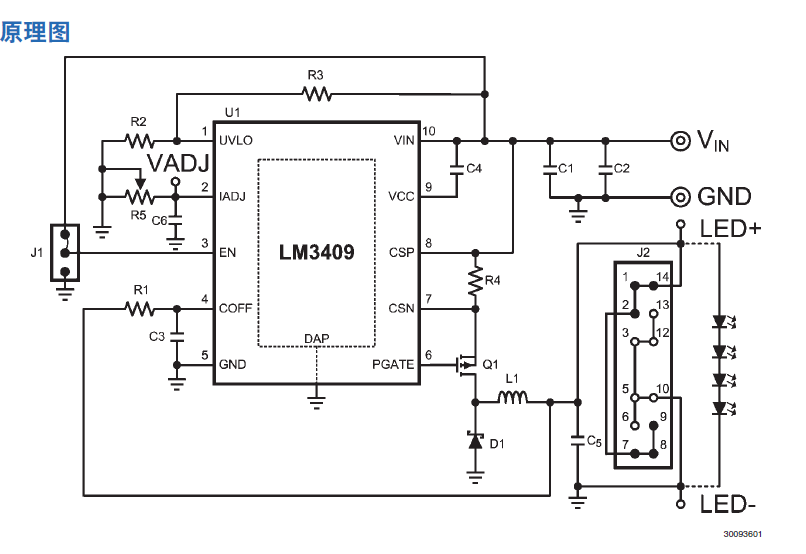

這里主要介紹一下UVLO欠壓鎖定引腳,此引腳電壓為人為設定低壓鎖定值VUVLO;配合遲滯電壓VHYS人為設定值。欠壓鎖定通過 VIN和 GND之間的電阻分壓器設置,并與 1.24V閾值進行比較,如圖28所示。一旦輸入電壓高于預設的 UVLO上升閾值(假設該器件已啟用),內部電路就會激活,并且 UVLO引腳上的 22μA電流源會打開。這個額外的電流提供滯后作用以創建一個較低的 UVLO下降閾值。

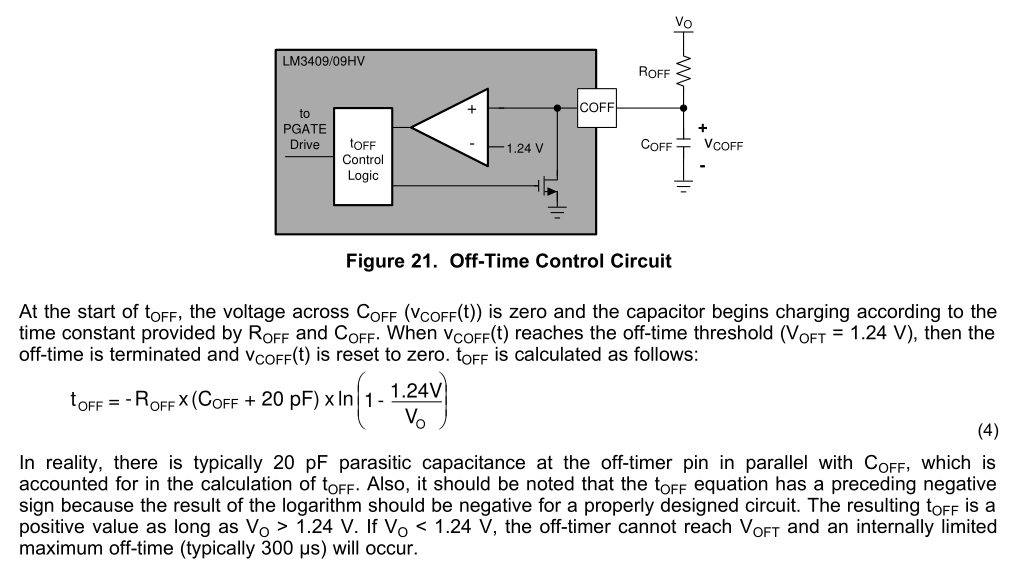

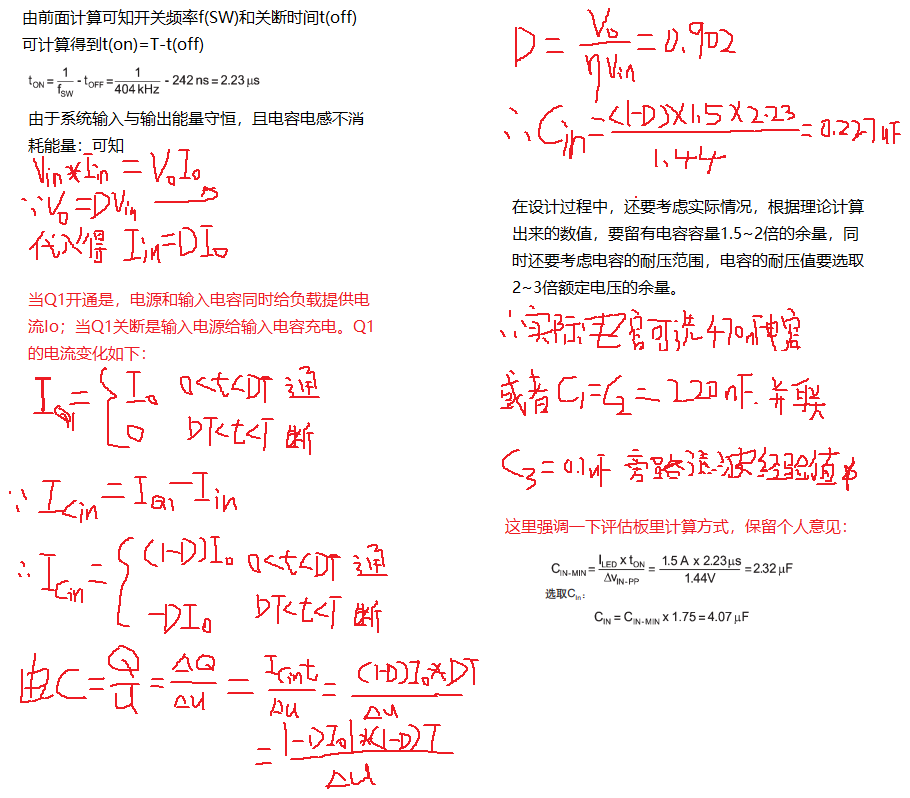

5)標稱開關頻率的計算過程

下圖是芯片內部及外圍的開關控制頻率的電路圖,此部分為RC電路。

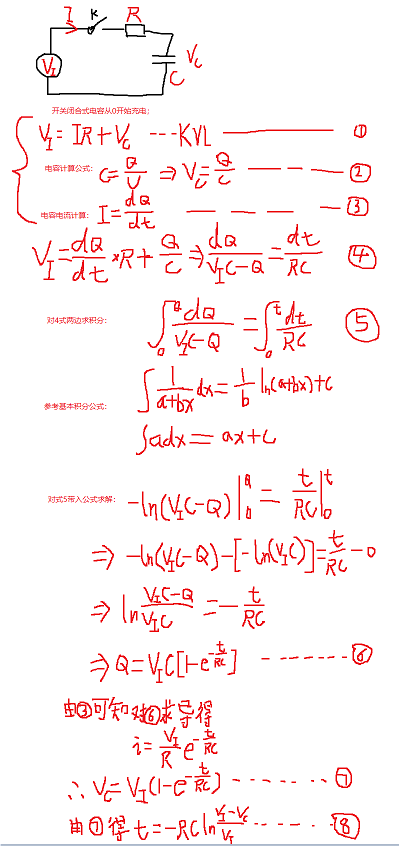

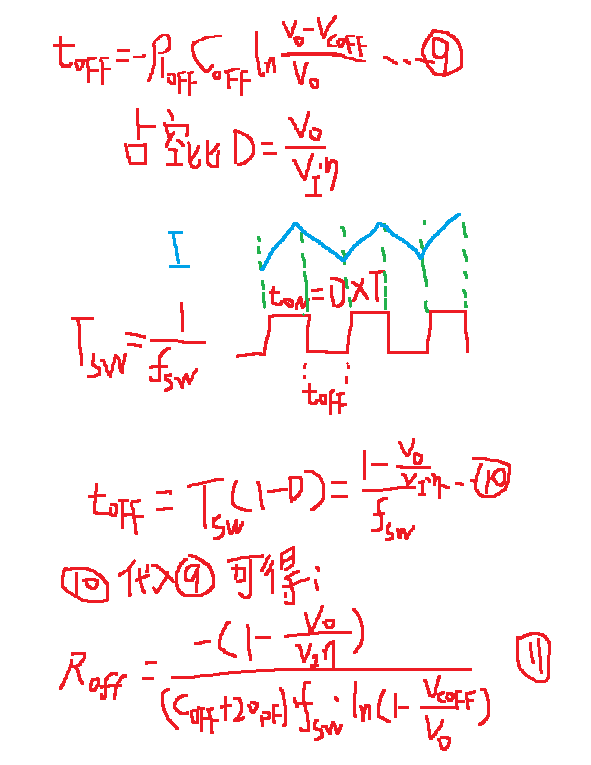

在tOFF開始時COFF兩端的電壓(VCOFF(t))為零,電容器開始根據 ROFF和 COFF提供的時間常數充電。當VCOFF(t)達到關閉時間閾值 (VOFT= 1.24V)時,關閉時間終止并且(VCOFF(t))重置為零。其中20pF是寄生電容;上述結果的推導見下圖。

接下來我們要計算電路中R6;首先我們要選型C7電容,即假定C7=470pF,并已知η=0.97;

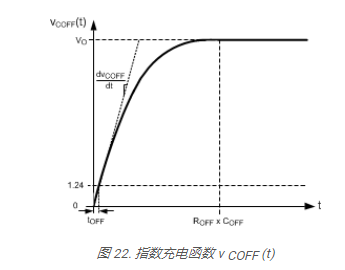

下圖是電容充電函數圖像:

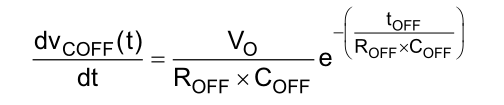

雖然tOFF方程是非線性的,但在大多數應用中tOFF實際上是非常線性的。忽略COFF引腳上的 20pF寄生電容,VCOFF(t)繪制在上圖中。可以計算VCOFF(t)的時間導數以找到tOFF方程的線性近似值:

對式7進行求導可得下式:

當 tOFF<< ROFFx COFF(相當于 VO>> 1.24V時),函數的斜率基本上是線性的,tOFF可以近似為給 COFF充電的電流源:

這里要知道開關頻率是用來調節BUCK電路的,這里引入一個BUCK電路占空比的概念后續會提供相關證明,BUCK電路如果電流過大開關會關閉,電流下降開關導通,這里存在導通和關斷時間概念;

由上圖計算可知:

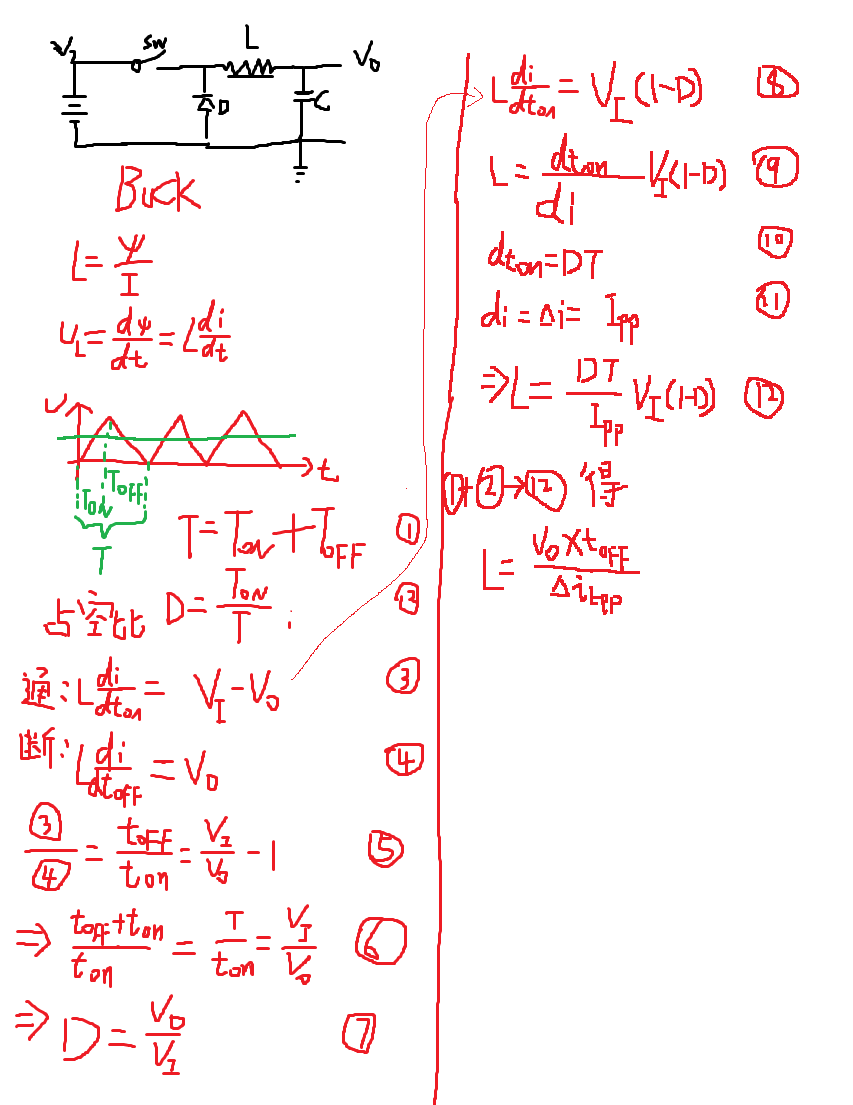

6)接下來是BUCK電路的計算推導;

首先要明白最基本的電感基本公式;開通和關斷時間為一個周期,占空比為開通所占整個周期的比例。

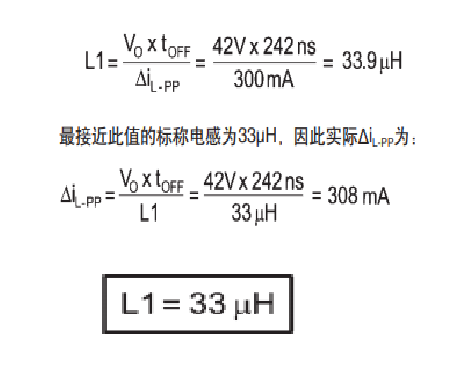

由上圖可知電感L1為:

7)下面是計算LED恒流和反饋電阻R9

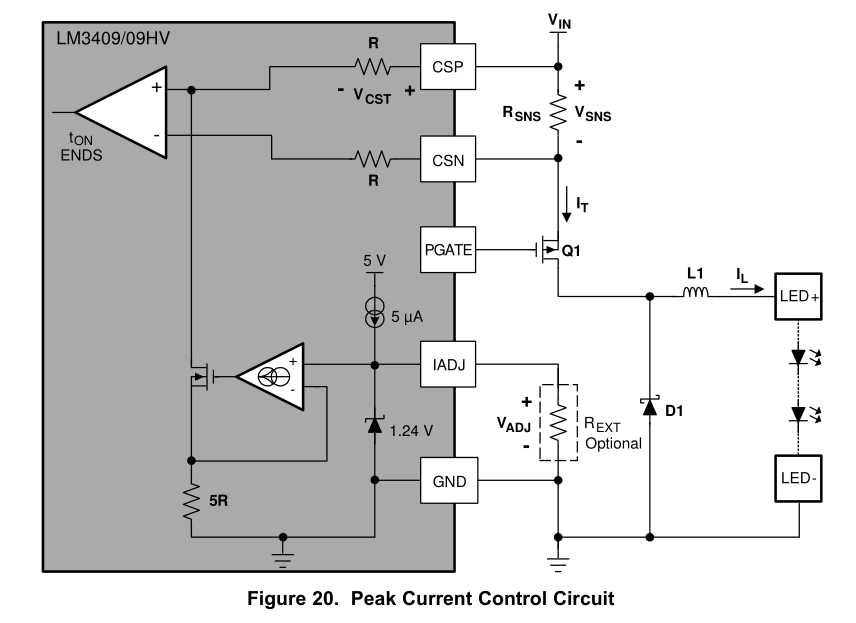

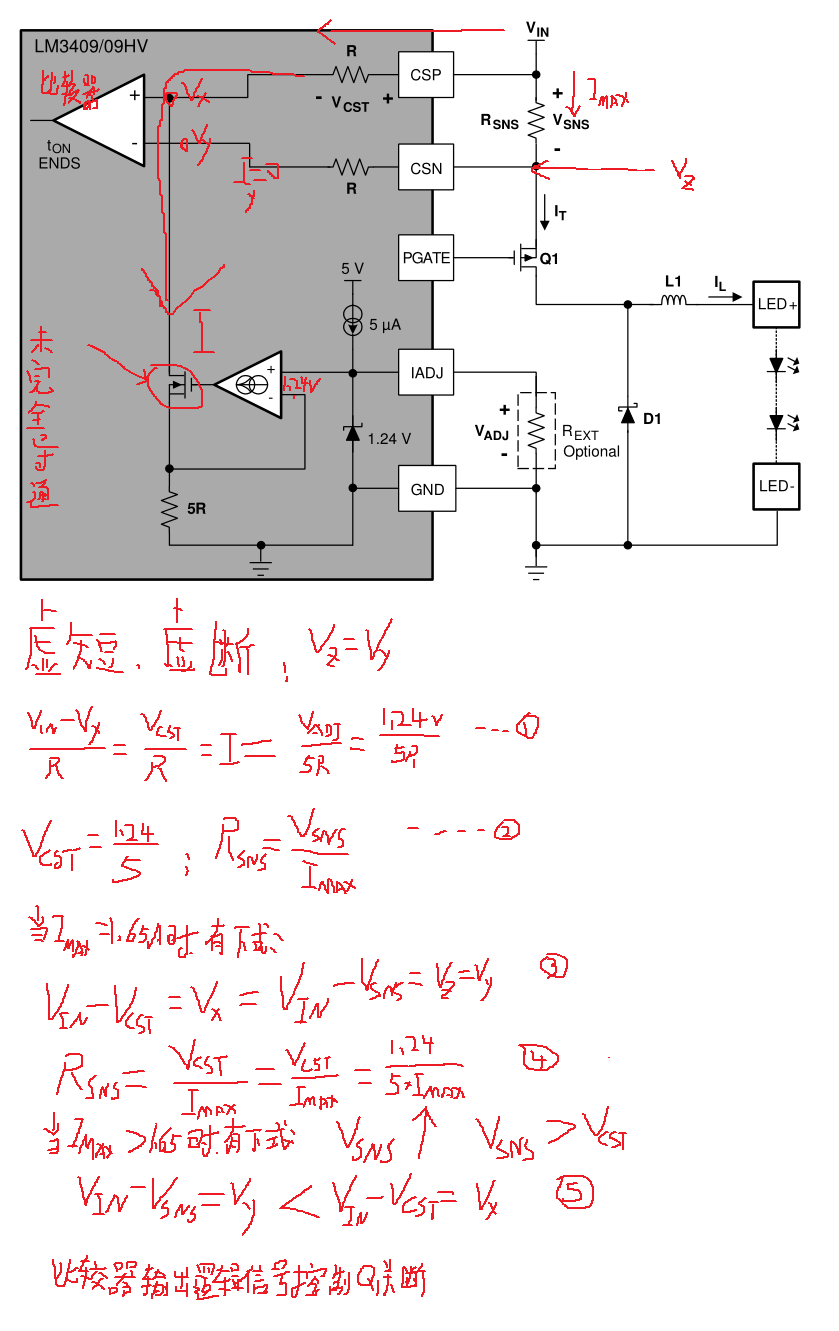

下圖是芯片內部框圖

由上圖可知芯片內部鉗位二極管旁邊是一個電壓跟隨器,上面運放是一個比較器。

在開關周期開始時,Q1導通,電感電流增加。一旦檢測到峰值電流,Q1關閉,二極管 D1正向偏置,電感器電流減小。上圖顯示了如何使用電流流過電阻器 (RSNS)時產生的差分電壓信號來完成峰值電流檢測。(RSNS)兩端的電壓(VSNS)與可調電流檢測閾值 (VCST)進行比較,當VSNS超過VCST時,Q1將關閉,前提是tON大于可能的最小 tON(通常為115ns)。

計算分析見下圖,由運放虛斷可知VZ=VY;通過下式推導可知比較器是比較(RSNS)兩端的電壓(VSNS)與可調電流檢測閾值 (VCST)進行比較。

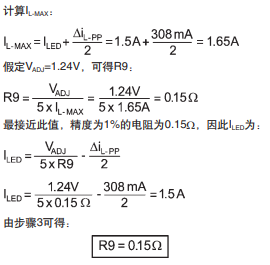

由上圖步驟4計算可知R9:

8)IADJ的作用

看芯片手冊可知IADJ引腳的作用是模擬 LED 電流調整。施加 0至 1.24 V的電壓,將電阻器連接到 GND,或懸空以設置電流檢測閾值電壓 (VCST)。有以下三種方式設置IADJ,結合第7節說明可知

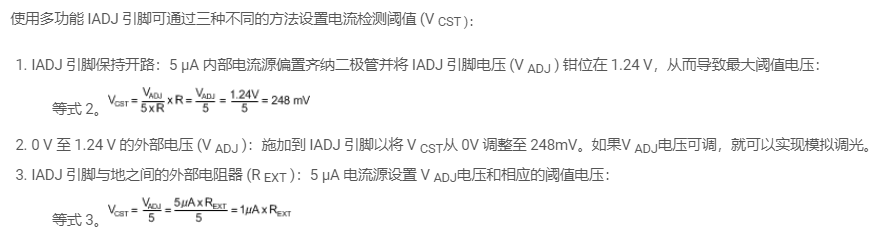

9)輸入電容的選擇

電源輸入端電容為去耦電容,有濾波和穩壓作用。

因為C=Q/U----------Q=C*U,I=dQ/dt---------I=d(C*U)/dt=C*dU/dt,C=I*dt/dU

從上式可以看出,濾波電容大小與電源輸出電流和單位時間電容電壓變化率有關系,且輸出電流越大電容越大,單位時間電壓變化越小電容越大;

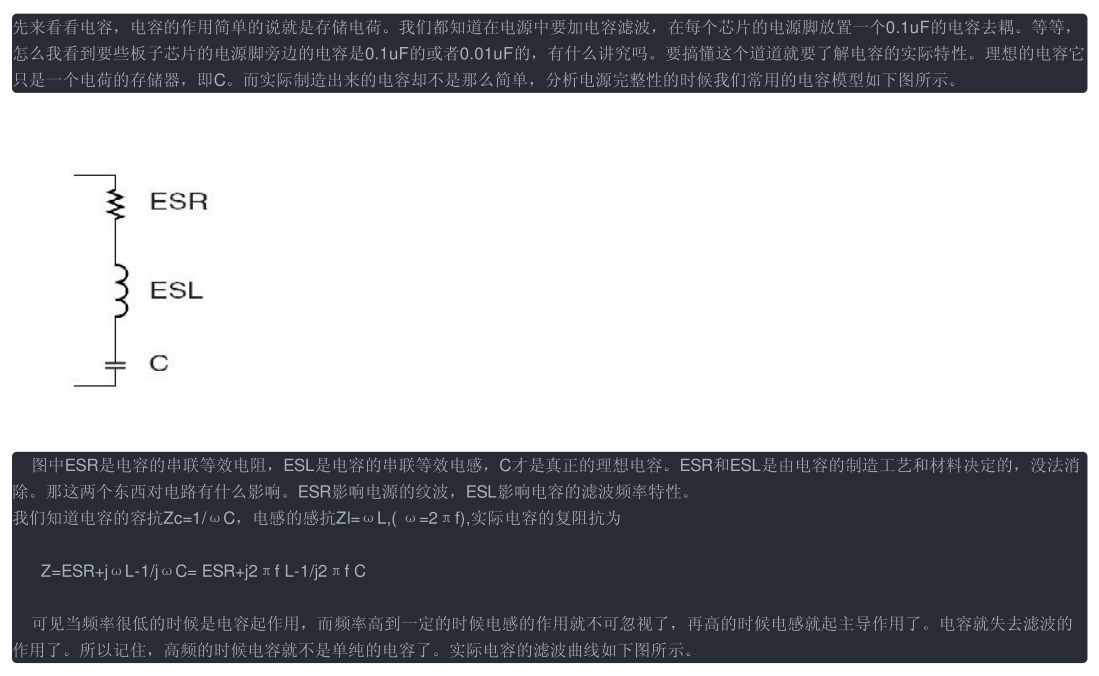

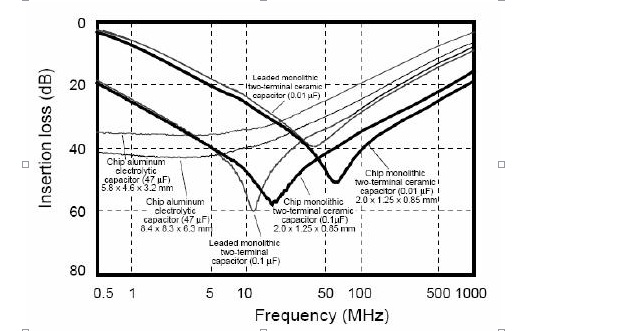

對于相同材料的電容器,容量越小,頻率特性越好。電容器的典型頻率特性是:隨著頻率的增加,總等效電容電抗減小,但當頻率增加到一定值時,電容電抗開始增大。如果將此頻率定義為電容電抗的轉折頻率,則電容越小,轉折頻率越高。因此,為了獲得相同的電容,可以將幾個小容量電容器并聯,這樣可以改善電容器的高頻特性。

這里給大家普及一下C3=0.1uf是怎么來的,我們的芯片IC內部的邏輯門在10-50Mhz范圍內執行的時候,芯片內部產生的干擾也在10-50Mhz,(比如51單片機),0.1uF電容 (有兩種,一種是插件,一種是貼片)的谷底剛好落在了這個范圍內,所以能夠濾除這個頻段的干擾。

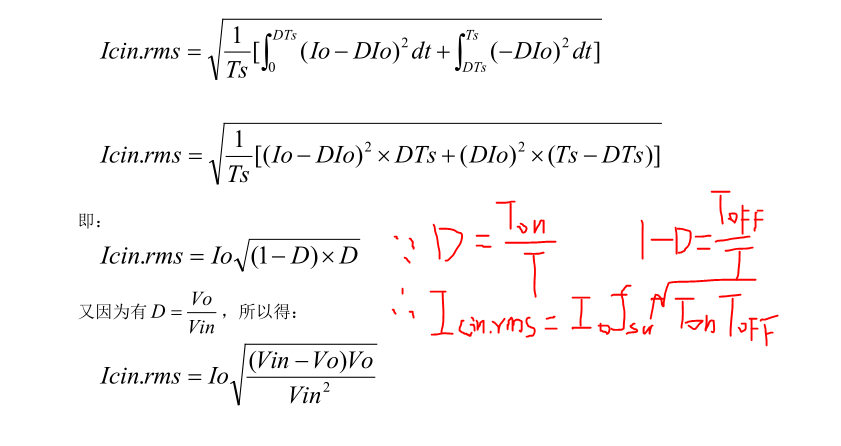

10)輸入電容紋波電流有效值計算

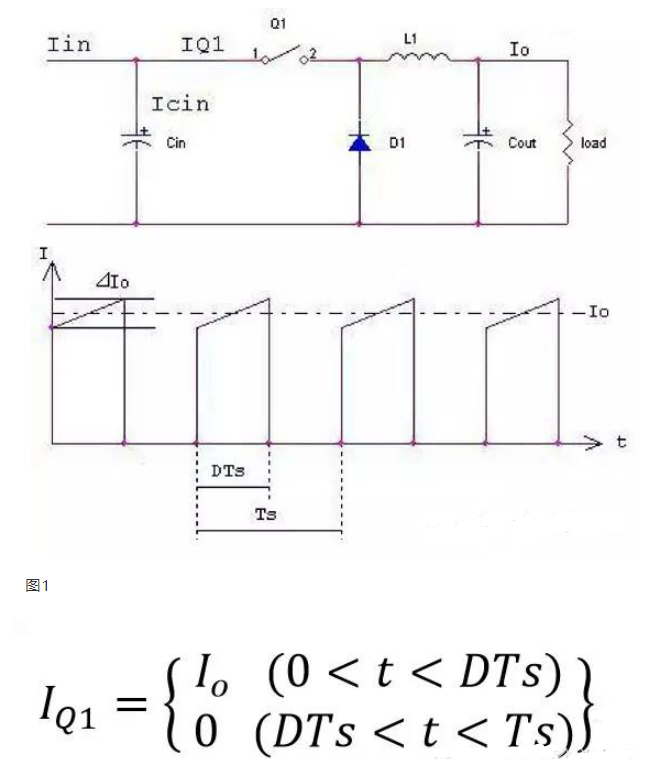

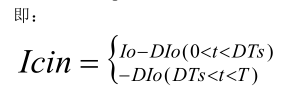

在Buck電路中Q1的電流(IQ1)波形基本如下圖所示:0~DTs期間為一半梯形,DTs~Ts期間為零。當0~DT期間Iq1⊿I足夠小時(不考慮輸出電流紋波的影響),則Iq1波形為近似為一個高為Io、寬為DTs的矩形,則有:

Iin* Vin =Vo*IoàIin=(Vo/Vin)*Io=DIo (Iin,只要Cin容量足夠大,則在整個周期中是基本恒定的;按照能量守恒定律:Pin≈Pout)

Icin=Iq1-Iin

對Icin的表達式可以這樣理解:在Q1導通期間輸入端電源和輸入電容共同向輸出端提供電流,因此輸入電容電流等于Q1電流減去輸入端電流;在Q1關斷期間輸入端對電容充電,以補充在Q1導通期間所泄掉的電荷,而此時電流方向與所定義的正向是相反的,所以有Icin=-DIo根據有效值的定義.

有效值定義:有效值(Effectivevalue)在相同的電阻上分別通以直流電流和交流電流,經過一個交流周期的時間,如果它們在電阻上所消耗的電能相等的話,則把該直流電流(電壓)的大小作為交流電流(電壓)的有效值,正弦電流(電壓)的有效值等于其最大值(幅值)的1/√2,約0.707倍。

在正弦交流電流電中根據熱等效原理,定義電流和電壓的有效值為其瞬時值在一個周期內的方均根值。

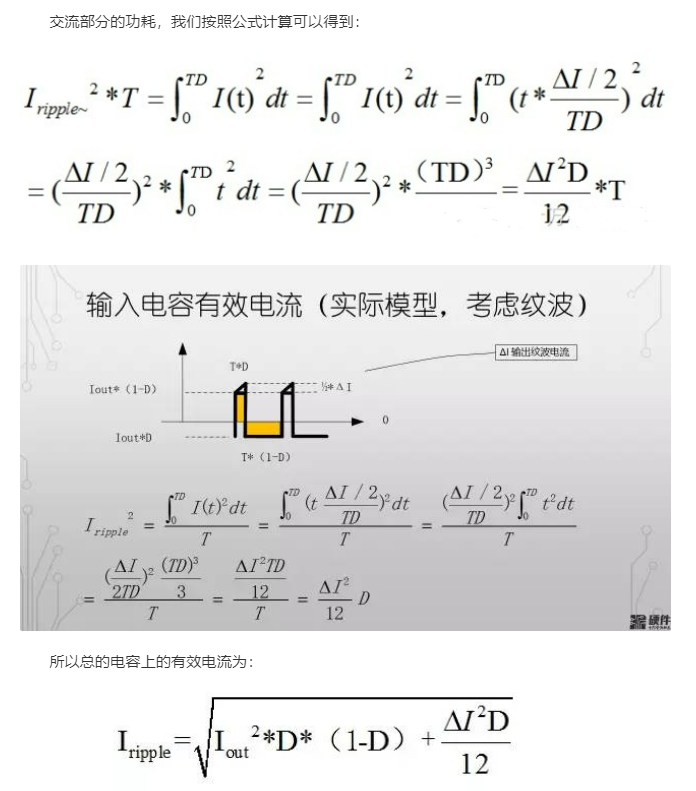

注:上式是在不考慮紋波影響的前提下計算得來的,若要考慮紋波⊿I,相當于在直流I0的基礎上疊加上了一個交流成分,

11)輸出電容的選擇和計算

輸出電容器需要保持直流輸出電壓。建議使用陶瓷或者CAP(鉭電容);使用陶瓷電容時,開關頻率處的阻抗由電容決定。輸出電壓紋波主要由電容引起。

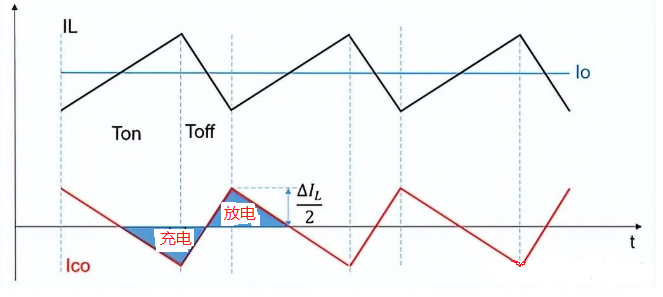

我們設計時總是按照電感電流諧波全部進入Co,恒定分量進入負載( 如果帶阻性負載,在閉環電路的控制下,輸出電壓恒定,確實是這樣的)。即電感上直流部分IO全部給與負載,電感上的交流(三角波部分)給到了電容。也就是交流部分給電容充放電。

下面詳細介紹輸出電容工作流程,在Q1導通時電感感應電動勢最大,電流最小,導通時電感電流逐漸增大,當達到均值后,電感開始給電容充電,直到電感電流下降到均值后結束充電,然后電感開始電流繼續減小此時電容開始放電給負載。

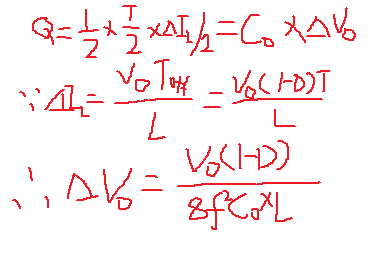

其輸出電壓紋波的計算公式推導如下:

電容充放電的總電荷量可用電流乘以時間計算,即為上圖中三角形的面積

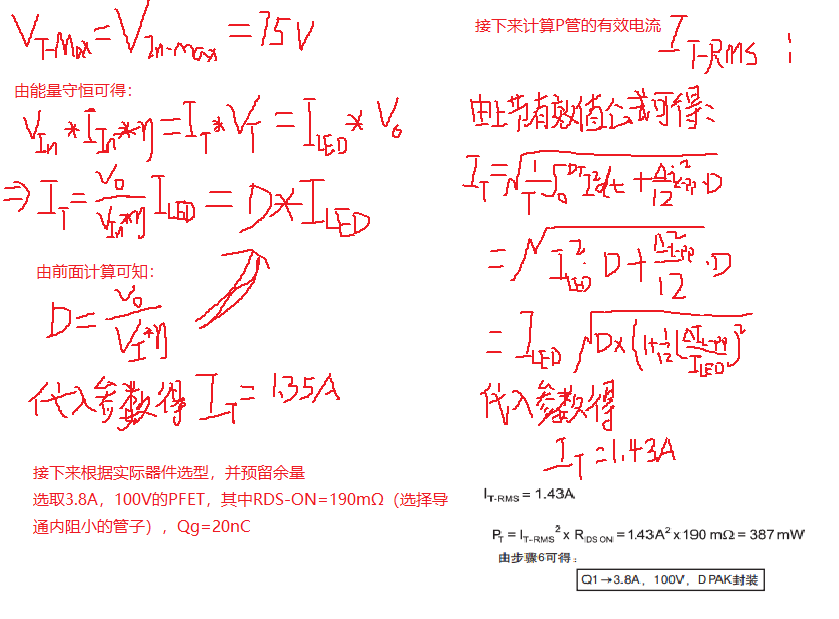

12)P溝道MOS管選型計算

根據電路圖可知P管的耐壓VT與輸入最大電壓有關,P管的導通電流IT可根據能連守恒計算,見下圖:

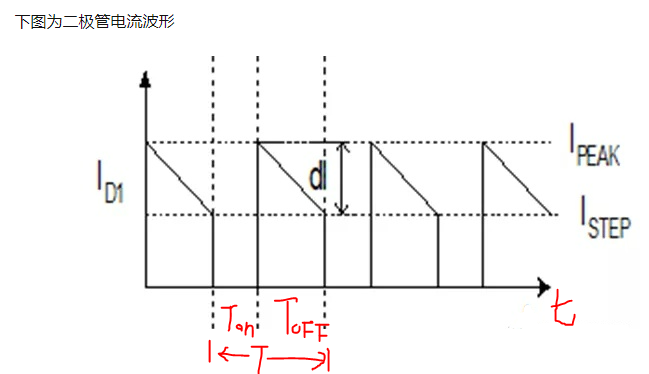

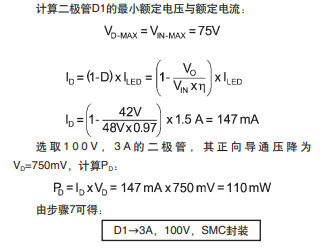

13)續流二極管的選型

首先要明白二極管D1在PFET管Q1關閉(TDs~T)時即T(1-D)時間內,電感L1產生反向電動勢進行續流的。續流二極管選取要求,選擇額定正向平均電流大于等于1.5-2倍,反向重復峰值電壓大于等于1.5-2倍,正向壓降小,反向漏電流小,反向恢復時間段等.

P管關閉后,二極管平均電流ID*T=ILED*(1-D)T;即ID =ILED*(1-D)。

反向擊穿電壓

在二極管截止時,將會承受最大的反向電壓Urev,Urev =Vin

在選取二極管時,需要選擇比這個電壓高的

平均電流:ID=IO·(1-D);IPEAK峰值電流:最大電流等于電感電流的最大值

IDMAX = Ipeak=Io + ? ·?I

額定功率:Pd = ID·VF,選用的二極管能承受這個消耗功率且要留有余量

正向導通電壓VF:

二極管的正向導通電壓VF越小,功率消耗就越小,所以要盡可能地選擇VF比較小的

反向恢復時間trr:

在開關電路中,一定要選擇反向恢復時間快的二極管,不然電路會工作異常。按反向恢復速度快慢分類:普通整流二極管 > 500ns ,快恢復二極管(150, 500)ns,超快恢復二極管(10,150)ns,肖特基二極管<10 ns。

14)輸入欠壓閉鎖

如果一個芯片有欠壓關斷,就會有閾值(閾值可以理解為臨界值)電壓,低于這個閾值電壓芯片就會自動停止運行(也就是關斷),高于這個閾值,芯片就會重新啟動。如果芯片啟動后,假如閾值電壓為10V,當電壓在10V臨界波動時,噪聲干擾都可能造成這種小的波動,于是在這個閾值附近芯片會不斷的啟停。遲滯電壓就是解決這一問題的,如果設置遲滯電壓為1.1V,則電壓為10V時芯片開啟,電壓電壓波動下降到8.9V時芯片才會徹底停止工作,這樣就解決了不斷的波動不斷的啟停。

VUVLO=10V;VHYS=1.1V; 設定低壓保護值和遲滯電壓;

根據上圖推算,代入數據后根據實際選型可得如下:

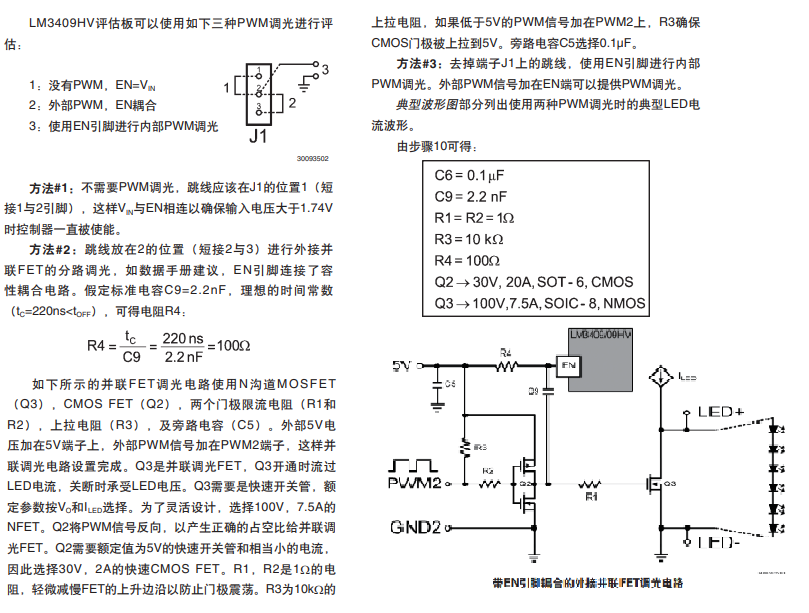

15)PWM調光方法

這里可以參照評估板的設計思路,PWM調光的好處是可以用軟件進行調光,方便快捷。

16)EN引腳內部調光電路介紹

啟用引腳 (EN)是用于 LED PWM調光的 TTL兼容輸入。EN的邏輯低電平(低于 0.5V)將禁用內部驅動器并切斷流向 LED陣列的電流。當 EN引腳處于邏輯低電平狀態時,支持電路(驅動器、帶隙、V CC穩壓器)保持活動狀態,以最大限度地減少在 EN引腳出現邏輯高電平(高于 1.74 V)時重新打開 LED陣列所需的時間。

17)旁路電容

這里大家需要理解旁路電容與去耦電容的概念,旁路電容是把輸入信號中的干擾作為濾除對象,而去耦電容是把輸出信號的干擾作為濾除對象,防止干擾信號返回電源。

我們經常提到去耦、耦合、濾波等說法,是從電容器在電路中所發揮的具體功能的角度去稱呼的,這些稱呼屬于同一個概念層次,而旁路則只是一種途徑,一種手段,一種方法。

比如,我們可以這么說:電容器通過將高頻信號旁路到地而實現去耦作用。因此,數字芯片電源引腳旁邊100nF的小電容,你可以稱之為去耦電容,也可以稱之為旁路電容,都是沒有錯的,如果你要強調的是去耦作用,則應該稱其為去耦電容,有些日本廠家的數據手冊比較講究,文中講的是去耦電路,就會以“旁路(去耦)電容器”來表示。

-

buck電路

+關注

關注

28文章

487瀏覽量

47407 -

LM3409

+關注

關注

0文章

5瀏覽量

8634 -

恒流電路

+關注

關注

3文章

52瀏覽量

12672

發布評論請先 登錄

基于LM3409芯片的LED恒流驅動電路設計

請問能否單獨改為12V給LM3409供電?

【WEBENCH 大賽作品】LED

請教各位大神,在proteus中繪制LM3409HV調光電路時,怎么找到LM3409HV這個芯片,找了好久沒找到

請教各位大神,在proteus中繪制LM3409HV調光電路時,怎么找到LM3409HV這個芯片,找了好久沒找到

用于 LM3409的非同步降壓控制器PMP7755技術資料下載

LM3409/LM3409HV,pdf datasheet

LM3409—可驅動高功率LED的PowerWise PFE

TILM3409演示板中文資料

采用LM3409P溝道MosFET設計的調光控制LED驅動器電路

基于LM3409芯片的恒流電路的設計

基于LM3409芯片的恒流電路的設計

評論