首先,我們需要理解什么是時(shí)鐘抖動(dòng)。簡而言之,時(shí)鐘抖動(dòng)(Jitter)反映的是時(shí)鐘源在時(shí)鐘邊沿的不確定性(Clock Uncertainty)。例如,假定我們現(xiàn)在有一個(gè)頻率為100MHz的時(shí)鐘,那么時(shí)鐘周期就是10ns,理想情況下,時(shí)鐘的上升沿將會出現(xiàn)在0ns,10ns,20ns……基于此,如果已知時(shí)鐘上升沿出現(xiàn)在30ns,這樣我們就可以得出下一個(gè)上升沿將會出現(xiàn)在40ns。但實(shí)際情況是,下一個(gè)上升沿很可能介于39.9ns到40.1ns之間。也就是說,有0.1ns對時(shí)鐘周期構(gòu)成了影響。就FPGA設(shè)計(jì)而言,對于抖動(dòng)我們理解這么多就足夠了。

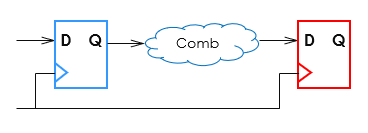

接下來我們看一下時(shí)鐘抖動(dòng)對時(shí)序性能的影響。以經(jīng)典的單周期時(shí)序路徑為例(收發(fā)時(shí)鐘為同一個(gè)時(shí)鐘且建立時(shí)間Requirement為一個(gè)時(shí)鐘周期),如下圖所示。

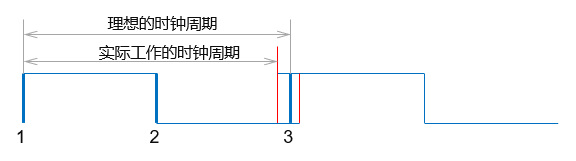

就建立時(shí)間而言,基于靜態(tài)時(shí)序分析(STA)理論,假定數(shù)據(jù)發(fā)起沿為下圖邊沿1,那么捕獲沿將是邊沿3。如果邊沿1出現(xiàn)在20ns這一時(shí)刻,那么邊沿3可能出現(xiàn)在以下兩個(gè)時(shí)刻:

20+Clock Period+Jitter

20+Clock Period-Jitter

考慮最壞情況,我們應(yīng)該按照20+Clock Period-Jitter來評估建立時(shí)間裕量。換言之,實(shí)際的時(shí)鐘周期為Clock Period-Jitter。

再看保持時(shí)間,發(fā)起沿和捕獲沿都是邊沿1,或都是邊沿3,即發(fā)起沿和捕獲沿是同一時(shí)鐘的同一個(gè)上升沿,故抖動(dòng)不會對保持時(shí)間裕量產(chǎn)生影響。

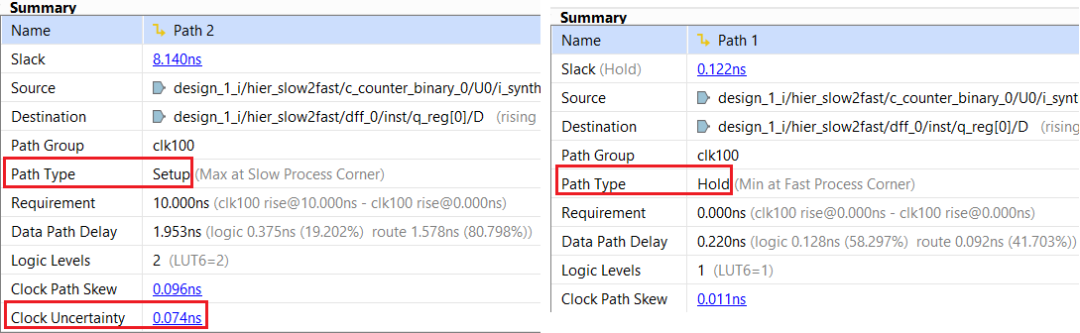

基于此,我們可以得出如下結(jié)論:對于發(fā)送時(shí)鐘和接收時(shí)鐘是同一時(shí)鐘的單周期路徑,時(shí)鐘抖動(dòng)對建立時(shí)間有負(fù)面影響,但對保持時(shí)間沒有影響。這一點(diǎn),在Vivado的時(shí)序報(bào)告中也可以看到。如下圖所示,圖中左側(cè)為建立時(shí)間時(shí)序報(bào)告,可以看到Clock Uncertainty,而右側(cè)為保持時(shí)間時(shí)序報(bào)告,是沒有Clock Uncertainty。

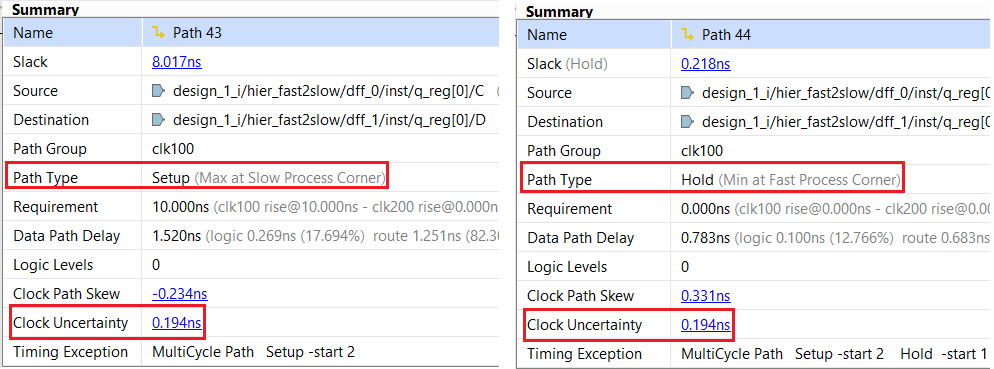

如果發(fā)送時(shí)鐘和接收時(shí)鐘是不同時(shí)鐘呢?假定發(fā)送時(shí)鐘為200MHz,接收時(shí)鐘為100MHz,兩者由同一個(gè)MMCM生成,故二者為同步時(shí)鐘。兩者之間的跨時(shí)鐘域路徑可采按多周期路徑進(jìn)行約束。毋庸置疑,抖動(dòng)仍然會對建立時(shí)間有負(fù)面影響。對于保持時(shí)間,發(fā)起沿是200MHz時(shí)鐘的上升沿,捕獲沿是100MHz的上升沿,不是同一個(gè)邊沿,故要將100MHz的時(shí)鐘抖動(dòng)考慮在內(nèi)。

根據(jù)保持時(shí)間的定義:數(shù)據(jù)被時(shí)鐘有效沿采樣到之后仍要穩(wěn)定保持一段時(shí)間,這個(gè)時(shí)間即為保持時(shí)間。考慮最壞情況,抖動(dòng)使得時(shí)鐘采樣沿后移,意味著數(shù)據(jù)需要保持更長的時(shí)間即Th+Jitter。因此,此時(shí),抖動(dòng)對保持時(shí)間也是一種惡化。這一點(diǎn)在Vivado的時(shí)序報(bào)告中也會有所體現(xiàn)。

審核編輯:劉清

-

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

27248 -

時(shí)鐘抖動(dòng)

+關(guān)注

關(guān)注

1文章

63瀏覽量

16162 -

STA

+關(guān)注

關(guān)注

0文章

52瀏覽量

19264

原文標(biāo)題:時(shí)鐘抖動(dòng)會影響建立時(shí)間和保持時(shí)間違例嗎?

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

靜態(tài)時(shí)序之建立時(shí)間和保持時(shí)間分析

芯片設(shè)計(jì)進(jìn)階之路—從CMOS到建立時(shí)間和保持時(shí)間

淺析D觸發(fā)器的建立時(shí)間和保持時(shí)間物理含義

數(shù)字電路中,建立時(shí)間和保持時(shí)間對于觸發(fā)器的時(shí)鐘信號有

建立時(shí)間和保持時(shí)間討論

FPGA實(shí)戰(zhàn)演練邏輯篇51:建立時(shí)間和保持時(shí)間

保持時(shí)間與建立時(shí)間

數(shù)字 IC 筆試面試必考點(diǎn)(9)建立時(shí)間以及保持時(shí)間 精選資料分享

建立時(shí)間和保持時(shí)間(setup time 和 hold time)

到底什么是建立時(shí)間/保持時(shí)間?

SOC設(shè)計(jì)中的建立時(shí)間和保持時(shí)間

PCB傳輸線建立時(shí)間、保持時(shí)間、建立時(shí)間裕量和保持時(shí)間裕量

關(guān)于建立時(shí)間和保持時(shí)間的測量方法

時(shí)鐘抖動(dòng)會影響建立時(shí)間和保持時(shí)間違例嗎?

時(shí)鐘抖動(dòng)會影響建立時(shí)間和保持時(shí)間違例嗎?

評論