IC封裝的熱特性對于IC應用的性能和可靠性來說是非常關鍵的。本文描述了標準封裝的熱特性:熱阻(用“theta”或Θ表示),ΘJA、ΘJC、ΘCA,并提供了熱計算、熱參考等熱管理技術的詳細信息。

引言

為確保產品的高可靠性,在選擇IC封裝時應考慮其熱管理指標。所有IC在有功耗時都會發熱,為了保證器件的結溫低于最大允許溫度,經由封裝進行的從IC到周圍環境的有效散熱十分重要。本文有助于設計人員和客戶理解IC熱管理的基本概念。在討論封裝的熱傳導能力時,會從熱阻和各“theta”值代表的含義入手,定義熱特性的重要參數。本文還提供了熱計算公式和數據,以便能夠得到正確的結(管芯)溫度、管殼(封裝)溫度和電路板溫度。

熱阻的重要性

半導體熱管理技術涉及到熱阻,熱阻是描述物質熱傳導特性的一個重要指標。計算時,熱阻用“Theta”表示,是由希臘語中“熱”的拼寫“thermos”衍生而來。熱阻對我們來說特別重要。

IC封裝的熱阻是衡量封裝將管芯產生的熱量傳導至電路板或周圍環境的能力的一個標準。給出不同兩點的溫度,則從其中一點到另外一點的熱流量大小完全由熱阻決定。如果已知一個IC封裝的熱阻,則根據給出的功耗和參考溫度即可算出IC的結溫。

Maxim網站(制造商、布線、產品、QA/可靠性、采購信息)中給出了常用的IC熱阻值。

定義

以下章節給出了Theta (Θ)、Psi (Ψ)的定義,這些標準參數用來表示IC封裝的熱特性。

ΘJA是結到周圍環境的熱阻,單位是°C/W。周圍環境通常被看作熱“地”點。ΘJA取決于IC封裝、電路板、空氣流通、輻射和系統特性,通常輻射的影響可以忽略。ΘJA專指自然條件下(沒有加通風措施)的數值。

ΘJC是結到管殼的熱阻,管殼可以看作是封裝外表面的一個特定點。ΘJC取決于封裝材料(引線框架、模塑材料、管芯粘接材料)和特定的封裝設計(管芯厚度、裸焊盤、內部散熱過孔、所用金屬材料的熱傳導率)。

對帶有引腳的封裝來說,ΘJC在管殼上的參考點位于塑料外殼延伸出來的1管腳,在標準的塑料封裝中,ΘJC的測量位置在1管腳處。對于帶有裸焊盤的封裝,ΘJC的測量位置在裸焊盤表面的中心點。ΘJC的測量是通過將封裝直接放置于一個“無限吸熱”的裝置上進行的,該裝置通常是一個液冷卻的銅片,能夠在無熱阻的情況下吸收任意多少的熱量。這種測量方法設定從管芯到封裝表面的熱傳遞全部由傳導的方式進行。

注意ΘJC表示的僅僅是散熱通路到封裝表面的電阻,因此ΘJC總是小于ΘJA。ΘJC表示是特定的、通過傳導方式進行熱傳遞的散熱通路的熱阻,而ΘJA則表示的是通過傳導、對流、輻射等方式進行熱傳遞的散熱通路的熱阻。

ΘCA是指從管殼到周圍環境的熱阻。ΘCA包括從封裝外表面到周圍環境的所有散熱通路的熱阻。

根據上面給出的定義,我們可以知道:

ΘJA = ΘJC + ΘCA

ΘJB是指從結到電路板的熱阻,它對結到電路板的熱通路進行了量化。通常ΘJB的測量位置在電路板上靠近封裝的1管腳處(與封裝邊沿的距離小于1mm)。ΘJB包括來自兩個方面的熱阻:從IC的結到封裝底部參考點的熱阻,以及貫穿封裝底部的電路板的熱阻。

測量ΘJB時,首先阻斷封裝表面的熱對流,并且在電路板距封裝位置較遠的一側安裝一個散熱片。如下圖1所示:

圖1. ΘJB的測量過程示意圖.

ΨJB是結到電路板的熱特性參數,單位是°C/W。文章JESD51-12–Guidelines for Reporting and Using Package Thermal Information,明確指出熱特性參數與熱阻是不同的。與熱阻ΘJB測量中的直接單通路不同,ΨJB測量的元件功率通量是基于多條熱通路的。由于這些ΨJB的熱通路中包括封裝頂部的熱對流,因此更加便于用戶的應用。關于ΨJB參數的更多詳細說明請參考JEDEC標準的JESD51-8和JESD51-12部分。

設計者可以通過熱量建模或直接測量的方式確定ΘJB和ΨJB的值。對上述任意一種方式,參見下面的步驟:

將功耗控制在適合ΘJB或ΨJB的范圍內。

測定管芯溫度,通常用一個芯片上的二極管來實現。

測定在距封裝邊緣小于1mm處的PCB溫度。

測定功耗。

ΨJT是衡量結溫和封裝頂部溫度之間的溫度變化的特征參數。當封裝頂部溫度和功耗已知時,ΨJT有助于估算結溫。

熱計算

結溫

TJ = TA + (ΘJA × P)

其中:

TJ = 結溫

TA = 周圍環境溫度

P = 功耗,單位為W

TJ也可用ΨJB或ΨJT的值來計算,如:

TJ = TB + (ΨJB × P)

其中:

TB = 距離封裝小于1mm處的電路板溫度

TJ = TT + (ΨJT × P)

其中:

TT = 在封裝頂部的中心處測得的溫度。

注意:產品數據資料給出了每個器件所允許的最大結溫。

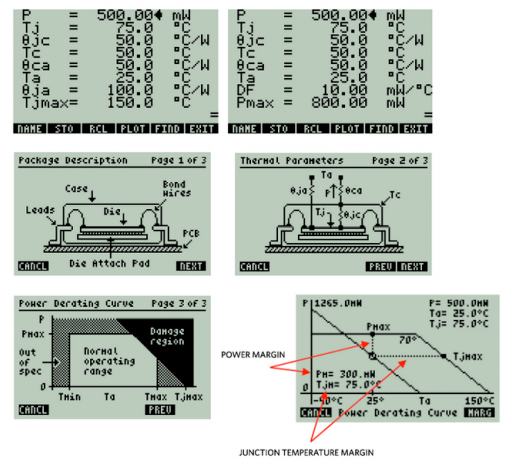

最大允許功耗

Pmax = (TJ-max - TA) / ΘJA

Maxim產品中列出的最大允許功率是在環境溫度為+70°C和最大允許結溫為+150°C的條件下給出的。

降額系數

該系數描述了在環境溫度高于+70°C時,每升高1°C所應降低的功耗值,單位為mW/°C。

降額系數 = P / (TJ - TA)

其中:

TA的典型值為+70°C (商用)。

TJ是最大允許結溫,典型值為+150°C。

為了得到在環境溫度超過+70°C時(例如,對于擴展溫度范圍的+85°C)的最大允許功率,可通過下面公式進行計算:

Pmax85C = Pmax70C - (降額系數 × (85 - 70))

熱特性及測試條件

IC封裝的熱特性必須采用符合JEDEC標準的方法和設備進行測量。在不同的特定應用電路板上的熱特性具有不同的結果。據了解JEDEC中定義的結構配置不是實際應用中的典型系統反映,而是為了保持一致性,應用了標準化的熱分析和熱測量方法。這有助于對比不同封裝變化的熱性能指標。

JEDEC規范可在這里得到:JEDEC。注意JEDEC標準涵蓋了不同的熱應用場合。

JEDEC規范名稱

JESD51: Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device)

JESD51-1: Integrated Circuit Thermal Measurement Method—Electrical Test Method (Single Semiconductor Device)

JESD51-2: Integrated Circuit Thermal Test Method Environmental Conditions—Natural Convection (Still Air)

JESD51-3: Low Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

JESD51-4: Thermal Test Chip Guideline (Wire Bond Type Chip)

JESD51-5: Extension of Thermal Test Board Standards for Packages with Direct Thermal Attachment Mechanisms

JESD51-6: Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air)

JESD51-7: High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

JESD51-8: Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board

JESD51-9: Test Boards for Area Array Surface Mount Package Thermal Measurements

JESD51-10: Test Boards for Through-Hole Perimeter Leaded Package Thermal Measurements.

JEDEC51-12: Guidelines for Reporting and Using Electronic Package Thermal Information.

JEDEC多層熱測試電路板規范JESD51-7摘要

High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages

JESD51-7規范中描述的熱測試電路板非常適合Maxim IC的應用。

材質:FR-4

板層:兩個信號層(頂層和底層)和兩個中間層。

成品板厚:1.60 ±16mm

金屬厚度

頂層和底層:2盎司銅(成品厚度0.070mm)

兩個中間層:1盎司銅(成品厚度0.035mm)

介質層厚度:0.25mm到0.50mm

板尺寸:76.20mm x 114.30mm ±0.25mm (對于某一邊小于27mm的封裝)。

元件層的布線

測試設備放在電路板中心位置,并根據此進行布線。走線從封裝本體向外延伸至少25mm。對于引腳間距為0.5mm或更大的封裝,線寬應為0.25 ±10%,對引腳間距更小的封裝來說,線寬應與引腳寬度相等。走線類型和走線端接規范在JESD51-7中有詳細的說明。

底層的布線

器件層端接到通孔的布線可以通過走線或線纜(22 AWG或更小的銅線)連接到邊緣連接器。JESD51-7規范中詳細列出了不同線寬對應的電流限度。

除通孔隔離布線模式外,電源和地平面應當保持完整,且與邊緣連接器的距離應當大于9.5mm。

帶裸焊盤的封裝

對于帶裸焊盤(EP)的封裝(如QFN封裝,DFN封裝(雙列扁平無外伸引腳),EP-TQFP封裝),其熱特性中非常重要的一點是裸焊盤焊點下方的散熱過孔的設計。在典型的熱特性電路板設計中,會有一個包含4個、9個或16個通孔的陣列,就近連接到地平面上。通孔數量超過25個以后,散熱改進基本趨于平緩,不會再有顯著的改善。理解電路板上的散熱通孔與系統熱特性之間的對應關系是十分重要的。關于帶裸焊盤封裝的電路板設計請參見JESD51-5。

焊接覆蓋率

用戶焊接電路板時,應當保證焊點的覆蓋率達到50%或者更高,當焊點的空白面積接近50%或更多時,將會由于未連接到散熱通孔而對熱阻產生嚴重的影響。

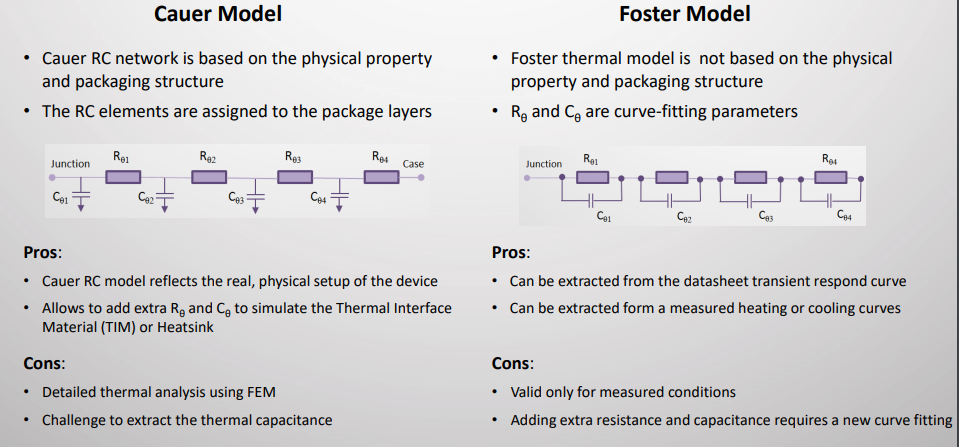

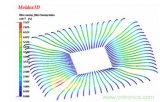

熱建模

采用FLOTHERM?和其它的熱分析軟件可以對封裝和系統實現精確的熱預測。適當的熱模型與經驗數據相結合,可以精確地反映實際應用的情況。

電路設計工具,如PSPICE或Cadence? toolscan可用來建立簡單的封裝熱模型。封裝可以表示成電阻的形式,以電阻網絡的方式連接到電路板上。確認封裝模型符合經驗數據后,該模型可用來預估封裝結構的變化情況,包括:管芯尺寸、裸焊盤尺寸、帶有保險絲的引腳、或連接到平面的地線數量。這些假設分析模型對于封裝結構的定制能夠給出相當精確的預估

審核編輯:郭婷

-

電路板

+關注

關注

140文章

5103瀏覽量

101785 -

封裝

+關注

關注

128文章

8561瀏覽量

144889 -

PCB

+關注

關注

1文章

2072瀏覽量

13204

發布評論請先 登錄

IC封裝熱阻的定義與量測技術

IC封裝的熱特性

IC封裝原理及功能特性匯總

關于IC封裝原理及功能特性分析和介紹

熱阻和熱特性參數的關鍵要點

漲知識:IC封裝原理及功能特性匯總

基于RC熱阻SPICE模型的GaNPX?和PDFN封裝的熱特性建模

IC封裝的熱特性

IC封裝的熱特性

評論