今年三月,英特爾、AMD、Arm、兩家領先的代工廠、Google Cloud、Meta、高通和 ASE 宣布,他們正在建立一種新的小芯片(chiplet)互聯開放標準,名為通用小芯片互聯技術(Universal Chiplet Interconnect Express,UCIe),旨在標準化小芯片的構建和相互通信方式。

過去幾年的一大趨勢是業內越來越多地使用多裸片先進封裝,作為構建硅基系統的一種方式,通常稱為系統級封裝(Systems-in-Package,SiP)。目前,小芯片 (chiplet) 之間的通信沒有什么重大的技術挑戰,至少沒有超出電路板上芯片通信的既有挑戰。而在沒有任何標準的情況下,所有 SiP 上的裸片都來自同一家公司(盡管通常是在多個半導體工藝節點上)。值得注意地, HBM 是一個例外(還有 HBM2 和 HBM3),JEDEC 參與了標準制定,Micron 等制造商提供了裸片堆棧,以便整合到基于高級封裝的設計中。

Universal Chiplet Interconnect Express (UCIe) 標準

只有當標準得到普遍采用時,才能最大程度體現其價值。因此,對于建立小芯片互聯開放標準,最重要的是哪些公司宣布加入其中。前文已經提到,最初的簽署名單是:

英特爾、AMD、Arm、兩家領先的代工廠、Google Cloud、Meta、高通和 ASE

在這些公司中,哪些公司實際上提供了符合標準的裸片,還有待觀察。當然,Arm 不生產芯片,代工廠也不設計芯片;但也許有一天,將有可能制造一個搭載英特爾 x86 處理器、Google TPU 和高通 5G 調制解調器的 SiP,并且所有這些都整合在同一個封裝中。

IP 公司沒有受邀參加最初的官宣活動,可能是因為需要邀請的半導體和系統公司已經足夠多。但我們將調整我們的 D2D(Die-to-Die)互連來遵循該標準——這樣說應該并不唐突。

顯然,UCIe 將效仿 PCIe(二者的名字都很相似)。PCIe 已經使大量供應商能夠制造可以成功協同工作的電路板和芯片;同樣,UCIe的目標則是使不同制造商的小芯片之間能夠有類似水平的互操作性。至于什么樣的商業環境能夠促成這一目標,還有待觀察。

至少,未來將應該有可能從多家公司購買裸片,并由這些公司制造裸片,然后當把這些裸片組裝在一個先進多裸片封裝時,它們可以順利協同工作。進一步說,未來將可能有公司配備現成的裸片庫存,從而消除等待生產這一過程。而更為理想的是,未來將可能有分銷商(或新公司類型)擁有來自多個制造商的裸片庫存,就像他們現在擁有封裝好的元件一樣。

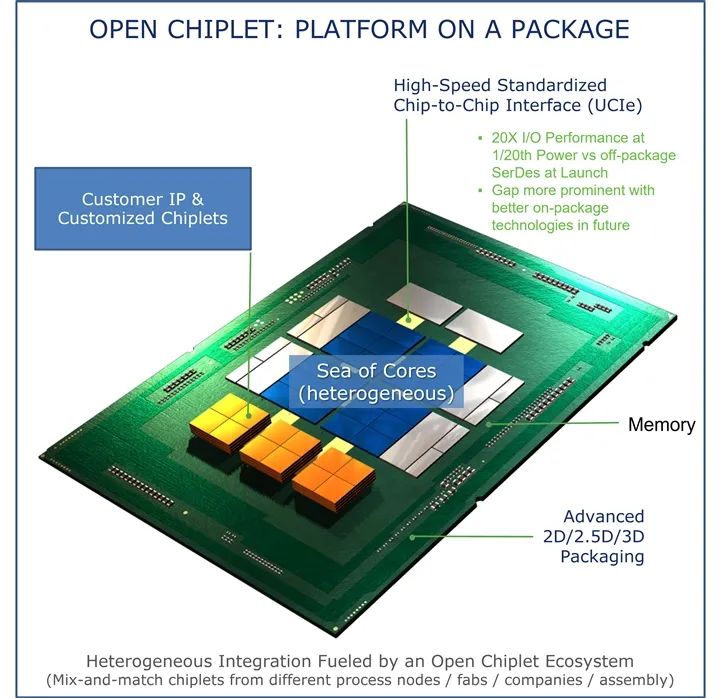

開發 D2D 互連的一個重要動機是,它比 PCB 上的芯片外連接具有更高的性能和更低的功耗。事實上,最初的產品發布承諾能夠以 1/20 的功耗獲得 20 倍的性能(見上圖的新聞稿)。

與 PCIe(和 USB)一樣,UCIe 標準最初的開發工作是由英特爾完成的,然后他們將該標準捐贈給后來成立的 UCIe 聯盟。與其最為相似的的標準實際上是高級互連總線 (Advanced Interconnect Bus ,AIB),最初也是由英特爾開發而后捐贈給CHIPS 聯盟;CHIPS 全稱為“Common Hardware for Interfaces, Processors, and Systems(接口、處理器和系統的通用硬件)”,專注于開源的硬件和工具。

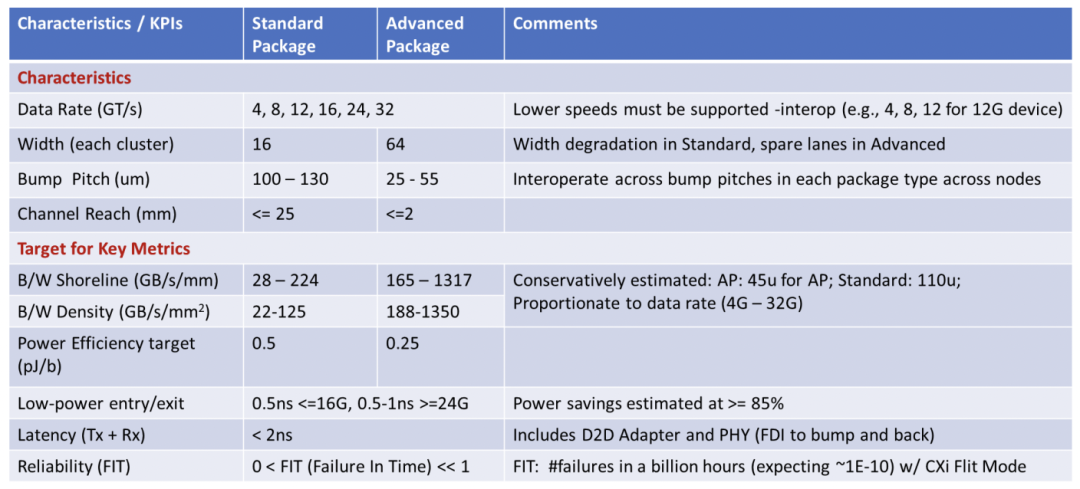

UCIe 顯然不僅僅是英特爾的標準,這一點可以從最初通告的簽署名單中看出。能讓英特爾、AMD 和 Arm 聯手合作,這件事必然意義重大。該規范包括物理層(電信號標準)和上面的協議層,并且詳細說明了支持的 bump 間距,這間接指定了可以使用的先進封裝技術。

上表對初始標準中的數字進行了更深入的分析。

在白皮書《Universal Chiplet Interconnect Express (UCIe): Building an Open Chiplet Ecosystem(UCIe:構建開放的芯片生態系統)》中,有這樣一段總結:

《UCIe:構建開放的芯片生態系統》

業界對一個開放的小芯片生態系統有巨大的需求,它將釋放整個計算連續體的創新。UCIe 1.0 提供了極高的能效和極具性價比的性能。事實上,它是一個具有即插即用模式的開放標準,以多個成功的標準為藍本,并由一群最合適不過的行業領導者推出,這將確保該標準被廣泛采用。我們預計下一代創新將發生在小芯片層面,而使小芯片組合能夠提供不同功能以供客戶選擇,將充分滿足客戶的應用要求。

-

芯片

+關注

關注

459文章

51927瀏覽量

433809

發布評論請先 登錄

相關推薦

新思科技與英特爾攜手完成UCIe互操作性測試

乾瞻科技宣布最新UCIe IP設計定案,推動高速傳輸技術突破

Alpahwave Semi推出全球首個64Gbps UCIe D2D互聯IP子系統

MATLA B助力數字與模擬芯片設計:高效實現HLS、UCIe和UVM

新思科技發布40G UCIe IP,加速多芯片系統設計

新思科技發布全球領先的40G UCIe IP,助力多芯片系統設計全面提速

小鵬汽車自主研發的智能駕駛芯片已順利完成流片階段

印度汽車制造商Ola預計2026年推出首款AI芯片

一文了解CableLabs的領域與行業影響力

行業資訊 I 一文了解通用小芯片互聯技術 (UCIe) 標準

行業資訊 I 一文了解通用小芯片互聯技術 (UCIe) 標準

評論