現(xiàn)代計(jì)算機(jī)系統(tǒng)的許多接口都采用了 DDR 技術(shù),其中之一涉及到處理器與內(nèi)存的工作方式,人工智能(AI)、機(jī)器學(xué)習(xí)(ML)和數(shù)據(jù)挖掘等新應(yīng)用也在不斷推動這種接口突破新的極限。針對高帶寬同步動態(tài)隨機(jī)存取存儲器(SDRAM)的最新 DDR5 版本 DDR 接口的開發(fā)始于 2017 年,而備受期待的 JESD79-5 DDR5 SDRAM 標(biāo)準(zhǔn)于 2020 年 7 月發(fā)布。

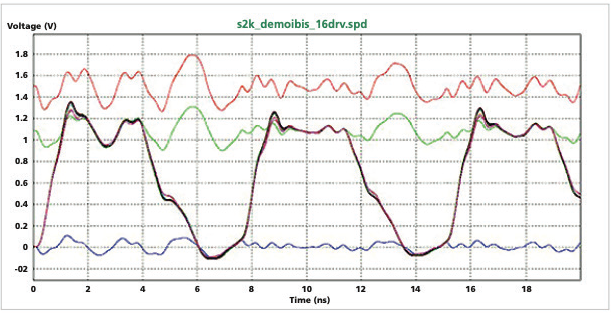

“兼顧電源影響”指的是一種先進(jìn)的信號完整性仿真方法,可以同時分析信號和電源噪聲(圖 1)。

圖1:兼顧電源影響的信號完整性仿真結(jié)果

兼顧電源影響的信號完整性解決方案必須考慮反射、串?dāng)_、時序和其他效應(yīng),并配備相應(yīng)的仿真和規(guī)則檢查技術(shù)。這些效應(yīng)也表明,同步開關(guān)噪聲(SSN)只能代表信號和電源相互作用引起的一部分問題。SSN 關(guān)注于通過正確的返回電流路徑同時進(jìn)行多個信號切換的場景。

另一種需要考慮電源影響的情況是,由信號通過平面空腔耦合引起的平面噪聲注入到另一信號,該信號與平行總線連接到同一電源,但不屬于 SSN 分析所關(guān)注的多開關(guān)網(wǎng)絡(luò)。噪聲也可能來自 PCB 上的電壓調(diào)節(jié)器。因此,SSN 仿真只是兼顧電源影響的解決方案的一部分。

最好在規(guī)則檢查和布線后分析階段實(shí)施兼顧電源影響的解決方案,因?yàn)槠矫婧托盘柕南嗷プ饔?耦合發(fā)生在布線完成之后。因此,一個完整的兼顧電源影響的解決方案需要提供:

一套針對信號衰減和電源對信號的影響的快速檢查方案

能夠模擬大型電路的時域仿真器(多個信號網(wǎng)絡(luò)和電源網(wǎng)絡(luò)的結(jié)果)

電源網(wǎng)絡(luò)和信號網(wǎng)絡(luò)的建模

高級輸入/輸出(I/O)緩沖器建模

借助 Cadence Sigrity X 進(jìn)行兼顧電源影響的信號完整性(SI)分析,并將其作為 DDR5 應(yīng)用設(shè)計(jì)和驗(yàn)證流程的一部分,工程師可以確信最終產(chǎn)品將與規(guī)格相符,并實(shí)現(xiàn)更好的性能。

Sigrity X 是 Cadence 最新一代信號和電源完整性(SI/PI)解決方案。搭載了全新的用于系統(tǒng)級分析的強(qiáng)大仿真引擎,并采用旗艦 Cadence Clarity 3D Solver 場求解器創(chuàng)新的大規(guī)模分布式架構(gòu)用于超大規(guī)模、5G 通信、汽車及航空航天應(yīng)用。

將系統(tǒng)分析性能提升 10 倍且無損精準(zhǔn)度

突破性的大規(guī)模分布式仿真實(shí)現(xiàn)云端大規(guī)模復(fù)雜分析

緊密集成、業(yè)界領(lǐng)先的 SI/PI 技術(shù)在 Cadence 全設(shè)計(jì)平臺可用

帶來新的用戶體驗(yàn),用戶可以在不同分析工作流程間復(fù)用,縮短復(fù)雜的系統(tǒng)分析設(shè)置時間

-

電源

+關(guān)注

關(guān)注

185文章

18313瀏覽量

255402 -

分析

+關(guān)注

關(guān)注

2文章

134瀏覽量

33599

發(fā)布評論請先 登錄

電源完整性分析及其應(yīng)用

聽懂什么是信號完整性

虎家白皮書系列 | Samtec Flyover?電纜系統(tǒng) 上篇

高速PCB信號完整性分析及應(yīng)用

超常材料應(yīng)用于電路板進(jìn)行電源完整性、信號完整性、電磁兼容性研究

高速PCB的信號完整性、電源完整性和電磁兼容性研究

信號完整性與電源完整性-信號的串?dāng)_

Introspect DDR5/LPDDR5總線協(xié)議分析儀

移遠(yuǎn)通信《5G RedCap技術(shù)發(fā)展及應(yīng)用白皮書》重磅發(fā)布

【白皮書】使用 Sigrity X 對 DDR5 應(yīng)用進(jìn)行兼顧電源影響的信號完整性分析

【白皮書】使用 Sigrity X 對 DDR5 應(yīng)用進(jìn)行兼顧電源影響的信號完整性分析

評論