BGA 封裝尺寸緊湊,引腳密度高。

在 BGA 封裝中,由于焊球排列和錯位而導致的信號串擾被稱為 BGA 串擾。

BGA 串擾取決于入侵者信號和受害者信號在球柵陣列中的位置。

在多門和引腳數量眾多的集成電路中,集成度呈指數級增長。得益于球柵陣列 (ball grid array ,即BGA) 封裝的發展,這些芯片變得更加可靠、穩健,使用起來也更加方便。BGA 封裝的尺寸和厚度都很小,引腳數則更多。然而,BGA 串擾嚴重影響了信號完整性,從而限制了 BGA 封裝的應用。下面我們來探討一下 BGA 封裝和 BGA 串擾的問題。

球柵陣列封裝

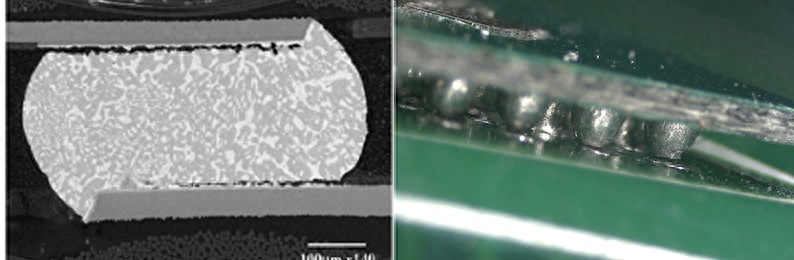

BGA 封裝是一種表面貼裝封裝,使用細小的金屬導體球來安裝集成電路。這些金屬球形成一個網格或矩陣圖案,排列在芯片表面之下,與印刷電路板連接。

使用 BGA 封裝的器件在芯片的外圍沒有引腳或引線。相反,球柵陣列被放置在芯片底部。這些球柵陣列被稱為焊球,充當 BGA 封裝的連接器。

微處理器、WiFi 芯片和 FPGA 經常使用 BGA 封裝。在 BGA 封裝的芯片中,焊球令電流在 PCB 和封裝之間流動。這些焊球以物理方式與電子器件的半導體基板連接。引線鍵合或倒裝芯片用于建立與基板和晶粒的電氣連接。導電的走線位于基板內,允許電信號從芯片和基板之間的接合處傳輸到基板和球柵陣列之間的接合處。

BGA 封裝以矩陣模式在芯片下分布連接引線。與扁平式和雙列式封裝相比,這種排列方式在 BGA 封裝中提供了更多的引線數。在有引線的封裝中,引腳被安排在邊界。BGA 封裝的每個引腳都帶有一個焊球,焊球位于芯片的下表面。這種位于下表面的排列方式提供了更多的面積,使得引腳數量增多,阻塞減少,引線短路也有所減少。與有引線的封裝相比,在 BGA 封裝中,焊球之間的排列距離最遠。

BGA 封裝的優點

BGA 封裝尺寸緊湊,引腳密度高。BGA 封裝電感量較低,允許使用較低的電壓。球柵陣列的排列間隔合理,使 BGA 芯片更容易與 PCB 對齊。

BGA 封裝的其他一些優點是:

由于封裝的熱阻低,散熱效果好。

BGA 封裝中的引線長度比有引線的封裝要短。引線數多加上尺寸較小,使 BGA 封裝的導電性更強,從而提高了性能。

與扁平式封裝和雙列式封裝相比,BGA 封裝在高速下的性能更高。

使用 BGA 封裝的器件時,PCB 的制造速度和產量都會提高。焊接過程變得更簡單、更方便,而且 BGA 封裝可以方便地進行返工。

BGA 串擾

BGA 封裝確實有一些缺點:焊球不能彎曲、由于封裝密度高而導致的檢查難度大,以及大批量生產需要使用昂貴的焊接設備。BGA 串擾是另一項限制,會影響通過 BGA 封裝傳輸的信號完整性。

BGA 封裝經常在大量 I/O 設備中使用。采用 BGA 封裝的集成芯片所傳輸和接收的信號,可能會受到從一個引線到另一個引線的信號能量耦合的干擾。由 BGA 封裝中的焊球排列和錯位而導致的信號串擾被稱為 BGA 串擾。球柵陣列之間的有限電感是 BGA 封裝中產生串擾效應的原因之一。當 BGA 封裝引線中出現高 I/O 電流瞬變(入侵信號)時,對應于信號引腳和返回引腳的球柵陣列之間的有限電感會在芯片基板上產生電壓干擾。這種電壓干擾導致了信號突變,并以噪音的形式從 BGA 封裝中傳輸出去,導致串擾效應。

在網絡系統等應用中,具有使用通孔的厚 PCB,如果沒有采取措施屏蔽過孔,那么 BGA 串擾會十分常見。在這樣的電路中,放置在 BGA 下面的長通孔會造成大量的耦合,并產生明顯的串擾干擾。

BGA 串擾取決于入侵者信號和受害者信號在球柵陣列中的位置。要減少 BGA 串擾,低串擾的 BGA 封裝排列至關重要。借助 Cadence Allegro Package Designer Plus 軟件,設計師能夠優化復雜的單裸片和多裸片引線鍵合(wirebond)以及倒裝芯片(flip-chip)設計;徑向、全角度推擠式布線可解決 BGA/LGA 基板設計的獨特布線挑戰;特定的 DRC/DFM/DFA 檢查,更可保障BGA/LGA設計一次成功;同時提供詳細的互連提取、3D 封裝建模以及兼顧電源影響的信號完整性和熱分析。

-

集成電路

+關注

關注

5420文章

11968瀏覽量

367330 -

BGA

+關注

關注

5文章

566瀏覽量

48176

發布評論請先 登錄

電子產品更穩定?捷多邦的高密度布線如何降低串擾影響?

技術資訊 | CMOS 噪聲容限值

技術資訊 I 哪些原因會導致 BGA 串擾?

技術資訊 I 哪些原因會導致 BGA 串擾?

評論