在描述高速運行的數字系統時,噪聲容限是最重要的參數之一。通常情況下,噪聲容限定義了 I/O 引腳上或接口中可接受的噪聲水平。在數字電子技術領域,噪聲容限是指 I/O 引腳上出現但不會導致接收邏輯狀態出錯的噪聲水平。這個值在時域中經常調用,用于測量比特誤碼率。

如果您正在設計高速 PCB 并需要執行串擾檢查,首先應明確評估成功的具體標準。從數字器件的 CMOS 噪聲容限值入手是個不錯的選擇,因為這些器件很可能是采用 CMOS 工藝制造的。

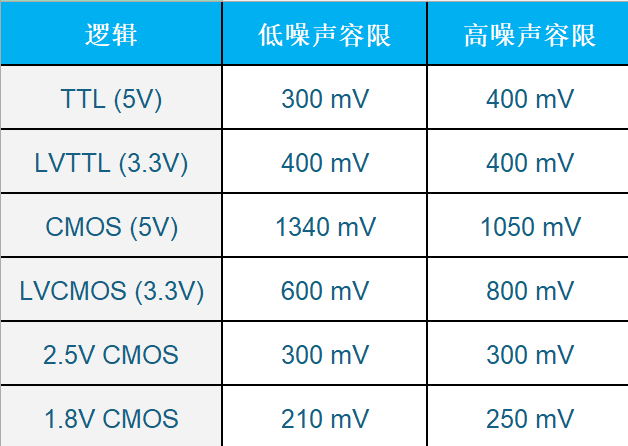

邏輯系列的噪聲容限值

電子產品中使用的所有邏輯系列都具有用于定義二進制邏輯狀態的高閾值和低閾值。在每種狀態下,信號電平都有一個可接受的電壓范圍,這決定了接口上的噪聲容限,而噪聲容限是邏輯系列的函數。對于采用 CMOS 工藝制造的較新器件,噪聲容限也是電源電壓的函數,并隨著核心電壓值的降低逐漸下降。

下表總結了不同邏輯系列的部分噪聲容限值。由于高電平和低電平狀態下的噪聲容限值不同,通常取兩者中的較小值作為器件 I/O 引腳上可接受的噪聲電平。

核心電壓已降至 1.8V 以下(例如 1.2V、1.0V 和 0.8V),這些器件的噪聲容限也隨著核心電壓的降低而下降。大多數采用 CMOS 工藝制造的常見數字 ASIC 和微控制器都在 LVCMOS 核心電壓水平下運行。

噪聲容限的應用

在 PCB 設計中,噪聲容限主要用于分析以下三個特定 SI 問題:

地彈

串擾

電源軌噪聲

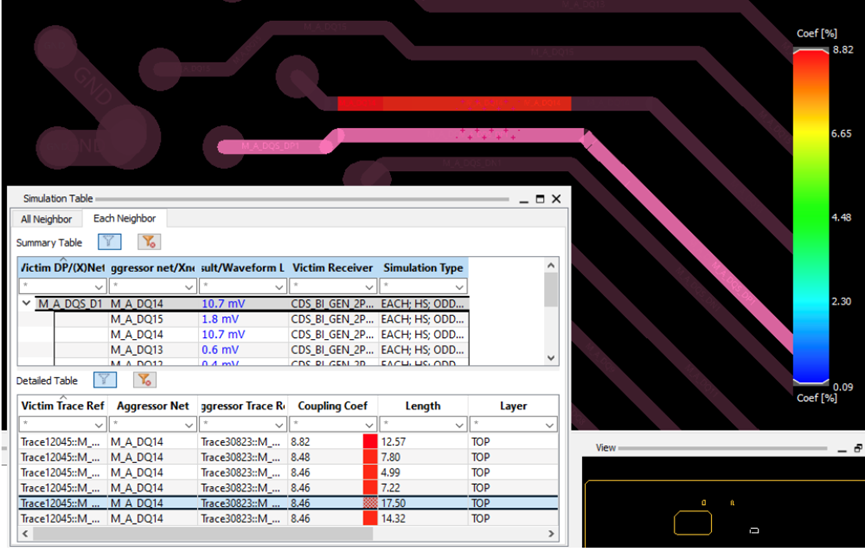

地彈和串擾可以在時域中分析,并與所允許的噪聲容限進行比較。例如,在簡單的串擾仿真中,可以將計算得出的串擾脈沖幅度與噪聲容限進行比較,以快速評估串擾是否超出可接受范圍。

例如,下圖中的串擾仿真示例顯示串擾比率(受害者峰值電壓與攻擊者峰值電壓)為 8.46%。當攻擊者的峰值信號水平為 1.8V 時,峰值串擾為 152 mV,略低于此示例接口的噪聲容限。

對于地彈問題,通常使用示波器進行測量。當 I/O 引腳暴露在 PCB 上時,使用帶寬足夠高的示波器探頭便可直接測量地彈。

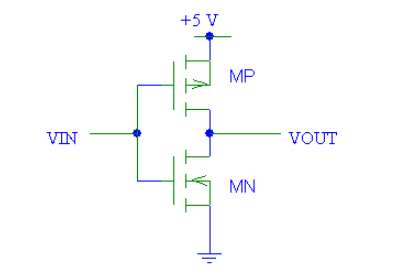

上述問題中的最后一項(即電源軌噪聲的 I/O 噪聲)較難理解,因為電源軌噪聲并不會以 1:1 的比例傳輸至 I/O 輸出。這是由 CMOS 緩沖電路的性質所決定的,其中涉及半導體裸片上的諸多晶體管和無源元件。正因如此,業界開發了兼顧電源影響的 SI 仿真工具,以更精確地分析電源軌噪聲對 SI 的影響。目前,I/O 上的噪聲必須作為注入電源軌噪聲的函數進行測量。這種測量方法較為復雜,無法直接適用于所有 PCB 堆疊。

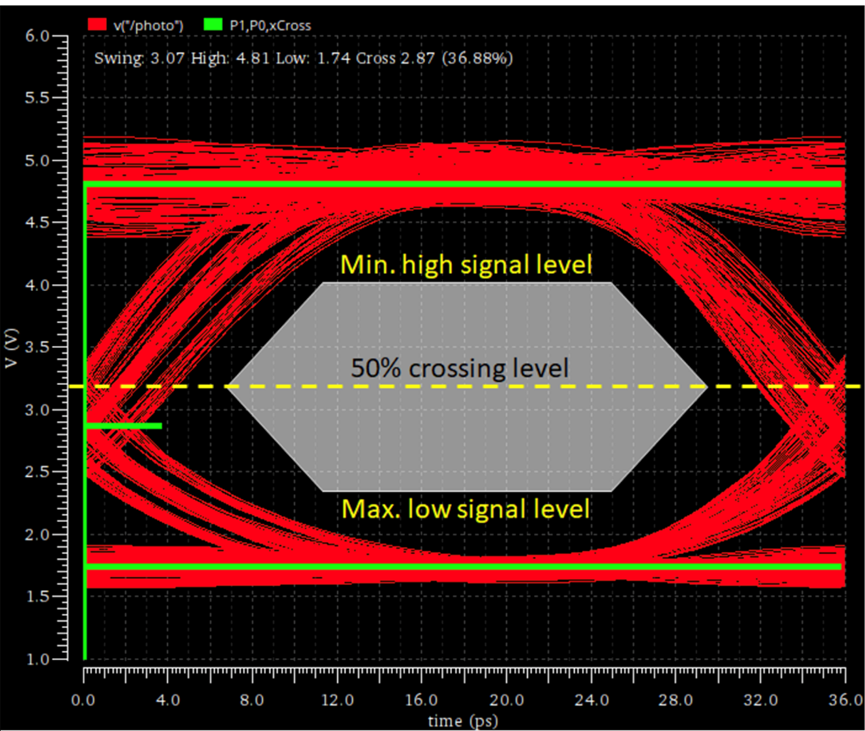

低于 1.8V 的高速接口

在高速接口中,眼圖通常用于評估信號完整性,因為它是在接收器件的 I/O 引腳上測量的。即使在信號電壓高達 1.8V 的接口中,噪聲容限也不會直接用于評估,而是包含在眼圖的另一項評估指標中,即眼圖模板或眼開度。眼圖模板對信號電平的上升時間和噪聲設定了限制,如下圖所示。

高級信號完整性仿真器允許用戶指定眼圖模板,以便根據仿真數據計算比特誤碼率。這些仿真器可以直接處理 PCB 布局數據,并確定串擾、ISI 和抖動的合理準確估計值。雖然噪聲容限是這些仿真的一項輸入參數,但無需手動檢查眼圖中的每條軌跡,即可判斷通道的合規性。

如需加快 CMOS 接口噪聲容限的分析速度,可以使用 Cadence 的系統分析工具組合評估高速數字系統。新一代 Sigrity X 可以與 Clarity 3D Solver 配合工作,并與 Allegro X PCB Designer 和 Allegro X Advanced Package Designer 工具緊密集成。這一全新特性可以幫助 PCB 和 IC 封裝設計師將端到端、multi-fabric 和多電路板系統(從發射端到接收端或從電源到耗電端)相結合,確保 SI/PI 成功簽核。

-

電子產品

+關注

關注

6文章

1209瀏覽量

59176 -

CMOS

+關注

關注

58文章

5996瀏覽量

238201 -

pcb

+關注

關注

4356文章

23438瀏覽量

407159

發布評論請先 登錄

TTL電平和CMOS電平標準

CY8C21334的噪聲容限不匹配

LTC4313的典型應用具有高噪聲容限的2線總線緩沖器

抖頻要要有效降低開關電源EMI噪聲容限的技術

噪音容限,噪音容限是什么意思

cmos電平與rs485_rs485通信與DP的區別

FS153是一款低功耗,高速,高噪聲容限,EPROM/ROM基于8位CMOS工藝制造的單片機

技術資訊 | CMOS 噪聲容限值

技術資訊 | CMOS 噪聲容限值

評論