硬件仿真器被稱之為EDA工具皇冠上的明珠,其地位十分重要。近日,國內(nèi)EDA廠商芯華章正式發(fā)布硬件仿真系統(tǒng)樺敏HuaEmu E1,是國內(nèi)首臺(tái)可滿足150億門以上芯片應(yīng)用系統(tǒng)的驗(yàn)證容量的產(chǎn)品。至此,芯華章搭建完整的全流程數(shù)字前端驗(yàn)證EDA工具平臺(tái)。

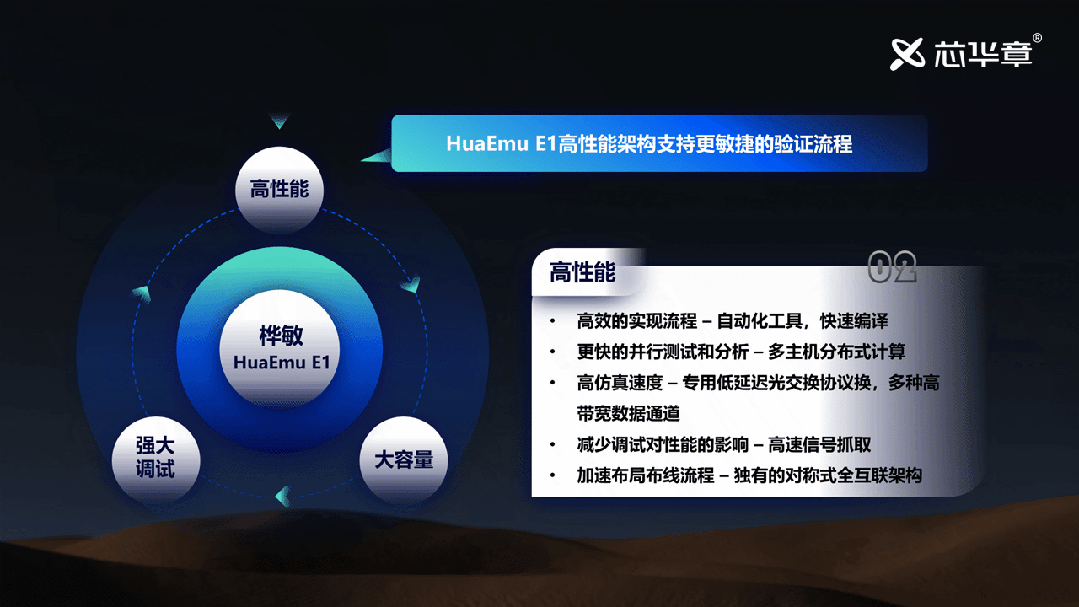

HuaEmu E1三大核心優(yōu)勢(shì)

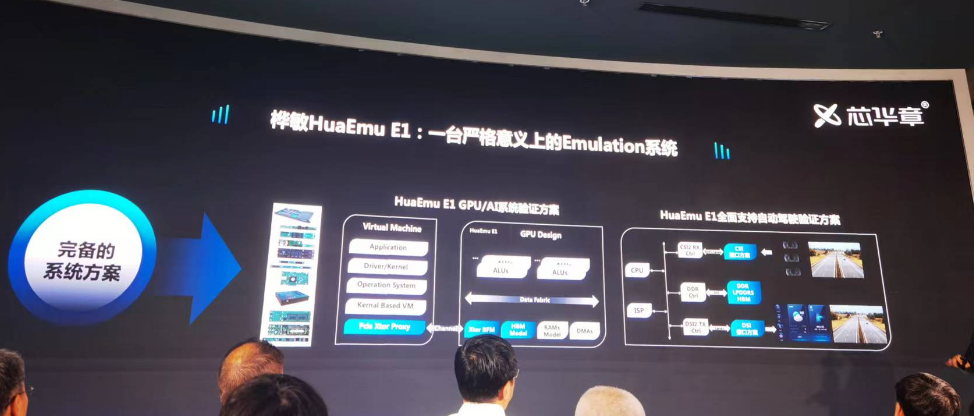

樺敏HuaEmu E1基于自主研發(fā),實(shí)現(xiàn)多項(xiàng)國內(nèi)驗(yàn)證技術(shù)突破,具備大規(guī)模可擴(kuò)展驗(yàn)證容量、自動(dòng)化實(shí)現(xiàn)工具、全流程智能編譯、高速運(yùn)行性能以及強(qiáng)大的調(diào)試能力,從而極大助力軟硬件協(xié)同開發(fā),提升系統(tǒng)級(jí)創(chuàng)新效率,賦能高性能計(jì)算、GPU、人工智能、智能駕駛、無線通信等各種應(yīng)用領(lǐng)域的開發(fā)。在發(fā)布會(huì)上,芯華章研發(fā)副總裁顏體儼博士對(duì)樺敏HuaEmu E1的特性做了詳細(xì)解讀。

大容量

樺敏HuaEmu E1支持超過150億門級(jí)的容量,支持目前世界上最高階、最復(fù)雜的芯片。既能夠?qū)我恍酒?yàn)證,又能夠進(jìn)行幾個(gè)芯片的系統(tǒng)級(jí)驗(yàn)證。另外,在驗(yàn)證芯片時(shí),客戶可以利用E1的容量將周邊的環(huán)境直接在E1中實(shí)現(xiàn),譬如可以用E1來提供足夠的存儲(chǔ)容量。

驗(yàn)證同一個(gè)芯片時(shí),一個(gè)芯片設(shè)計(jì)團(tuán)隊(duì)會(huì)有很多位的芯片驗(yàn)證工程師,需要同時(shí)執(zhí)行許多的芯片測(cè)試,或者驗(yàn)證芯片中不同的模塊。E1可以同時(shí)支持最高128個(gè)用戶使用不同的資源,資源的顆粒度可以以2,000萬門為單位。基于relocation的能力,不同的使用者可以快速的切換,不需要重新編譯,直接移轉(zhuǎn),這種高效率的使用,也可以支持以后芯華章EDA 2.0云原生的系統(tǒng)。

高性能

以Emulation的執(zhí)行速度來看,如果一個(gè)客戶只用到8000門的容量,E1最高的執(zhí)行速度可以達(dá)到10兆赫。如果客戶用從8,000萬門到3.2億門,E1最高可以跑到5兆赫,如果超過3.2億門,E1最高可以跑到一兆赫。

E1內(nèi)部有快速低延遲的連接,從前端到后端有非常高效的編譯流程,E1中對(duì)稱的互聯(lián)結(jié)構(gòu),也使得后端的partition能夠更快速的完成。

調(diào)試能力

芯片驗(yàn)證過程最花時(shí)間的通常是定位問題并解決之,那么強(qiáng)大的調(diào)試能力對(duì)硬件仿真顯得非常重要。

E1能夠讓使用者讀取或看到波形,同時(shí)可以看到RTL SystemVerilog的里面所有的訊號(hào),它可以取出無限深度的波形,還具有精準(zhǔn)的觸發(fā)功能。

E1能夠支持各種驗(yàn)證的方法。E1連接到物理上的真實(shí)場(chǎng)景,比如一個(gè)GPU用在電玩上時(shí),可以把E1直接連到遙感,另一邊連到高清電視。當(dāng)芯片的RTL完成之后,即使還沒有做綜合布局布線,就可以馬上開始玩游戲。

又以虛擬主機(jī)混合仿真為例,驗(yàn)證手機(jī)上的APP或者PC的 devicedriver能否與芯片共同工作,需要依賴虛擬主機(jī)的功能,它可以模擬各種操作系統(tǒng),測(cè)試軟件在不同操作系統(tǒng)下如何跟芯片共同工作。當(dāng)芯片驗(yàn)證的過程中,可以把一些資料寫在存儲(chǔ)上,當(dāng)驗(yàn)證完以后,把這個(gè)資料與標(biāo)準(zhǔn)的預(yù)設(shè)數(shù)據(jù)相比較。既可以讀取任何信號(hào),也可以調(diào)配數(shù)值和驗(yàn)證環(huán)境,模擬各種狀況。此外,如果物理模型不方便建構(gòu),同時(shí)有C++模型所制造的虛擬仿真環(huán)境,E1能夠提供高速與主機(jī)互聯(lián)的通道來進(jìn)行驗(yàn)證。

對(duì)于有波形產(chǎn)生的功能,顏體儼談到波形產(chǎn)生要滿足幾個(gè)條件,第一個(gè)全信號(hào)可見,第二個(gè)要有足夠的深度、足夠長的波形時(shí)間。第三個(gè)要高效運(yùn)行,不把執(zhí)行速度減低太多。第四個(gè)要減低資源的消耗。E1有很多功能,經(jīng)過靈活的搭配使用,可以滿足以上各種的要求,并且隨著觸發(fā)的功能共同使用,可以在運(yùn)行之間隨時(shí)換擋,先高速運(yùn)行到某一種條件之下,再慢下來捕捉更多的波形信號(hào),接著再全速前進(jìn)。

E1還能夠提供遠(yuǎn)程控制功能,E1的風(fēng)扇散熱可以根據(jù)溫度的高低自動(dòng)調(diào)節(jié)轉(zhuǎn)速,自動(dòng)監(jiān)測(cè)電壓溫度等等環(huán)境。

進(jìn)一步來說,樺敏HuaEmu E1由研發(fā)團(tuán)隊(duì)從頭設(shè)計(jì),與芯華章其他的驗(yàn)證產(chǎn)品比如GalaxSim、GalaxFV、FusionDebug使用相容的數(shù)據(jù)庫,產(chǎn)生的波形使用統(tǒng)一的標(biāo)準(zhǔn),通過FusionDebug可以觀看波形,并分析E1跑出來的結(jié)果。

芯華章首席技術(shù)官傅勇認(rèn)為:“HuaEmu E1的發(fā)布,標(biāo)志芯華章徹底搭建了完整的全流程數(shù)字驗(yàn)證平臺(tái),能夠支持超大容量芯片設(shè)計(jì)完成系統(tǒng)級(jí)驗(yàn)證,并有能力進(jìn)行深度調(diào)試。基于芯華章智V驗(yàn)證平臺(tái)提供的統(tǒng)一底層框架、統(tǒng)一覆蓋率數(shù)據(jù)庫和調(diào)試系統(tǒng),我們圍繞HuaEmu E1的大容量、高性能與強(qiáng)大調(diào)試能力,針對(duì)系統(tǒng)應(yīng)用創(chuàng)新,如智能網(wǎng)聯(lián)汽車、高性能計(jì)算中心、大算力芯片和系統(tǒng)的軟硬件開發(fā)等,打造了豐富、高效的定制化系統(tǒng)級(jí)敏捷驗(yàn)證技術(shù)解決方案,可以幫助用戶大大提高驗(yàn)證效率,降低研發(fā)成本的同時(shí),極大提高產(chǎn)品的創(chuàng)新效率。”

目前,HuaEmu E1已交付多家國內(nèi)頭部芯片設(shè)計(jì)和系統(tǒng)級(jí)用戶使用,獲得實(shí)際項(xiàng)目部署。

不斷完善驗(yàn)證產(chǎn)品線,助力國產(chǎn)EDA發(fā)展

芯華章資深產(chǎn)品和業(yè)務(wù)規(guī)劃總監(jiān)楊曄表示,E1產(chǎn)品的發(fā)布意味著芯華章已經(jīng)正式進(jìn)入硬件仿真器市場(chǎng),硬件仿真器要做成芯華章一個(gè)拳頭產(chǎn)品,能獲得用戶的認(rèn)可,并繼續(xù)擴(kuò)張產(chǎn)品方案,逐步地去對(duì)標(biāo)產(chǎn)品線更加完整的國際大廠。

面對(duì)當(dāng)前全球半導(dǎo)體的發(fā)展形勢(shì),芯華章首席市場(chǎng)戰(zhàn)略官謝仲輝表示,盡管全球半導(dǎo)體發(fā)展受到多重因素的影響,但哪怕是Synopsys、Cadence等公司在過去多年芯片產(chǎn)業(yè)的起起伏伏中,仍然保持著比較好的業(yè)績。畢竟越是低迷不景氣的時(shí)候,越需要?jiǎng)?chuàng)造新的產(chǎn)品刺激增長。算力芯片就是當(dāng)前關(guān)注度最高的領(lǐng)域之一。

楊曄補(bǔ)充道,以GPU來看,英偉達(dá)主流GPU已經(jīng)達(dá)到100多億門的規(guī)模,就必須要有高性能的硬件仿真器。并且主機(jī)與GPU放在一個(gè)系統(tǒng)里去仿真就需要驗(yàn)證方案的支持。這不僅是一臺(tái)硬件,而是仿真客戶的整個(gè)系統(tǒng)。因此,算力芯片的設(shè)計(jì)更加需要硬件仿真器的助力。

EDA技術(shù)發(fā)展也在與時(shí)俱進(jìn),芯華章提出EDA2.0時(shí)代降低EDA工具使用門檻,讓芯片設(shè)計(jì)更普惠。對(duì)此,謝仲輝談到,芯華章研究院正在做一些課題,例如將人工智能導(dǎo)入形式驗(yàn)證,用大語言模型或直接用母語轉(zhuǎn)成systemverilog 語言驅(qū)動(dòng)EDA工具,又或者利用AI以數(shù)據(jù)而不只是看波形來進(jìn)行調(diào)試,還有EDA支持原生云以此靈活提供新的業(yè)務(wù)模式等等。

據(jù)了解,芯華章主要布局在數(shù)字前端驗(yàn)證,目前也有部分的工具已經(jīng)涉及到后端,逐漸拓展產(chǎn)品線,形成更強(qiáng)的系統(tǒng)能力。對(duì)于國產(chǎn)EDA企業(yè)間的合作也秉持開放態(tài)度,謝仲輝表示芯華章主要做數(shù)字驗(yàn)證,團(tuán)隊(duì)規(guī)模在500多人,華大九天也有六七百人的規(guī)模,國內(nèi)EDA企業(yè)在各自領(lǐng)域做專做深,再以接口開放標(biāo)準(zhǔn)做融合,流程打通,能發(fā)揮國產(chǎn)EDA企業(yè)的合力。關(guān)于國產(chǎn)FPGA的合作,謝仲輝也表示大容量高性能FPGA有助EDA硬件性能更優(yōu),最終賦能編譯器和軟件。我們也非常關(guān)心國產(chǎn)FPGA的進(jìn)度,積極推動(dòng)合作。

-

eda

+關(guān)注

關(guān)注

71文章

2904瀏覽量

176752 -

硬件仿真器

+關(guān)注

關(guān)注

0文章

7瀏覽量

8852 -

芯華章

+關(guān)注

關(guān)注

0文章

180瀏覽量

11585

發(fā)布評(píng)論請(qǐng)先 登錄

無懼EDA封鎖升級(jí),思爾芯國產(chǎn)方案筑牢客戶驗(yàn)證防線

芯華章攜手EDA國創(chuàng)中心推出數(shù)字芯片驗(yàn)證大模型ChatDV

芯華章以AI+EDA重塑芯片驗(yàn)證效率

國內(nèi)EDA大廠芯華章換將,聚焦發(fā)展,戰(zhàn)略升級(jí)

芯華章謝仲輝:國產(chǎn)EDA以市場(chǎng)為導(dǎo)向,以客戶價(jià)值為重

芯華章持續(xù)助力EDA精英挑戰(zhàn)賽

艾偉達(dá)發(fā)布數(shù)字芯片EDA工具adsDesigner

芯華章發(fā)布FPGA驗(yàn)證系統(tǒng)新品HuaProP3

芯華章推出新一代高性能FPGA原型驗(yàn)證系統(tǒng)

國產(chǎn)EDA公司芯華章科技推出新一代高性能FPGA原型驗(yàn)證系統(tǒng)

華中科技大學(xué)集成電路學(xué)院一行走訪EDA廠商芯華章

行芯、EDA2與華為云攜手共創(chuàng)EDA評(píng)測(cè)新篇章

芯華章致力于打造完整的數(shù)字驗(yàn)證全流程工具

芯華章生態(tài)戰(zhàn)略亮相DAC,發(fā)布全流程敏捷驗(yàn)證管理器FusionFlex,并聯(lián)合華大九天推出數(shù)模混合仿真解決方案

芯華章推出EDA全流程敏捷驗(yàn)證管理器昭睿FusionFlex

補(bǔ)齊重要版圖,國產(chǎn)EDA廠商實(shí)現(xiàn)全流程數(shù)字芯片前端驗(yàn)證!芯華章發(fā)布硬件仿真器,EDA2.0戰(zhàn)略更進(jìn)一步

補(bǔ)齊重要版圖,國產(chǎn)EDA廠商實(shí)現(xiàn)全流程數(shù)字芯片前端驗(yàn)證!芯華章發(fā)布硬件仿真器,EDA2.0戰(zhàn)略更進(jìn)一步

評(píng)論