GPIO的八種工作模式

GPIO是通用輸入/輸出端口的簡稱,GPIO的引腳與外部設備連接,可實現與外部通訊、控制外部硬件或者采集外部硬件數據的功能。GPIO的8種輸入模式:包括4種輸入模式和4種輸出模式(2種普通輸出和2種復用輸出)。

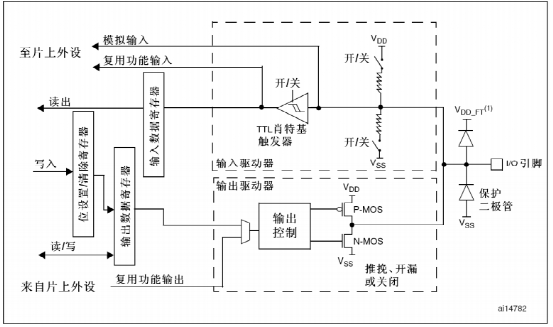

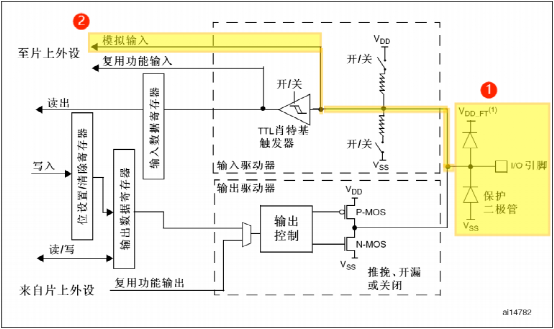

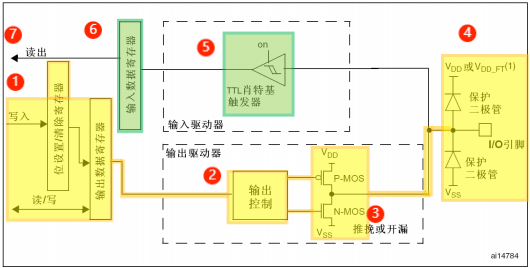

GPIO基本結構

每個GPIO內部都有這樣的一個電路結構,下面就簡單的介紹一下這個電路

保護二極管:I/O引腳上的二極管是為了防止引腳外部輸入過高、過低的電壓時對芯片造成損壞而設置的,起到保護電路的作用。當引腳電壓>VDD時,上方的二極管導通;當引腳電壓

P-MOS管和N-MOS管:GPIO所具有的“推挽輸出”輸出和“開漏輸出”模式得益于由P-MOS管和N-MOS管組成的單元電路。

TTL肖特觸發器:可以理解為用肖特管構成的施密特觸發器,模擬信號經過觸發器后,就會轉化為0和1的數字信號。如果GPIO引腳作為輸入通道進行ADC電壓采集時,用其“模擬輸入”功能,信號就不會經過觸發器進行TTL轉換。

VDD_FT 對5V容忍I/O腳是特殊的,它與VDD不同。這句話的意思就是VDD_FT是兼容5V和3.3V的,而沒有FT的是不兼容5V的。

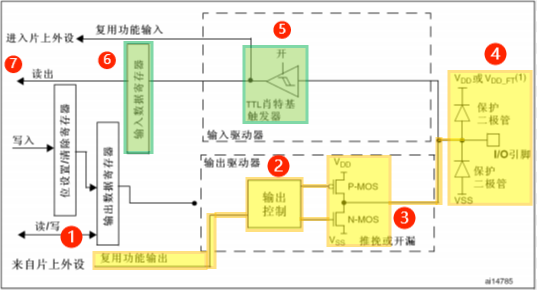

下面具體介紹GPIO的8種工作模式:

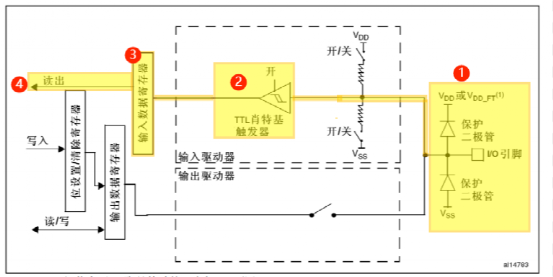

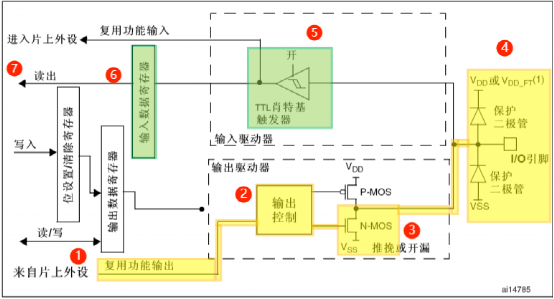

輸入模式—浮空輸入

在此模式下,上圖黃色陰影部分①—④的電路為通路,由①I/0端口輸入電平(高電平或低電平)→保護二極管→②TTL肖特基觸發器→③輸入數據寄存器→④CPU,這樣CPU就能讀取到I/O端口處的高低電平狀態。浮空輸入模式下,I/O端口的電平信號直接進入輸入數據寄存器。也就是說,I/O的電平狀態是不確定的,完全由外部輸入決定;如果在該引腳懸空(無信號輸入)的情況下,讀取該端口的電平是不確定的。它的輸入阻抗較大,一般把這種模式用于標準的通信協議如I2C、USART。

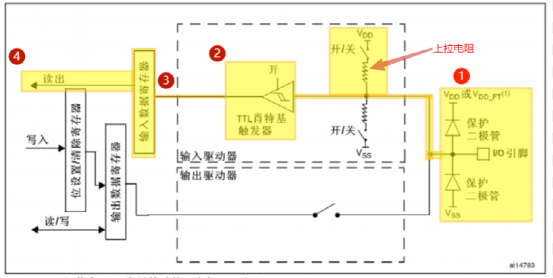

輸入模式—輸入上拉

上拉電阻:把不確定的信號通過電阻連接到高電平,默認情況下輸入引腳數據為1,高電平。在上拉輸入模式下,也是I/O端口的電平信號直接進入輸入數據寄存器,但是它和浮空模式的主要區別在于,輸入上拉模式中上拉電阻(連接VDD)的開關閉合,上拉電阻的大小約為30—50kΩ。

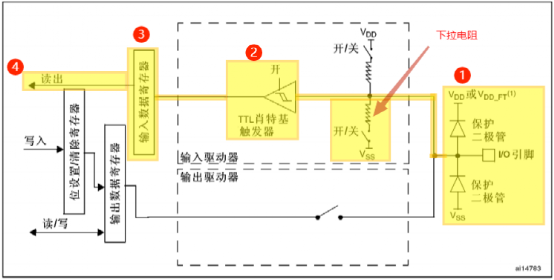

輸入模式—輸入下拉

下拉電阻:把不確定的信號通過電阻連接到低電平,默認情況下輸入引腳數據為0,低電平。在下拉輸入模式下,也是I/O端口的電平信號直接進入輸入數據寄存器,同理,它和浮空模式的主要區別在于,輸入下拉模式中下拉電阻(連接VSS)的開關閉合。

輸入模式—模擬輸入

在此模式下,數據通道中上拉、下拉電阻和TTL肖特觸發器,這時均處于關斷的狀態,在模擬輸入狀態下,CPU是無法通過“輸入數據寄存器”讀到IO端口變化的數據了,也就是說“輸入數據寄存器”就無法反映I/O端口上的電平變化的了。I/O端口的模擬信號(注意是電壓信號,而非電平信號)直接模擬輸入到片上外設模塊,比如ADC模塊。

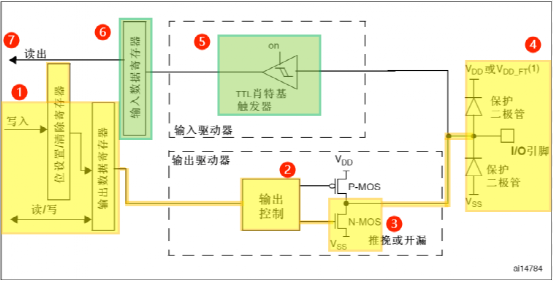

輸出模式—開漏輸出

①

若②輸出控制電路接收到1(高電平),則③N-MOS管截止,那么此時 ④I/O端口處的電平不是通過②輸出控制電路和③N-MOS管來控制的,而是取決于外部的“上拉”或“下拉”。

若②輸出控制電路接收到 0(低電平),③N-MOS管導通,此時④I/O端口處的電平就被③N-MOS管拉低。

同時,在輸出的狀態下,I/O口的電平還可以通入輸入電路(④I/O端口→⑥輸入數據寄存器→⑦CPU讀取)來讀取。

輸出模式—開漏復用輸出

開漏復用輸出模式與開漏輸出模式很相似,區別在于輸出的高低電平的來源,不是讓CPU直接向位設置/清除寄存器寫1/0然后將其映射到輸出數據寄存器中,而是利用片上外設模塊的復用功能輸出來決定的。

輸出模式—推挽輸出

由圖可知,GPIO的推挽輸出模式是在開漏輸出模式的基礎上,在“輸出控制電路”之后,增加了一個P-MOS管。

當CPU輸出邏輯“1 ”時,③P-MOS管導通,N-MOS管截止,輸出高電平。

當CPU輸出邏輯“0 ”時,③P-MOS管截止,N-MOS管導通,輸出低電平。

同時,I/O端口的電平也可以通過輸入電路(④I/O端口→⑥輸入數據寄存器→⑦CPU讀取)進行讀取。

輸出模式—推挽復用輸出

推挽復用輸出模式與推挽輸出模式相似。只是輸出的高低電平的來源,不是讓CPU直接向位設置/清除寄存器寫1/0然后將其映射到輸出數據寄存器中,而是利用片上外設模塊的復用功能輸出來決定的。

-

二極管

+關注

關注

148文章

10098瀏覽量

171551 -

引腳

+關注

關注

16文章

1719瀏覽量

52850 -

觸發器

+關注

關注

14文章

2039瀏覽量

62130 -

GPIO

+關注

關注

16文章

1280瀏覽量

54045 -

VDD

+關注

關注

1文章

316瀏覽量

35154

發布評論請先 登錄

單片機中常見GPIO的八種工作模式詳解

【轉載】STM32GPIO八種工作模式區別

ARM嵌入式裸機--GPIO的八種工作模式

ST MCU_GPIO有哪幾種工作模式

ST MCU_GPIO的八種工作模式詳解。

GPIO的八種工作模式

STM32 GPIO的八種工作模式

GPIO的八種工作模式

GPIO的八種工作模式

評論