來源:轉載自21ic論壇極海半導體專區

01 前言

一般我們開發MCU自帶的SRAM,對一般應用來說,已經夠用了,但是對于內存需求較高的場合,比如跑GUI或者算法等,自帶的內存會就不夠用,這個時候就要外擴SRAM或SDRAM。

不過還好找到了APM32E103VET6S,這款芯片合封了2MB的SDRAM,就是集成在芯片內部的意思,據我閱讀數據手冊了解,合封的SDRAM只是跟MCU封裝在一起,初始化程序寫法跟外擴SDRAM是一樣的。在程序中使用SDRAM的時候我們都需要填入起始地址,很不方便,這時候就需要內存管理來幫助我們自動分配內存,大大減少開發時間和出現bug的可能。

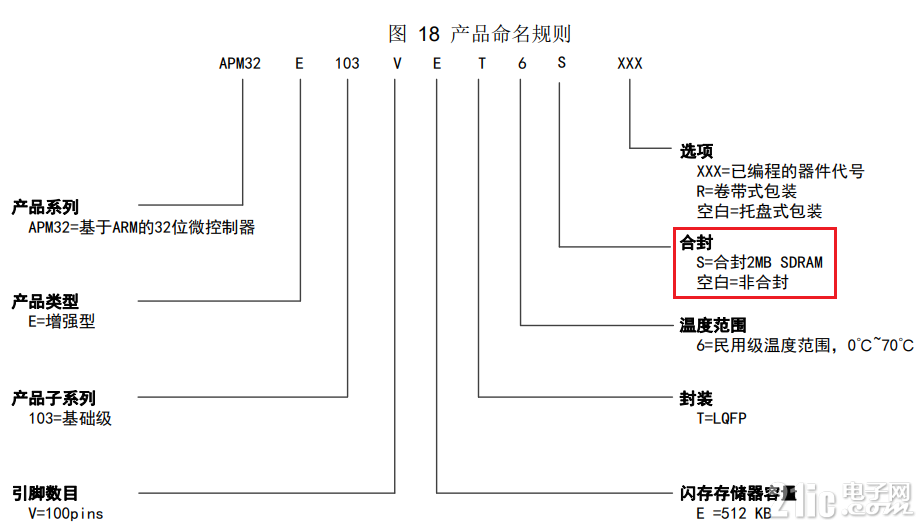

圖1-1產品命名規范

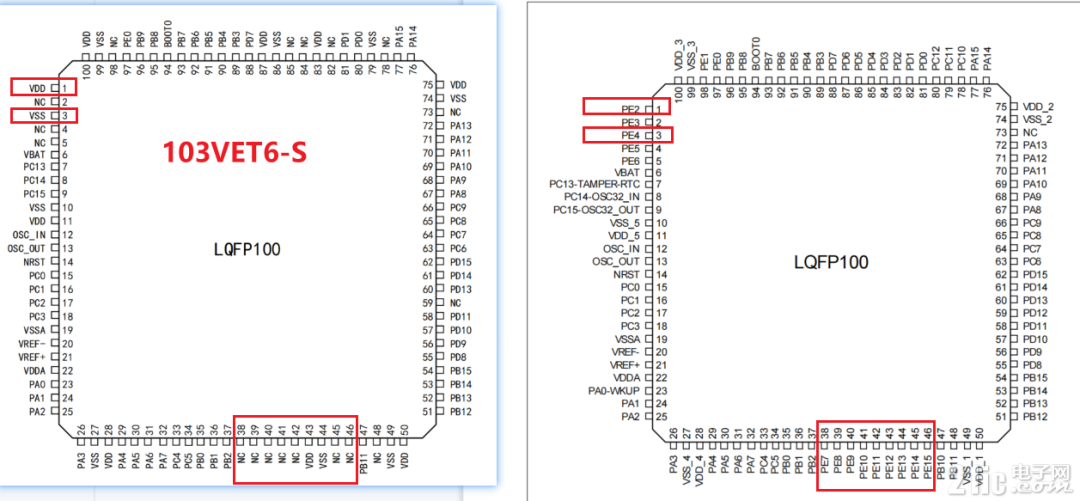

根據圖1-1可以看出APM32后綴帶S就是合封了2MB的SDRAM,不帶后綴S是沒有的,那么再來對比下這2者的區別,如圖1-2所示,合封了SDRAM的會把SDRAM所使用到的引腳隱藏起來了,但是官方沒有把PB11隱藏起來,與SDRAM存在沖突,如有使用建議更換其他IO口。

圖1-2 合封與非合封的區別

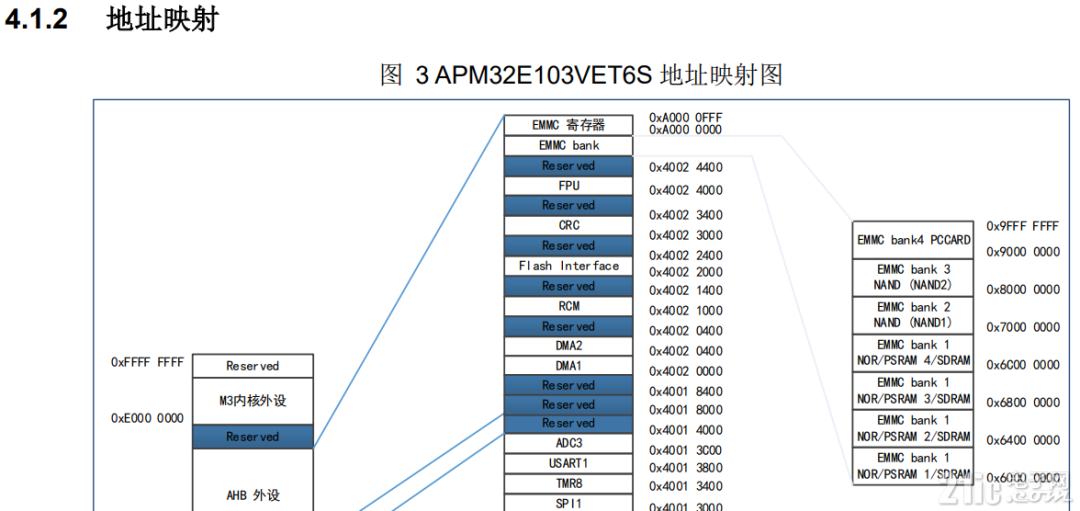

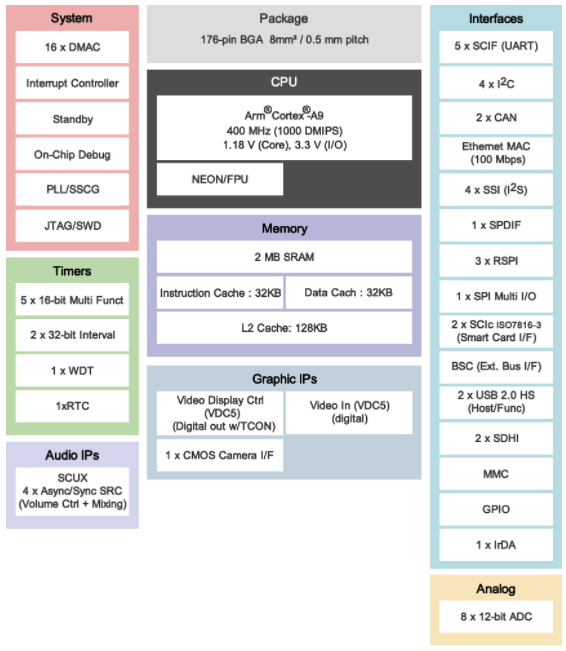

接下來看官方芯片數據手冊如圖1-3,Flash:512KB,SRAM:128KB,SDRAM:2MB

圖1-3存儲器

圖1-4地址映射圖

從地址映射可以看到SDRAM的地址從60000000H開始,記住這個地址,待會程序里用到。

02 準備材料

接下來用到2個程序,正點原子戰艦內存管理例子和APM32E1的SDK的DMC_SDRAM例子,我們在DMC_SDRAM程序的基礎上移植正點原子戰艦內存管理例子:

1、【正點原子】戰艦STM32F103開發板資料 資料盤(A盤)4,程序源碼實驗37 內存管理實驗

2、APM32E10x_SDK_V1.2ExamplesEMMCDMC_SDRAM

03 移植說明

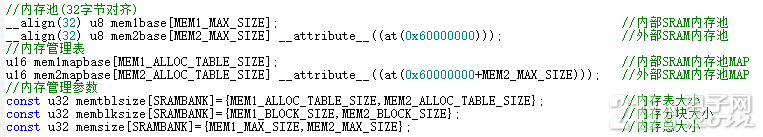

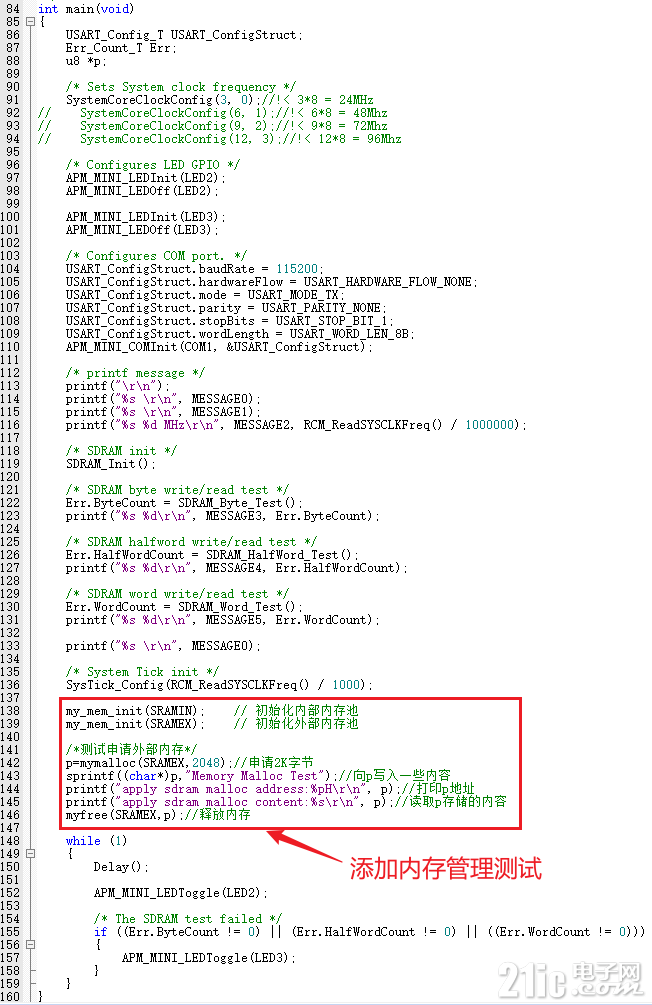

1、首先復制正點原子戰艦內存管理例子里的malloc.c和malloc.h到DMC_SDRAM工程下,修改malloc.c中的外部內存地址為0x60000000

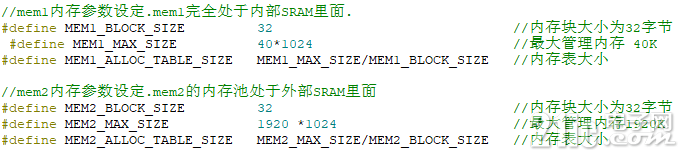

2、修改malloc.h,我這里SDRAM用1920K,留了點沒用完

3、移植完成,下面測試下

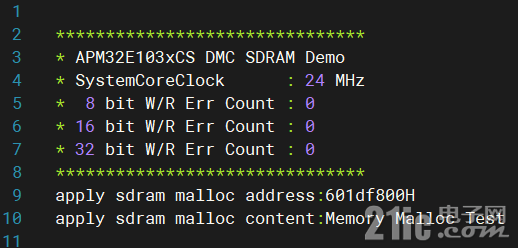

運行串口打印如下:

Err Count : 0證明SDRAM測試讀寫正常。然后再看打印的p地址不是0x20000000H,而是在60000000H到60200000H之間,就證明申請的內存用在SDRAM內。

好了,以后程序里就可以用mymalloc(SRAMEX,xxx)函數申請SDRAM自動分配的內存或者mymalloc(SRAMIN,xxx)申請內部SRAM自動分配的內存啦。

注:文章作者在原帖中提供了例程文件,有需要請至原文21ic論壇下載

原文地址:https://bbs.21ic.com/icview-3327108-1-1.html

-

芯片

+關注

關注

459文章

52481瀏覽量

440556 -

mcu

+關注

關注

146文章

17970瀏覽量

366531 -

sram

+關注

關注

6文章

785瀏覽量

115929 -

內存

+關注

關注

8文章

3122瀏覽量

75243

原文標題:APM32芯得 EP.60 | 自帶SRAM不夠用?一文教你如何在APM32E1上高效管理2MB SDRAM

文章出處:【微信號:geehysemi,微信公眾號:Geehy極海半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

ESP32-PICO-MINI-02確定內部flash為2MB,沒有外部ram嗎?

CC3200如何將flash從1MB改成2MB?

EMW3166內部2MB SPI閃存

為什么在sdkconfig中默認將ESP32閃存容量設置為2MB呢?

APM/ACPI電源管理

E1 2.048 Mb/s Interface Pod

DS13737 超低功耗Arm? Cortex?-M33 32位MCU+TrustZone?+FPU,240 DMIPS,2MB閃存,786 KB SRAM

DS13086 超低功率Arm? Cortex?-M33 32位MCU+TrustZone?+FPU, 240 DMIPS,高達2MB的閃存,786KB的SRAM,密碼器

DS12117_32 位 Arm? Cortex?-M7 480MHz MCU,2MB 閃存,1MB RAM,46 com. 和模擬接口,加密

DS12110_32 位 Arm? Cortex?-M7 480MHz MCU,最高 2MB 閃存,最高 1MB RAM,46 com. 和模擬接口

帶2MB片內RAM的RTOS微處理器RZ/A1LC數據手冊

如何在APM32E1上高效管理2MB SDRAM

如何在APM32E1上高效管理2MB SDRAM

評論