引言

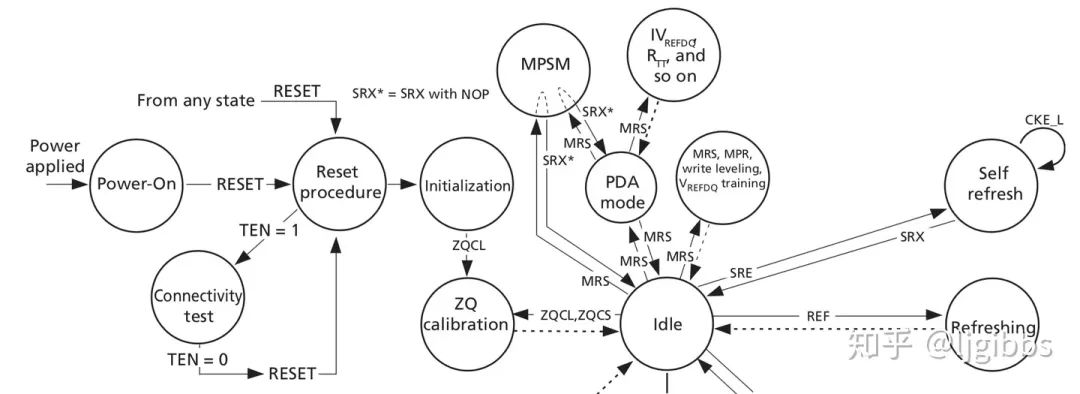

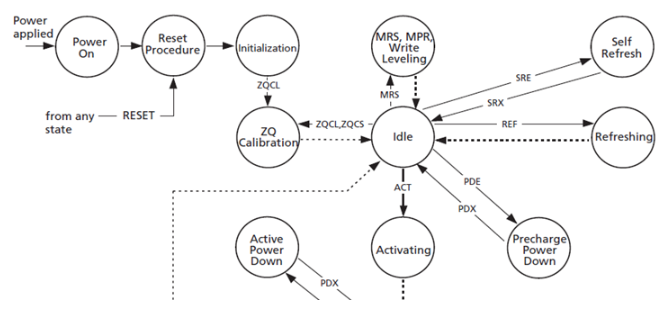

當一個擁有 DRAM 子系統(tǒng)的設備啟動時,有幾件事需要在 DRAM 進入工作狀態(tài)之前完成。下圖是來自JEDEC specification(DDR4 標準,jedec.org/standards-doc)的狀態(tài)機,展示出上電之后 DRAM 經(jīng)歷的幾個狀態(tài)。

圖-1 DDR4 初始化狀態(tài)機

實質(zhì)上,完整的初始化過程(Initialization)包括以下 4 個單獨的步驟:

上電與初始化 ,Power-up and Initialization

ZQ 校準,ZQ Calibration

Verf DQ 校準,Verf DQ Calibration

讀寫訓練,即存儲介質(zhì)訓練/初始校準,Read/Write Training

譯注:至此標題中的 Initialization,calibration,training 已經(jīng)全部出現(xiàn),接下來的文章中將嘗試讓讀者明白這三個詞的含義,以及這三個階段中具體做了哪些事情。

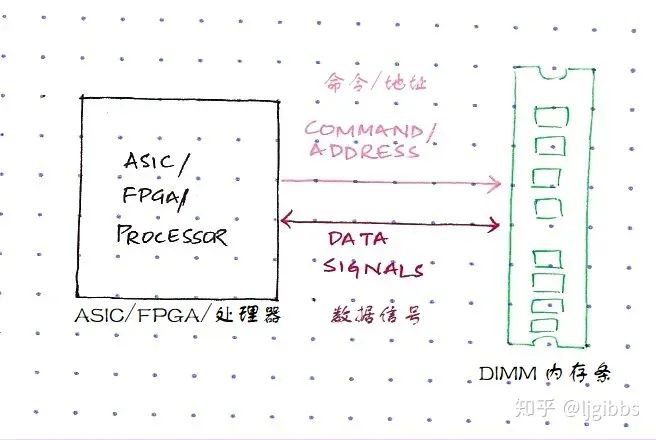

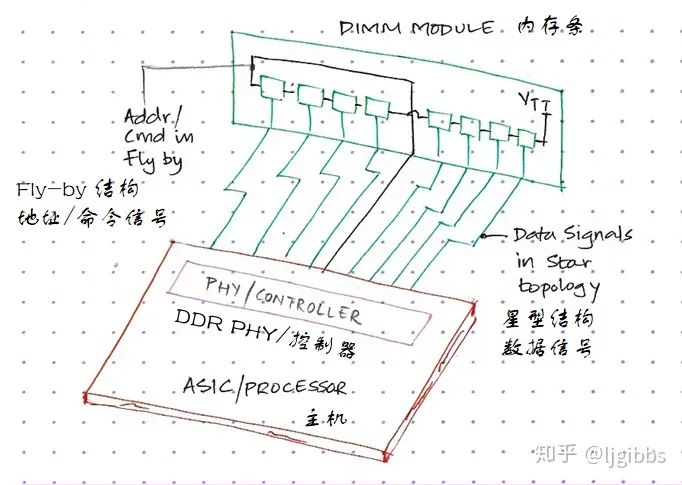

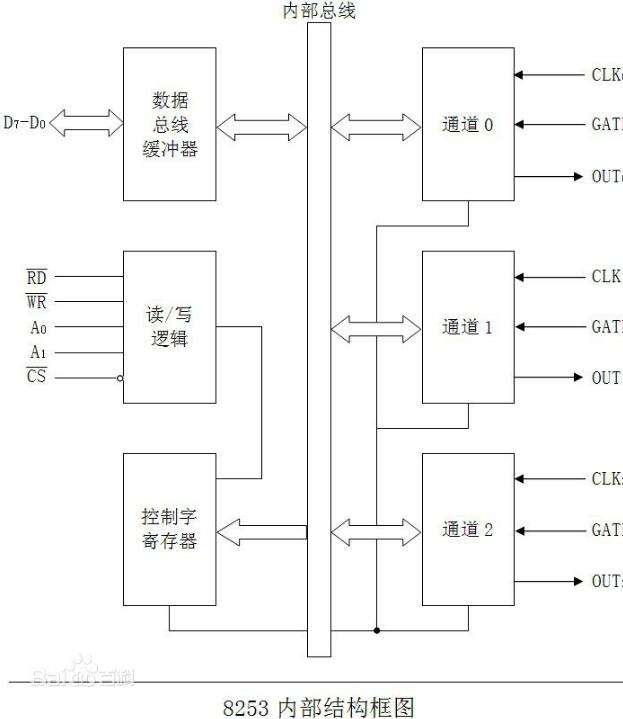

為了能夠更好地理解接下來的幾節(jié)內(nèi)容,這里我們假設有一個如下圖中的系統(tǒng):具有單個 DIMM 器件(即只有單個內(nèi)存條)的 ASIC/FPGA/處理器(譯注:以下稱為主機)。

圖-2 示例系統(tǒng)

初始化 Initialization

圖-3 初始化相關的狀態(tài)

上電與初始化是由一系列精心設計的步驟組成的序列(sequence)。一般來說,在系統(tǒng)上電之后,ASIC/FPGA/處理器中的 DDR 控制器會被從復位狀態(tài)中釋放,自動執(zhí)行上電與初始化序列。下文中列舉了一個超簡化的控制器所做的工作,而在 JESD79-49A 的 3.3 節(jié)中有更詳細并準確的描述。

給 DRAM 顆粒上電

置低 DRAM 的復位端口 RESET,并使能 DRAM 的時鐘使能 CKE

使能并產(chǎn)生時鐘 CK_t/CK_c

向 DRAM 發(fā)出 MRS 命令,并按照特定的序列讀取/配置 DRAM 的 Mode Register

進行 ZQ 校準(ZQCL)

使 DRAM 進入狀態(tài)機中的 IDLE 狀態(tài),為后續(xù)讀寫做好準備

在上述一系列流程結(jié)束后,DIMM 內(nèi)存條上的 DRAM 顆粒已經(jīng)了解了其需要工作在哪個頻率上,以及它的時序參數(shù)是多少,包括 CAS Latency,CAS Write Latency 等等。(譯注:那么讀者們,DRAM 是具體通過哪一個步驟了解這些信息的呢?)

ZQ 校準 ZQ Calibration

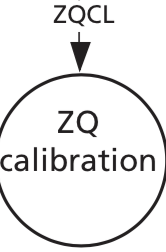

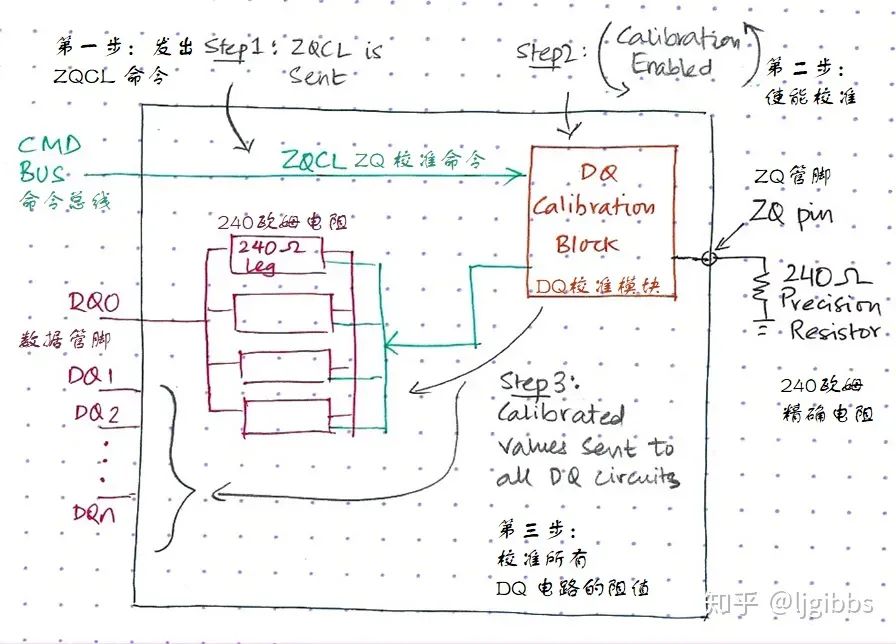

圖-4 ZQCL

ZQ 校準的概念與 DDR 數(shù)據(jù)信號線 DQ 的電路有關。當討論 ZQ 校準做了什么以及為何而做之前,我們首先需要來看下每個 DQ 管腳之后的電路。請注意,DQ 管腳都是雙向的(bidirectional),負責在寫操作時接收數(shù)據(jù),在讀操作時發(fā)送數(shù)據(jù)。

圖-5 DQ 校準模塊

如圖 5 所示,如果你從 DRAM 內(nèi)部的視角來看,每個 DQ 管腳之后的電路都有多個并聯(lián)的 240 歐姆電阻組成。(譯注:具體地說不上來,但這些電阻用于提高信號完整性)由于顆粒制造時, CMOS 工藝本身的限制,這些電阻不可能是精確的 240 歐姆。此外,阻值還會隨著溫度和電壓的改變而改變。所以必須校準至接近 240 歐姆,用于提高信號完整性。

為了能夠?qū)@些電阻阻值進行精確校準,每個 DRAM 顆粒具有:

專用的 DQ 校準模塊

一個 ZQ 管腳連接至外部電阻,該電阻阻值為精確的 240 歐姆

這個外部電阻因為其精確而且不會隨溫度變化而變化的阻值,被用于參考阻值。在初始化過程中,ZQCL 命令發(fā)出后,DQ 校準模塊對每個 DQ 管腳連接的電阻進行校準。

上文是對 ZQ 校準一個大概的講解:

DQ 管腳連接的電阻用于提高信號完整性 ->需要精確的阻值 ->由于制造工藝以及溫度變化的限制,這個阻值并不精確 ->引入 ZQ 管腳連接的外部電阻和 DQ 校準模塊,在初始化階段對 DQ 電阻值進行校準 ->提高信號完整性,以支持更高的數(shù)據(jù)速率。

如果你滿意了,可以直接忽略本節(jié)剩余的內(nèi)容,如果沒有,本節(jié)剩余的內(nèi)容將討論更多的細節(jié),請繼續(xù):

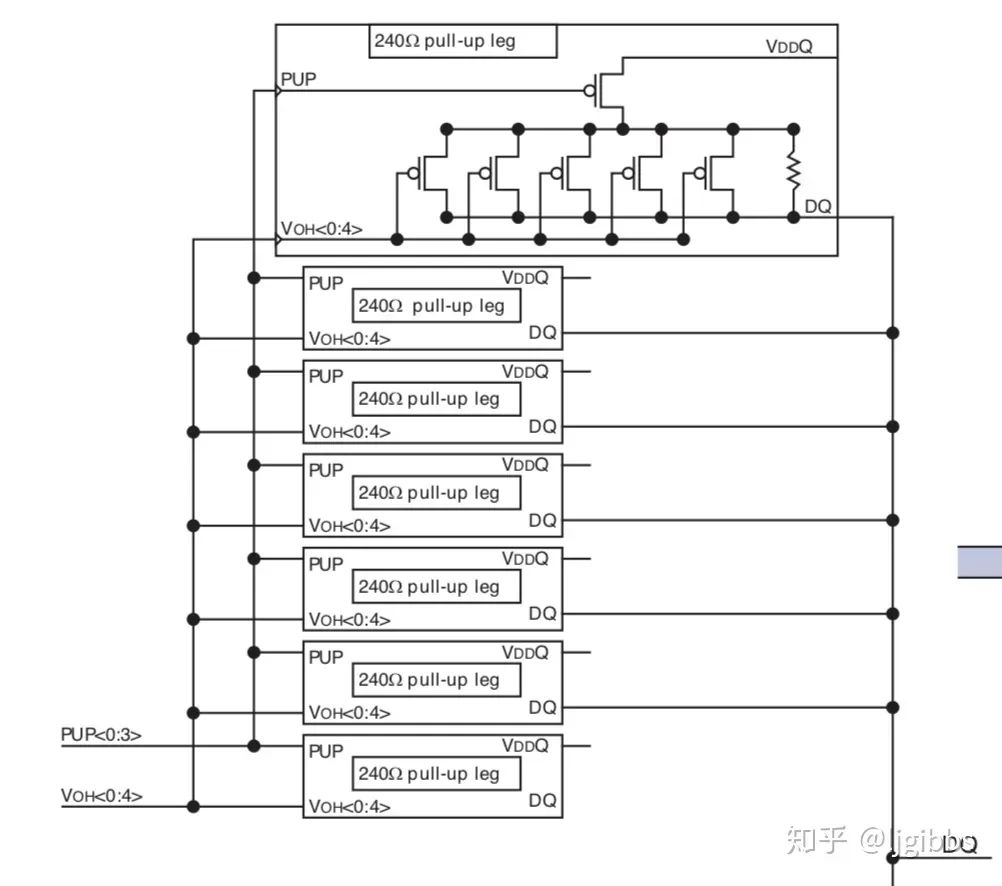

DQ 電路中的240歐姆電阻是Poly Silicon Resistor 類型的,通常來說,它們的阻值會略大于 240 歐姆。因此,在 DQ 電阻上并聯(lián)了很多 PMOS 管,當這些管子開啟時,通過并聯(lián)電阻降低 DQ 電阻的阻值,以接近 240 歐姆。

下圖中放大了某個電阻的內(nèi)部結(jié)構(gòu),有 5 個 PMOS 管與 DQ 電阻并聯(lián),通過 VOU[0:4] 控制管子的開關,以控制并聯(lián)上來的電阻數(shù)量。

圖-6 DQ driver/receiver 電路,來自 Micron datasheet

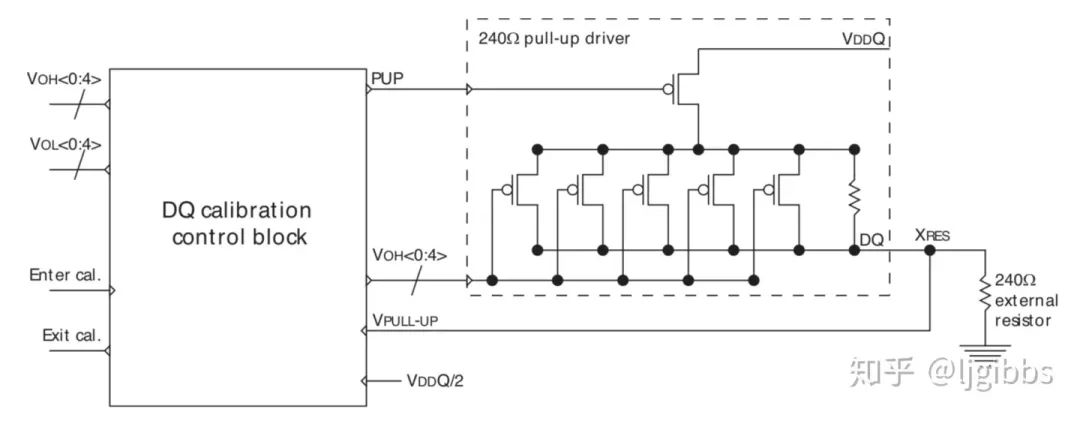

連接至 DQ 校準控制模塊的電路包括一個由兩個電阻組成的分壓電路,其中一個是上面提到的可調(diào)阻值的 poly 電阻,而另一個則是精準的 240 歐姆電阻。

當 ZQCL 命令發(fā)出后,DQ 校準控制模塊使能,并通過其內(nèi)部邏輯控制 VOH[0:4] 信號調(diào)整 poly 電阻阻值,直到分壓電路的電壓達到 VDDQ/2,即兩者均為 240 歐姆。此時 ZQ 校準結(jié)束,并保存此時的 VOH 值,復制到每個 DQ 管腳的電路。

圖-7 DQ 校準模塊,來自 Micron datasheet

那么問題來了,為什么不在每個 DRAM 出廠時就將阻值調(diào)整至 240 歐姆呢?而是在每次使用之前(初始化)調(diào)整呢?

這是因為并聯(lián)的電阻網(wǎng)絡允許用戶在不同的使用條件下對電阻進行調(diào)整,為讀操作調(diào)整驅(qū)動強度,為寫操作調(diào)整端接電阻值。此外,不同 PCB 具有不同的阻抗,可調(diào)整的電阻網(wǎng)絡可針對每個 PCB 單獨調(diào)整阻值,以提高信號完整性,最大化信號眼圖,允許 DRAM 工作在更高的頻率下。

信號驅(qū)動強度可以通過 mode register MR1[2:1] 控制。端接電阻可以通過 MR1/2/5 中的 RTT_NOM, RTT_WR & RTT_PARK 進行調(diào)節(jié)。

DQ 判決電平校準 Verf DQ Calibraton

圖-8 VrefDQ Calibration

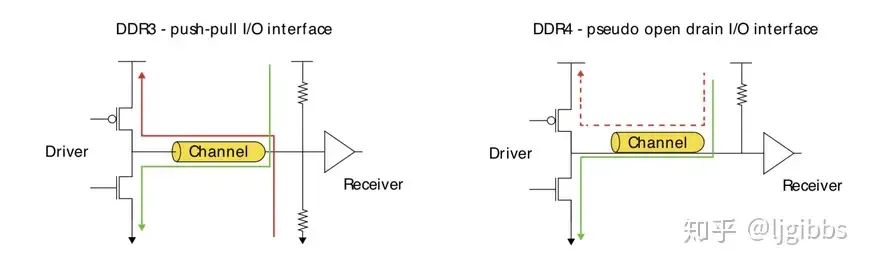

DDR4 數(shù)據(jù)線的端接方式(Termination Style)從 CCT(Center Tapped Termination,也稱 SSTL,Series-Stud Terminated Logic)更改為 POD(Pseudo Open Drain)。這是為了提高高速下的信號完整性,并節(jié)約 IO 功耗。這不是 POD 的首次應用,GDDR5 同樣使用 POD。

圖-9 DDR3(SSTL)v.s. DDR4(POD),來自 Micron datasheet

根據(jù)上圖可以發(fā)現(xiàn),在 DDR3 中接收方使用 Vdd/2 作為判決電平,判斷信號為 0 或者為 1,上圖中 DDR3 的接收實際上是一個分壓電路。

但是在 DDR4 中,接收方不再有分壓電路,取而代之的是一個內(nèi)部參考判決電平,判斷信號為 0 或者為 1。這個判決電平稱為 VerfDQ。VerfDQ 可以通過模式寄存器 MR6 進行設定,在 VrefDQ 階段,控制器需要通過嘗試不同的 VerfDQ 值,來設置一個能夠正確區(qū)分高低電平的值。

讀寫訓練 Read/Write Training

在完成上述步驟后,DRAM 初始化已經(jīng)完成,并處于 IDLE 狀態(tài),但此時存儲介質(zhì)仍然未處于正確的工作狀態(tài)。在正確讀寫 DRAM 之前,DDR 控制器或者物理層還必須來做一些重要的步驟,稱為讀寫訓練,也稱存儲介質(zhì)訓練/初始校準。

運行算法,以對齊 DRAM 的時鐘信號 CK 與數(shù)據(jù)有效信號 DQS 的邊沿

運行算法,確定 DRAM 顆粒的讀寫延遲

將采樣時刻移動至讀取數(shù)據(jù)眼圖的中央

報告錯誤,如果此時的信號完整性實在太差,沒辦法確保可靠的讀寫操作

為什么需要讀寫訓練

讓我們一起仔細地觀察我們的參考系統(tǒng),下圖顯示數(shù)據(jù)與地址/控制信號,在內(nèi)存條與主機(ASIC/Processor)之間是如何連接的。

數(shù)據(jù)(DQ)以及數(shù)據(jù)有效(DQS)信號連接至內(nèi)存條的相應位置,因為內(nèi)存條與主機上相應端口是一一對應的,因此采用星型拓撲。

時鐘、命令&地址信號(CK,CKE,A,WE,CSn)連接至 DIMM 內(nèi)存條時,采用一種稱為 fly-by 的拓撲結(jié)構(gòu),如下圖黑線所示。DIMM 上的多個顆粒(比如下圖中有 8 個)都共享同一組地址/控制信號,采用 fly-by 結(jié)構(gòu)能夠提高信號完整性與信號速度。

圖-10 詳細的參考系統(tǒng)示例

這樣一來,我們從主機的角度來看,與 DIMM 上不同的顆粒的距離是不同的。而從 DIMM 的角度來看,時鐘(黑色)與數(shù)據(jù)(綠色)之間的相對延遲對于不同顆粒是不同的。訓練的目的即消除這兩個不同對數(shù)據(jù)讀寫的影響。

DRAM 本身是個很“呆” 的器件,很多事情都需要 DDR 控制器來完成,為什么這么說呢。

如果你要進行寫操作,在初始化期間你需要通過將CAS Write Latency寫入 DRAM 模式寄存器,(CWL 是寫入列地址與數(shù)據(jù)之間的延遲時間長度),此后 DRAM 將始終使用該時序參數(shù),不會變化。DDR 控制器需要負責根據(jù)板級的布線延遲以及 fly-by 結(jié)構(gòu)的路由延遲,調(diào)整數(shù)據(jù)與地址信號之間的延遲,以保證地址和數(shù)據(jù)信號到達每個 DRAM 的相對延遲滿足 CWL。

舉例而言,如果設置 CWL 為 9,一旦主機在發(fā)出列地址后,由于地址到達各 DRAM 的時間不同,因此需要以不同的延遲,在各數(shù)據(jù)線上發(fā)送寫數(shù)據(jù),以保證寫數(shù)據(jù)到達 DRAM 的延遲均為 9。

讀操作也需要 DDR 控制器來做類似的工作。考慮到每個 DRAM 顆粒位于 DIMM 的不同位置,距離主機的距離不同。因此每個 DRAM 顆粒接收到讀命令的時間不同,因此后續(xù)回應的讀數(shù)據(jù)到達主機的時間也不相同。初始化期間,主機確定各個 DRAM 顆粒的延遲,并以此訓練內(nèi)部的電路,使電路能夠在正確的時刻采樣來自 DRAM 的讀數(shù)據(jù)。

對于讀寫訓練,控制器/PHY 一般提供多種算法。最常見的算法包括:

Write leveling

MPR Pattern Write

Read Centering

Write Centering

以上算法一般由控制器/PHY(譯注:以下統(tǒng)一表示為控制器) 完成,用戶只需要在寄存器中使能/失能相關算法,并根據(jù)其結(jié)果進行相應操作。接下來的幾節(jié)將進一步探討控制器是如何具體實現(xiàn)這些算法的。

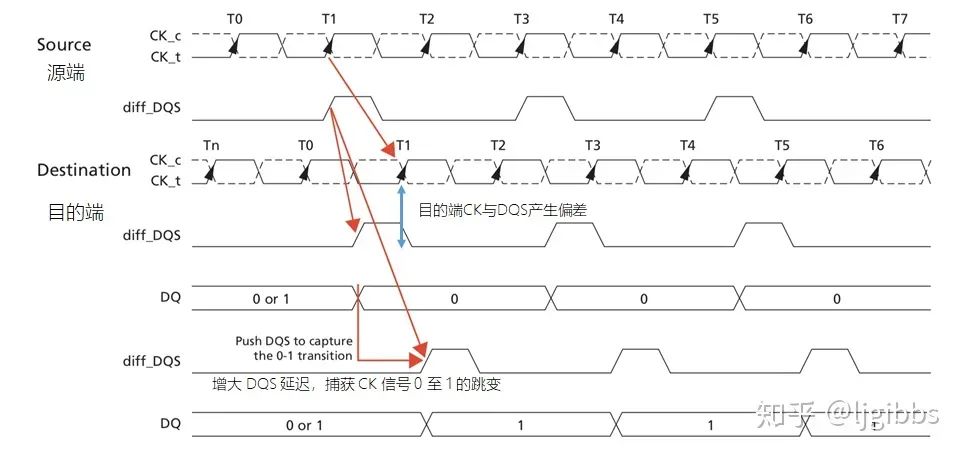

Write Leveling

DRAM 寫入中最重要的,不能違反的時序參數(shù)是tDQSS,表示數(shù)據(jù)有效信號 DQS 相對時鐘信號 CK 的相對位置。tDQSS 必須在協(xié)議規(guī)定的 tDQSS(MIN) 和 tDQSS(MAX) 之間。如果 tDQSS 超出規(guī)定的限制,那么可能會寫入錯誤的數(shù)據(jù)。

既然內(nèi)存條上每個 DRAM 顆粒的數(shù)據(jù)有效信號相對于時鐘的延遲都不同,所以控制器必須對每個 DRAM 顆粒的 tDQSS 進行訓練,并根據(jù)訓練的結(jié)果滿足每個顆粒不同的延遲需求。

啟用 Write Leveling 時,控制器會做以下幾項工作:

下圖展示了 Write Leveling 的概念。

圖-11 Write Leveling 示意圖

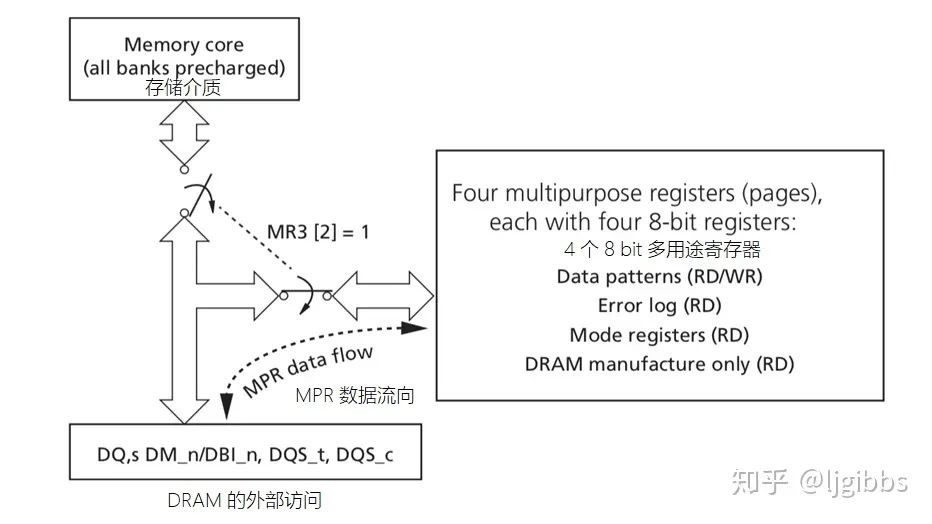

MPR Pattern Write

MPR(Multi Purpose Register,多用途寄存器)Pattern Write 實際上并不是一種校準算法,通常是讀寫對齊(Read/Write Centering)之前的一個預備步驟。

DDR4 DRAM 包括四個 8 比特可編程寄存器,稱為 MPR,用于 DQ 比特訓練(比如 Read/Write Centering)。通過向模式寄存器 MR3[2] 寫 1,進入 MPR 訪問模式,在該模式下所以向 DRAM 進行的讀寫操作都會同 MPR 進行,而不是真正的存儲介質(zhì)。

Read Centering

Read Centering 的目的是訓練控制器的讀采樣電路,在讀數(shù)據(jù)眼圖的中央進行采樣,以獲得最穩(wěn)定的采樣結(jié)果。DDR 控制器

Write Centering

與 Read Centering 類似,Write Centering 的目的是設定每條數(shù)據(jù)信號線上寫數(shù)據(jù)的發(fā)送延遲,使 DRAM 端能夠根據(jù)對齊數(shù)據(jù)眼圖的中央的 DQS 采樣數(shù)據(jù)信號 DQ。

在 Write Centering 的過程中,控制器不斷執(zhí)行 寫-讀-延遲變化-比較 (Write-Read-Shift-Compare)的流程

通過上述流程,控制器判斷出正常讀寫數(shù)據(jù)時能容忍的最大發(fā)送延遲。因此可以推斷出寫數(shù)據(jù)的左右有效邊界,并在 DRAM 端將寫數(shù)據(jù)的中央與 DQS 邊沿對齊。

周期性校準 Periodic Calibration

交換機或者路由器等網(wǎng)絡設備,運行過程中的溫度和電壓可能發(fā)生變化。為了確保信號完整性,以及讀寫的穩(wěn)定性,一些在初始化階段進行訓練的參數(shù)必須重新訓練更新。控制器 IP 通常會提供下列兩項周期性校準流程。

周期性校準是一項可選的功能,因為如果你可以確定你的設備只會工作在穩(wěn)定的溫度環(huán)境下,那么初始化時進行的 ZQ 校準以及讀寫訓練就已經(jīng)足夠了

一般來說控制器可以通過設定一個計時器,來進行周期性校準,在計時器計滿中斷發(fā)生后進行周期性校準。

總結(jié)

在 DRAM 投入使用之前,有 4 個步驟的工作需要完成

在這些步驟完成后,系統(tǒng)正式進入 IDLE 狀態(tài),并為后續(xù)的讀寫操作做好準備。根據(jù)設備的運行環(huán)境,你可能需要使能定期校準。

原文網(wǎng)址:左下角閱讀原文。

將模式寄存器 MR1 的比特 7 設為 1,使 DRAM 進入 Write Leveling 模式。在該模式中,DRAM 在數(shù)據(jù)有效 DQS 信號上升沿采樣時鐘信號 CK,并將采樣值通過數(shù)據(jù)信號 DQ 返回給控制器

控制器發(fā)送一系列 DQS 信號,在 Write Leveling 模式中,DRAM 根據(jù) DQS 信號采樣 CK 信號,返回采樣值 1 或者 0

控制器接下來

1.觀察 DRAM 返回的 CK 采樣值

2.根據(jù)采樣值增加或者減少 DQS 信號的延遲

3.繼續(xù)發(fā)送更新延遲的 DQS 信號,繼續(xù)觀察 CK 采樣值

DRAM 在 DQS 信號有效時,采樣 CK 信號并返回

重復步驟 2 至 4,直到控制器檢測到返回值從 0 變化到 1。此時,DQS 與 CK 上升沿對齊,控制器鎖定當前的 DQS 延遲,當前 DRAM 的 Write Leveling 完成

重復步驟 2 至 5,直到 DIMM 的所有 DRAM 顆粒都完成 Write Leveling

通過向模式寄存器 MR1 的比特 7 寫 0,退出 Write Leveling 模式

使能模式寄存器 MR3 中的 bit 2,進入 MPR 訪問模式,從 MPR 而不是 DRAM 存儲介質(zhì)中讀取數(shù)據(jù)

發(fā)起一系列讀請求,此時返回的是在 MPR Pattern Write 步驟中預先寫入 MPR 的 pattern。假設 pattern 是交替變化的 1-0-1-0-...

在讀數(shù)據(jù)進行過程中,增加或者減少采樣電路相對于時鐘的采樣延遲,來確定讀數(shù)據(jù)眼圖的左右邊界。(譯注:即保證讀取數(shù)據(jù)正確,與 pattern 一致時,最小以及最大采樣延遲)

在確定眼圖的左右邊界后,將讀延遲寄存器設置為眼圖的中央

對每一條數(shù)據(jù)信號 DQ 重復上述操作

發(fā)出一系列的寫,讀請求

增加寫數(shù)據(jù)時的發(fā)送延遲

將讀取的數(shù)據(jù)與發(fā)送數(shù)據(jù)進行比較

周期性 ZQ 校準, 也被稱為 ZQCS (ZQ Calibration Short),用于定期校準 240 歐姆電阻

周期性 Read Centering,重新計算讀取延遲以及其他相關的參數(shù)

上電與初始化 ,Power-up and Initialization

ZQ 校準,ZQ Calibration

Verf DQ 校準,Verf DQ Calibration

讀寫訓練,即存儲介質(zhì)訓練/初始校準,Read/Write Training

-

處理器

+關注

關注

68文章

19824瀏覽量

233722 -

DRAM

+關注

關注

40文章

2343瀏覽量

185239 -

子系統(tǒng)

+關注

關注

0文章

115瀏覽量

12695

原文標題:譯文:DDR4 - Initialization, Training and Calibration

文章出處:【微信號:數(shù)字芯片實驗室,微信公眾號:數(shù)字芯片實驗室】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

DDR3的MIG(xilinx)無法自動初始化和校準

DDR3初始化問題

6657的DDR3初始化不成功

如何從.mem文件初始化加密的ddr4內(nèi)存模型?

手機模塊初始化向?qū)?/a>

如何讓KeyStone DDR3接口初始化的詳細資料概述

8253初始化程序分享_8253應用案例

PCIe總線中的鏈路初始化與訓練

在51平臺下初始化文件的引入導致全局變量無法初始化的問題如何解決

跳過DDR VIP模型的初始化

DDR VIP模型的無縫快速初始化

DDR4-初始化、訓練和校準

DDR4-初始化、訓練和校準

評論