FPGA(現(xiàn)場可編程門陣列),是在可編程器件(如PAL,GAL,CPLD等)的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為ASIC領(lǐng)域的半定制電路開發(fā)的,不僅解決了定制電路的不足,而且克服了原有可編程器件柵極電路的局限性。它是當(dāng)今數(shù)字系統(tǒng)設(shè)計(jì)的主要硬件平臺,其主要特點(diǎn)是用戶可以完全通過軟件進(jìn)行配置和編程來完成特定功能。并且可以反復(fù)擦除。

在修改和升級中,不需要對PCB電路板進(jìn)行額外的更改,而只需要在計(jì)算機(jī)中修改和更新程序,使硬件設(shè)計(jì)工作成為軟件開發(fā)工作。縮短了系統(tǒng)設(shè)計(jì)的周期,提高了實(shí)施的靈活性,降低了成本。

FPGA的特點(diǎn)

1.高性能和實(shí)時性

由于FPGA芯片由數(shù)百萬個邏輯單元實(shí)現(xiàn),因此具有并行處理能力,運(yùn)行速度比單片機(jī)和DSP快得多。

2.高集成性能

FPGA可以根據(jù)用戶的需求在內(nèi)部嵌入硬/軟IP核,從而滿足不同的要求,使用SOPC技術(shù)可以節(jié)省目標(biāo)硬件的面積。

3.高可靠性、低成本

現(xiàn)在現(xiàn)在的FPGA芯片在出廠前都經(jīng)過了100%的測試,這意味著設(shè)計(jì)人員不需要承擔(dān)芯片的生產(chǎn)成本。

4.高靈活性和低功耗

FPGA是現(xiàn)場可編程的。用戶可以重復(fù)編程、擦除、使用或使用不同的設(shè)計(jì)來實(shí)現(xiàn)不同的功能,而外圍電路保持不變。這為產(chǎn)品升級和維護(hù)帶來了極大的便利。

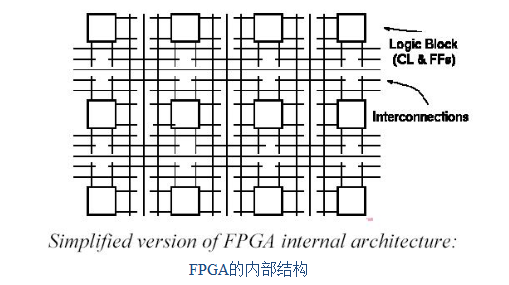

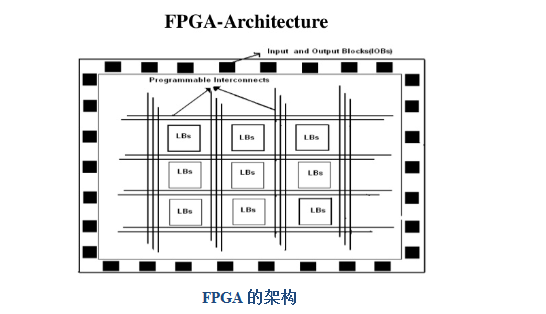

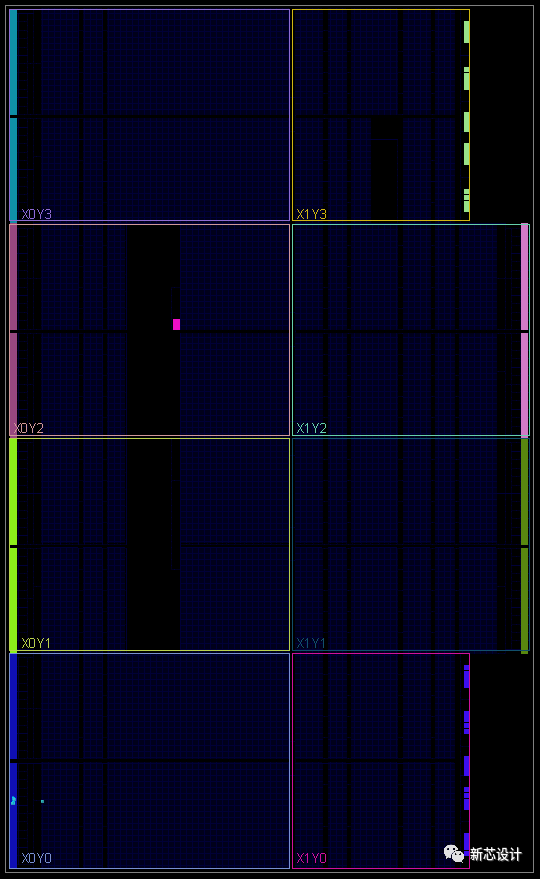

FPGA的架構(gòu)

FPGA使用邏輯單元陣列(LCA)的概念,其中包括可配置邏輯模塊CLB(可配置邏輯塊),輸入/輸出塊(IOB),互連和靜態(tài)存儲器SRAM,用于存儲編程數(shù)據(jù)。

1.可編程邏輯模塊負(fù)載均衡

CLB是邏輯功能的基本單元,通常排列成規(guī)則陣列并分散在整個芯片中。負(fù)載均衡一般由邏輯函數(shù)發(fā)生器、觸發(fā)器、數(shù)據(jù)選擇器等組成。函數(shù)發(fā)生器用于實(shí)現(xiàn)n個輸入變量的任意組合邏輯。

2.輸入/輸出模塊(IOB)

IOB在器件引腳和內(nèi)部邏輯陣列之間提供連接,主要由輸入發(fā)生器,輸入緩沖器,輸出觸發(fā)/鎖存器和輸出緩沖器組成,可以定義為具有雙向I/O功能的輸入/輸出。當(dāng)定義為輸入時,通過引腳的信號首先發(fā)送到輸入緩沖器,輸入緩沖器分為兩個通道,一個直接發(fā)送到MUX通道,另一個在延遲后發(fā)送到輸入路徑D觸發(fā)器。然后發(fā)送到數(shù)據(jù)選擇器,根據(jù)不同的控制信息判斷CLB數(shù)組是發(fā)送到輸入緩沖區(qū)還是觸發(fā)。

3.可編程互連資源紅外

IR可以在CLB和CLB之間或CLB和IOB之間連接,IR主要由許多金屬段組成。這些金屬段具有可編程開關(guān),可通過自動接線連接各種電路。芯片內(nèi)線按長度劃分:單長度線(a),雙長線(b)和長線(c)。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21985瀏覽量

615092 -

可編程器件

+關(guān)注

關(guān)注

2文章

60瀏覽量

21144

發(fā)布評論請先 登錄

FPGA架構(gòu)演進(jìn)之路 FPGA架構(gòu)設(shè)計(jì)原則和實(shí)現(xiàn)挑戰(zhàn)

什么是FPGA,FPGA是什么意思?FPGA的特點(diǎn)

FPGA架構(gòu)和應(yīng)用基礎(chǔ)知識

ARM、DSP、FPGA的技術(shù)特點(diǎn)和區(qū)別是什么

FPGA各芯片架構(gòu)特點(diǎn)

FPGA 內(nèi)部詳細(xì)架構(gòu) 精選資料分享

ARM、DSP、FPGA的區(qū)別與特點(diǎn)

FPGA 是如何引入工業(yè)驅(qū)動架構(gòu)的?

FPGA的特點(diǎn)及架構(gòu)

FPGA的特點(diǎn)及架構(gòu)

評論