前言

兩級運放是一個比較常見的模塊。其中以5管+共源級最為簡單,一般在中等增益時還是適用的。

基本概念

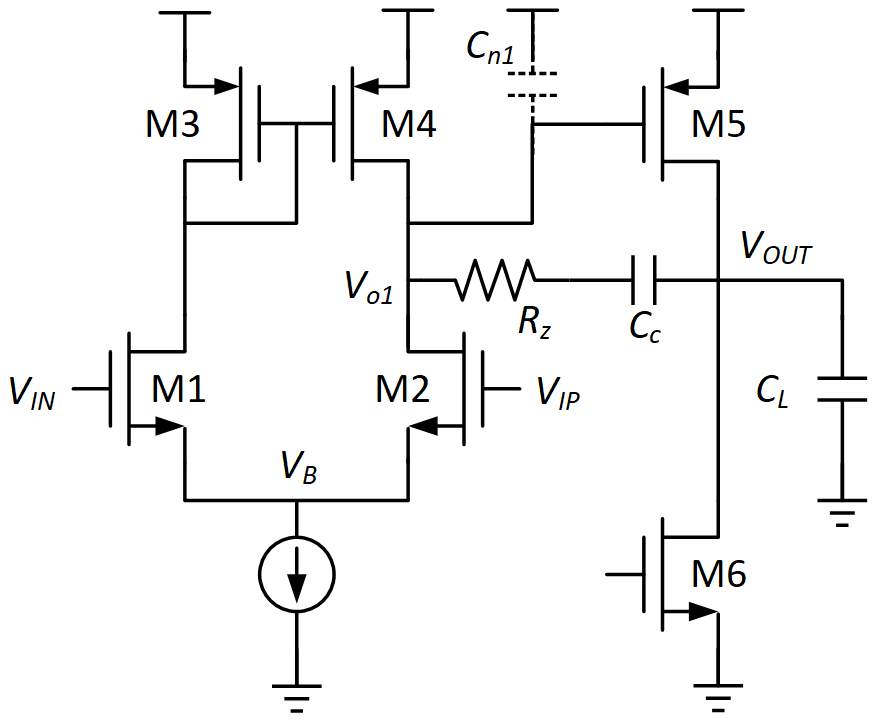

圖1 兩級運放基本結構

如圖1所示,Vout處會有一個較大的負載電容C L ,為了驅動這個大電容,M5需要較大的尺寸,導致M1、M2、M3、M4構成的第一級會看到很大的負載,這樣第一級(以后簡稱S1)的極點和第二級(以后簡稱S2)的極點相距很近,接成閉環后運放很不穩定,甚至振蕩。

為此,加入電容C c ,由于密勒效應,S1輸出節點形成一個很大的等效電容負載,極點頻率變低。對于S2,Cc跨接在M5兩端,形成了漏到柵的負反饋,減小了S2等效的輸出電阻,S2的極點變大。這就是所謂的極點分裂。

詳細的理論推導此處不再描述,直接上張老師(張鴻-西安交大)課件上的結論:(A1為第一級的增益,A2為第二級的增益,gmx代表標號為x的MOS管的跨導,其余類似) 主極點的角頻率為 式(1) :

非主極點的角頻率為 式(2) :

其中Cn1是VO1節點對交流地的總寄生電容。

對于兩級運放這樣一個二階系統,為了保證閉環后(假定反饋系數為1)系統是穩定的,ωnd和GBW應具有足夠的距離來保持足夠的相位裕度。以60°相位裕度為例,此時GBW=ω d ×(A 1 ×A 2 )=ω d ×(g m1 (r o2 ||r o4 )×A 2 )=g m1 /C c ,ω nd ≈1.5GBW。

寄生導致反復迭代

對于S2,其輸出端的寄生電容會增大VOUT節點的等效負載,因此一般手算之后需要提高S2的尺寸來保證ω nd ;另一方面,M5柵極到“交流地”的寄生會降低Cc的負反饋效果而降低ω nd ,所以需要反復迭代。

對于S1,理論上的負載電容為A 2 ×C c ;事實上,Cgd5也是密勒電容的一部分,C gs5 +Cgb5也增加了一部分負載。這樣,VO1節點的等效負載為A 2 ×(C c +C gd5 )+C gs5 +C gb5 ,式(1)重寫為:

在S1的輸出端,M2和M4的漏端寄生電容也會降低Cc的反饋效果,拉低ω nd 。

整體思路

給定負載、電流、帶寬、增益4個參數,且 假設S2輸入級的DC值已經根據輸出擺幅確定好 ,整體運行思路如下:

- A: 設定S2的初始增益,求解S2的尺寸,讀取S2的各個寄生和總電流;

- B: 計算S1的可用電流,將S2的寄生折算為S1的負載,求解S1尺寸;

- C: 迭代優化S1輸出節點的寄生電容;

- D: S1+S2拼接,掃描調零電阻。

Step1:確定S2

當S2的增益A2和M5的DC偏置點確定之后,假定S1輸出點寄生C node =1pF(Cnode主要由M2和M4的漏端電容構成,后面會再提到):

python調用hspice掃描M5的L,獲取“當g m5 ×r out5 =2×A 2 ”的L值,獲取此時M5的r out5 ×id5;

繼續掃描M6的L,獲取“r out6 ×i d6 =r out5 ×i d5 ”的L值(這個方法在求解S1時也會用到),那么此時所選取的M6的溝長,能使M6在流過和M5相同電流的情況下,得到和M5相同的輸出電阻。此時,hspice掃描得到gm5和C gs5 +C gb5 ,C gd5 ,C ds5 +C db5 +Cdd6的比例關系,ωnd的表達式參考拉扎維式10.24重寫如下 式(3) :

其中ωnd的目標值為1.5GBW,RL是S2的輸出電阻,值為A 2 /g m5 。

C mil 、C Lx 、Ce分別為考慮S2寄生電容后的總密勒值,總負載值和VO1節點的總寄生值(包含C node ),這3個變量均由1個固定值+1個與gm成正比的值組成。

直接求解式(3)(化簡后是一個一元二次方程),獲取gm5的最終值g m_target 。gm_target除以當前gm5的值,即可得到M5的finger數;同時也可得到S2預期的電流值cur2。

式(3)可能無解或最終求出一個很大的cur2,此時說明Cc太小,寄生對極點分裂的削弱作用過大,迭代Cc重新求解(這部分可由程序自動進行)。

有可能通過一個很大的Cc來使(3)具有一個合適的解,但此時S1的等效負載會很大,導致S1無解,此時說明當前的增益分配不合理,調整S2的增益,重新迭代。

Step2: 確定S1

如前所述,S2解出之后,需要回傳一些參數:

一是S2的預期電流cur2,總電流-cur2即為S1可接受的電流;

二是S2的C gd5 、Cgs5和C gb5 ,A 2 (C gd5 +C c )+C gs5 +Cgb5是第一級總的負載電容。在這個負載電容下,S1所產生的主極點頻率為ω d =GBW/(A 1 ×A 2 ),結合式(1)可以確定S1的輸出電阻;S1增益為A 1 ,所以S1預期的跨導gm_s1可以確定.

相比于S2,S1多出了一個需要優化的變量,源端電壓V B 。對于N管,VB越大,Vod越小,g m /id越大;但同時需要的管子面積可能也越大,帶來很大的寄生電容。

當VB較小時,實現同樣的gm會需要更大的電流,但是總面積可能減小;也有可能增大,因為Vgs較大時,MOS管實現相同的本征增益可能需要更大的L。

VB大了不行,小了也不行,還是讓代碼直接迭代吧。

首先,掃描一個基本管子的V th ,進而確定VB使Vod在300mV左右,VB從此時開始迭代。

從180n10u掃描MOS管的增益,得出合適的L(記為L1)后計算其g m_s1m /i d ,滿足要求則擴展MOS管的finger,達到g的跨導;否則增加V dB ,直至求出同時滿足增益和g m /i的M1/M2尺寸;按照前述r d~相等的原則確定M3/M4的尺寸。out *i

計算此時M2和M4帶來的寄生電容C par1 ,將L的求解范圍設為(180n ~ L1 - 50n),繼續求解。當解出的寄生電容比上次寄生電容大,或者無解時,停止迭代。此時即解出了S1的尺寸參數,且此時S1在VO1節點產生的寄生電容是最小的。

如果一開始即設置了一個合適的C node ,最后解出的S1輸出點的寄生電容小于這個預設值,此時迭代已經完成了,電路拼接之后即可實現預期的帶寬和相位裕度。

如果解出的S1輸出寄生大于預設的C node ,重新標定Cnode并再次先后求解S2和S1即可。

注意,上述求解過程中為了方便程序迭代,VB是一個固定電壓,全差分電路時這樣是可以的,在差分轉單端電路中,VB并不能按照固定電壓處理,需要將VB換成一個MOS電流源。

Step3: 調零電阻Rz

對調零電阻帶來的影響進行詳細推導需要大量篇幅,此處直接迭代Rz并根據GBW和相位裕度更新,得到一個滿足要求的解即可。

題外話

兩級運放如果直接采用5管,也很難做到較高增益。當S1增益很大時,其輸出點VO1的寄生電容很高,會導致S2的功耗很高甚至是式(3)無解;所以高增益時還是共源共柵+兩級更好一點,這樣VO1節點的寄生電容相對較小(個人觀點)。

考慮到Rz的調節作用,S2的設計可以更激進一些。例如為了滿足60°相位裕度,ωnd的目標從1.5GBW下降到1GBW,最后用Rz調出正確結果。

-

MOS管

+關注

關注

109文章

2552瀏覽量

70396 -

寄生電容

+關注

關注

1文章

298瀏覽量

19732 -

python

+關注

關注

56文章

4825瀏覽量

86494 -

差分電路

+關注

關注

2文章

59瀏覽量

23666 -

運放器

+關注

關注

0文章

12瀏覽量

6929

發布評論請先 登錄

OPA2350兩級放大后輸出飽和問題怎么解決?

封裝在一起的雙運放或四運放參數比較接近,是否可以設計電路經過兩級或更多級將失調電壓抵消掉?

設計了OPA657的兩級運放,出現了波形失真的原因?

PIN管運放兩級放大,第一級引入背景噪聲,怎么去除?

請問兩級運算放大器的建立時間如何估算?

請問兩級運算放大器的建立時間如何估算?

共源共柵兩級運放中兩種補償方法的比較

Ansible企業級自動化運維探索的詳細資料說明

兩級運放的自動化設計思路

兩級運放的自動化設計思路

評論