|

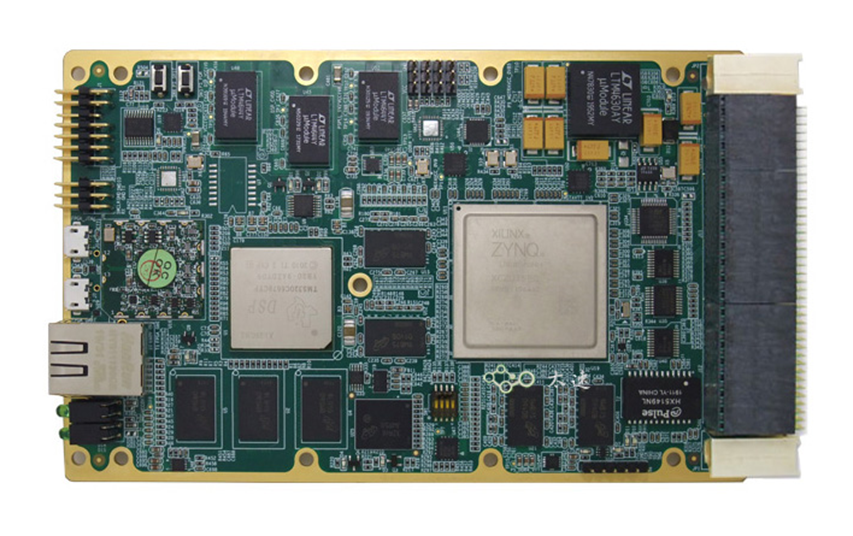

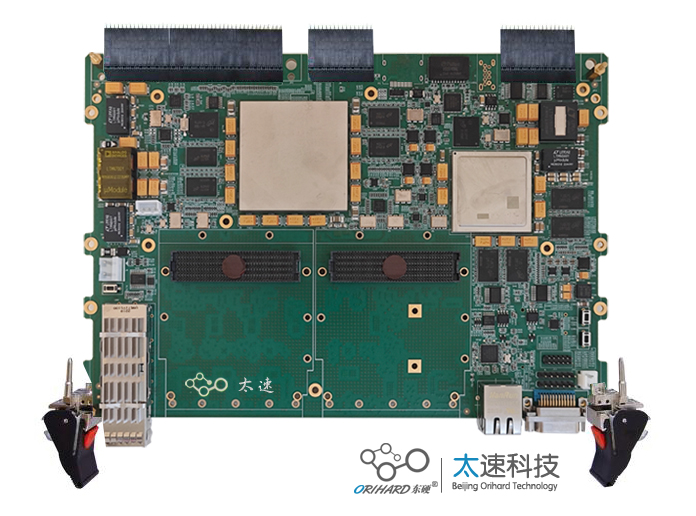

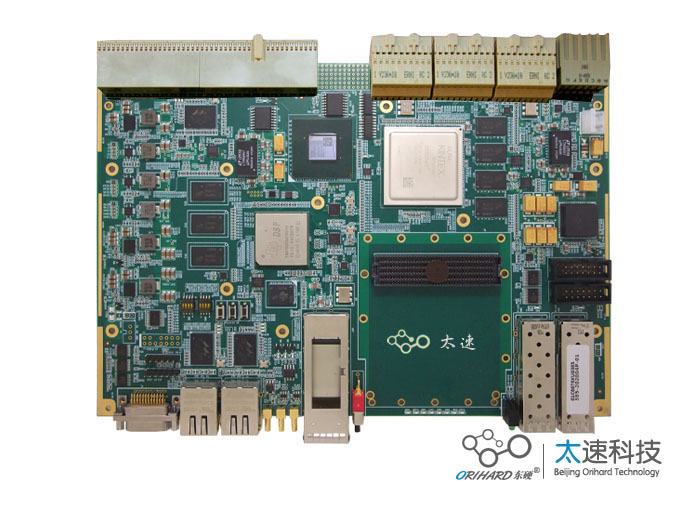

一、板卡概述 本板卡基于Xilinx Zynq Ultrascale+ MPSOC系列SOC XCZU15EG-FFVB1156架構,PS端搭載一組64-bit DDR4,容量32Gb,最高可穩(wěn)定運行在2400MT/s,1路USB3.0接口、1路千兆網(wǎng)絡接口、1路DP接口,2路RS232,2路Can接口。板卡具有自控上電順序,支持多種啟動模式,如Nor Flash啟動,EMMC啟動,SD卡啟動等。PL端接一組64-bit DDR4,容量32Gb,最高可穩(wěn)定運行在2400MT/s;接雙FMC連接器,1組連接8個GTH,LA,HA,HB總線,1組連接8個GTH,LA總線。另有2路40G QSFP光纖接口。北京太速科技板卡,設計滿足工業(yè)級要求,可用于高速信號處理、車載雷達信號處理等領域。實物如圖所示: 圖 1:ZU15EG板卡實物圖 |

|

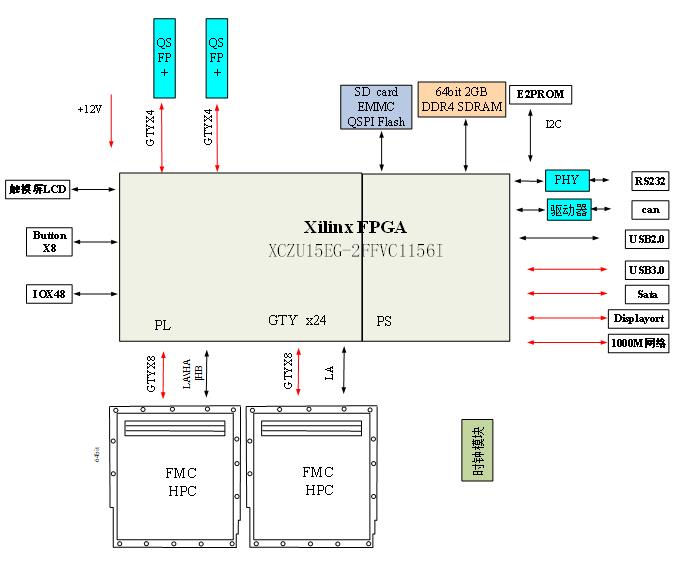

圖 2:ZU15EG板卡原理框圖 二、技術指標 ●PS端掛載一簇DDR4,數(shù)據(jù)位寬64-bit,容量32Gb,最高可穩(wěn)定運行在2400MT/s; ●PS端掛載兩片QSPI x4 NorFlash,每片容量512Mb,用于系統(tǒng)配置程序存儲; ●PS端掛載掛一片EMMC,64Gb容量,可用于系統(tǒng)配置程序存儲; ●PS端外掛SD卡接口,最大支持搜索8192個文件數(shù),可用于系統(tǒng)配置程序存儲; ●PS端外接Display Port接口,支持Display Port 1.2a協(xié)議標準,僅支持對外輸出; ●PS端外接一路千兆以太網(wǎng)接口,支持10/100/1000Mbps速率傳輸; ●PS端外接一路USB3.0接口,最大速率可達5Gbps; ●PL端掛載一片SPI接口的DataFlash,容量16Mb,可用于存儲系統(tǒng)參數(shù)信息; ●PL端通過SPI外接兩組獨立CAN FD控制器,CAN FD接口最高速率可達5Mbps; ●PL端外接2路QSFP+接口,最高支持40Gbps數(shù)據(jù)傳輸速率; ●PL端外接2組FMC總線,支持1組8個GTH,LA,HA,HB總線,另外1組8個GTH,LA總線; ●板卡外接兩路RS232接口,由PS端UART轉(zhuǎn)出,可用于系統(tǒng)調(diào)試及狀態(tài)信息打印; ●板卡留有多路用戶自定義測試IO管腳; ●板卡留有一組4位用戶自定義撥碼開關; ●板卡芯片全部采用工業(yè)級芯片; 三、軟件內(nèi)容 ●PS端QSPI加載測試代碼; ●PS端EMMC加載測試代碼; ●PS端SD卡加載測試代碼; ●PS端Display Port接口測試代碼; ●PS端USB3.0接口測試代碼; ●PS端DDR4讀寫測試代碼; ●PS端千兆網(wǎng)口收發(fā)測試代碼; ●PS端UART接口讀寫測試代碼; ●PL端SPI接口的DataFlash讀寫測試代碼; ●PL端QSFP+接口ibert模式測試代碼; ●PL端CAN FD接口測試代碼; ●其它GPIO信號連通性測試代碼; 四、物理特性 ●工作溫度:商業(yè)級 0℃ ~ +55℃,工業(yè)級-40℃~+85℃ ● 工作濕度:10%~80% 五、供電要求 ●單電源供電,整板最大功耗:30W ● 電壓:+12VDC±10%@5A 六、應用領域 高速信號處理、車載雷達信號處理等。 |

審核編輯 黃宇

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學習之用,如有內(nèi)容侵權或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

FMC

+關注

關注

0文章

103瀏覽量

20121 -

信號處理板

+關注

關注

0文章

23瀏覽量

8776

發(fā)布評論請先 登錄

相關推薦

熱點推薦

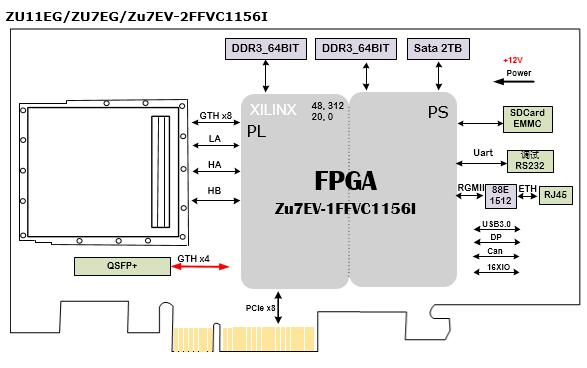

圖像信號分析處理卡設計原理圖:536-基于FMC接口的XCZU7EV 通用PCIe卡 視覺處理卡 工業(yè)控制卡

XCZU7EV 通用PCIe卡 , 圖像信號分析處理卡 , 視覺處理卡 , 工業(yè)控制卡 , 存儲擴展卡

國產(chǎn)化FMC接口通用計算平臺設計原理圖:2367-基于FMQL45T900 FMC接口通用計算平臺

, 數(shù)字信號處理卡, FMC接口通用計算平臺, FMQL45T900I, 前端信號處理

XILINX XCZU67DR FPGA完整原理圖

電子發(fā)燒友網(wǎng)站提供《XILINX XCZU67DR FPGA完整原理圖.pdf》資料免費下載

發(fā)表于 05-30 15:29

?0次下載

527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

ZynqUltraScale+系列FPGA XCZU15EG,一片TI公司的多核浮點處理器TMS320C6678,一片STM32 MCU用于板卡狀態(tài)監(jiān)控、電源控制及健康管理功能,板卡集成多片DDR、Flash

基于FMC接口的XCZU7EV?通用PCIe卡

基于通用PCIe ,實現(xiàn)FMC的數(shù)據(jù)接口和主控計算,廣泛應用于工業(yè)控制,檢測,視覺處理。支持工業(yè)級溫度工作。

電路板 Layout 的混合信號 PCB 設計指南

?本文重點在混合信號PCBLayout上布線在混合信號設計中放置器件。電源分配網(wǎng)絡的混合信號PCB設計要求。以前,電子產(chǎn)品包含多個電路板,每塊電路板

高速圖像處理卡設計原理圖:527-基于3U VPX XCZU15EG+TMS320C6678的信號處理板

C6678信號處理板 , FPGA 信號處理 , FPGA開發(fā)平臺 , XC7Z045板卡 , XCZU

FMC子卡設計方案:202-基于TI DSP TMS320C6678、Xilinx K7 FPGA XC7K325T的高速數(shù)據(jù)處理核心板

AD FMC子卡 , FMC子卡 , FMC子卡模塊 , XC7K420T處理板 , 圖像FMC

PCB板厚度對信號傳輸?shù)挠绊?/a>

PCB板的厚度對其信號傳輸性能有著顯著的影響。以下是詳細分析: 1、信號傳輸速度 PCB板的厚度會影響信號傳輸?shù)乃俣取R话銇碚f,較薄的PCB

高速數(shù)據(jù)計算卡設計原理圖:512-基于ZU19EG的4路100G 8路40G的光纖匯流計算卡

ZU19EG板卡 , ZU19EG處理板 , ZU19EG開發(fā)板 , 光纖匯流計算卡 , ZU1

DAC38J84EVM SYNC信號無法通過FMC-LHC接口輸入到FPGA,怎么解決?

我在使用一塊第三方的alinx xczu9eg ultrascale+mpsoc開發(fā)板進行基于JESD204B的DA開發(fā).

我現(xiàn)在使用的FMC子板是DAC38J84EVM , 其中D

發(fā)表于 11-26 06:43

基于6U VPX XCVU9P+XCZU7EV的雙FMC信號處理板卡

板卡基于6U VPX標準結構,包含一個XCVU9P 高性能FPGA,一片XCZU7EV FPGA,用于 IO擴展接口,雙路HPC FMC擴展高速AD、DA、光纖接口等。是理想應用于高性能數(shù)字計算,光纖加速的板卡。 板卡全工業(yè)級芯

通用信號處理板設計原理圖:523-基于XCZU15EG的雙 FMC通用信號處理板

通用信號處理板設計原理圖:523-基于XCZU15EG的雙 FMC通用信號處理板

評論