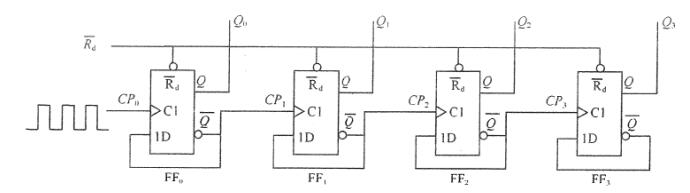

一、時序邏輯

時序邏輯是Verilog HDL 設計中另一類重要應用。從電路特征上看來,其特點為任意時刻的輸出不僅取決于該時刻的輸入,而且還和電路原來的狀態(tài)有關。

從電路行為上講,不管輸入如何變化,僅當時鐘的沿(上升沿或下降沿)到達時,才有可能使輸出發(fā)生變化。

1、在描述時序電路的always塊中的reg型信號都會被綜合成寄存器,這是和組合邏輯電路所不同的。

2、時序邏輯中推薦使用非阻塞賦值“<=”。

3、時序邏輯的敏感信號列表只需要加入所用的時鐘觸發(fā)沿即可,其余所有的輸入和條件判斷信號都不用加入,這是因為時序邏輯是通過時鐘信號的跳變沿來控制的。

二、時序邏輯在FPGA里RTL實現(xiàn)

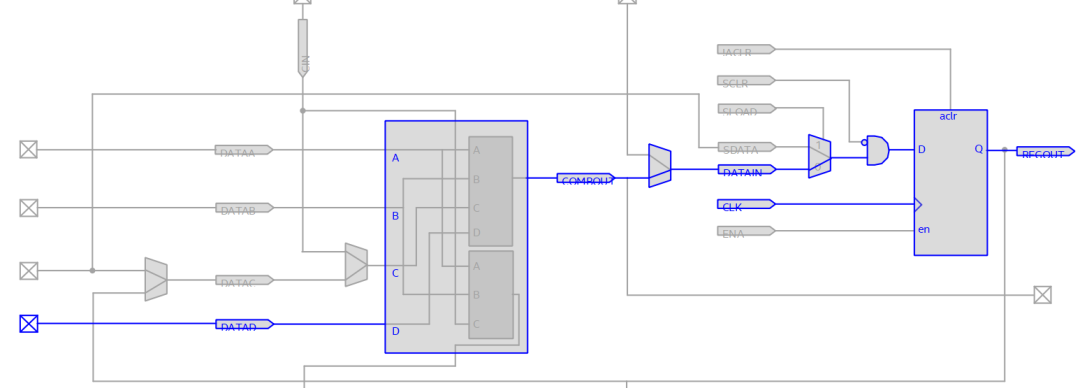

我們寫一個簡單的寄存器,看看fpga是怎樣實現(xiàn)時序邏輯的

module counter( input a, input clk, output reg q ); always@(posedge clk)begin q <= a; end endmodule

我們看一下fpga的芯片規(guī)劃器

從芯片規(guī)劃器,可以看出來幾個細節(jié)。

1、我們用了一個查找表、一個寄存器。對FPGA來說,這個寄存器你就算不使用他也是在那里的

2、我么的輸出信號是與clk同步的,必須要等到clk的上升沿到來是,輸出才會更新,因此就實現(xiàn)了寄存器的功能

三、同步復位、異步復位

1、同步復位:其實就是你的操作和時鐘的上升沿同步

舉個例子,你要將q設置為0,下面這代碼就是同步復位,q <= 0,是在時鐘上升沿到來時執(zhí)行的,所以是同步復位

module counter(

input a,

input clk,

output reg q

);

always@(posedge clk)begin

q <= 0;

end

endmodule

2、異步復位:其實就是你的操作和時鐘沒有關系

舉個例子,你要將q設置為0,下面這代碼就是異步復位,q <= 0,無論時鐘是什么狀態(tài),只有rst_n到來就執(zhí)行清零

module counter(

input a,

input clk,

input rst_n,

output reg [7:0] q

);

always@(posedge clk,negedge rst_n)begin

if(!rst_n)

q <= 0;

else

q <= q + 1'b1;

end

endmodule

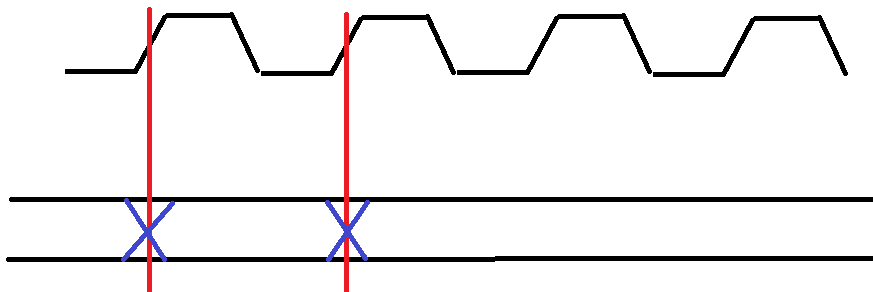

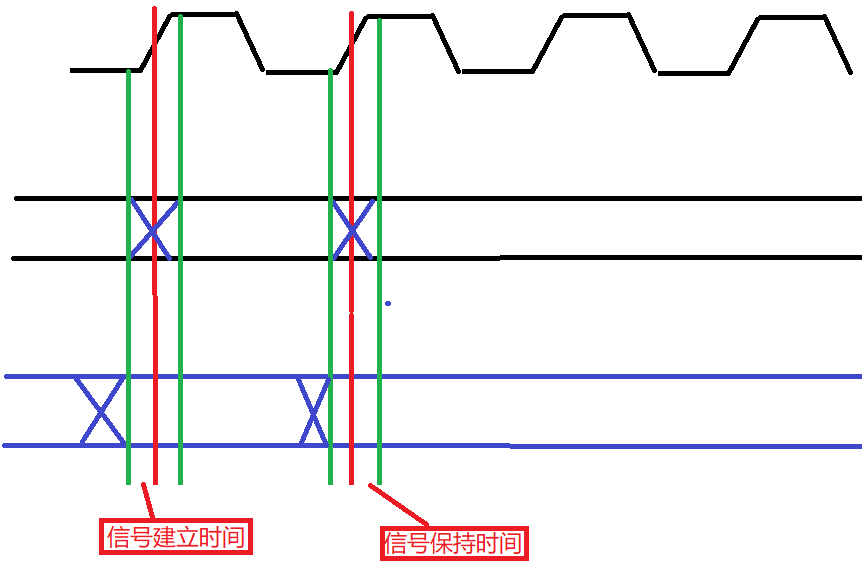

四、競爭冒險

競爭冒險:意思是,在我時鐘的上升沿進行采樣時,輸入信號處于不穩(wěn)定狀態(tài),這個會給電路帶來亞穩(wěn)態(tài)的問題

為了解決競爭冒險,我們只要滿足信號的建立時間和保持時間即可

五、verilog語法補充

1、parameter 定義全局變量

parameter T = 26'd49_000_000;

2、defparam重新定義參數(shù),這個主要是在仿真腳本修改例化的模塊的內(nèi)部參數(shù)

defparam counter_inst.T = 26'd49; counter counter_inst( .clk (clk), .rst_n (rst_n), .flag (flag)

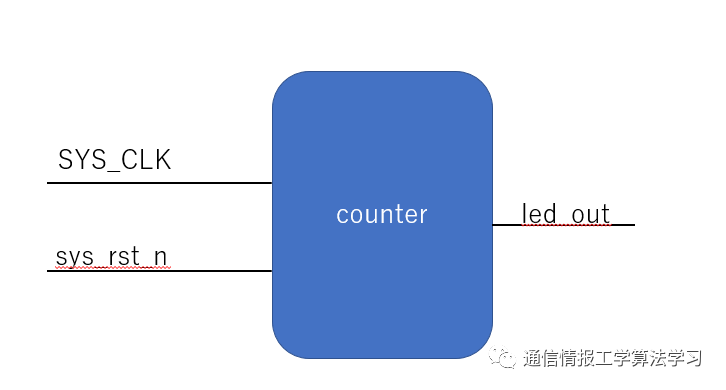

六、計數(shù)器設計

設計一個1秒的計數(shù)器,當時間到一秒后給出一個flag信號

1、代碼實現(xiàn) verilog.v

module counter(

input clk,

input rst_n,

output reg flag

);

reg [25:0] count;

parameter T = 26'd49_000_000;

always@(posedge clk,negedge rst_n)begin

if(!rst_n)begin

flag <= 1'b0;

count <= 0;

end

else if(count == T)begin

flag <= 1'b1;

count <= 0;

end

else

begin

count <= count + 1'b1;

flag <= 1'b0;

end

end

endmodule

2、仿真腳本

我在仿真腳本將時間參數(shù)改為T改為 T=26‘d49;方便仿真

`timescale 1ns/1ps module counter_tb; reg clk; reg rst_n; wire flag; defparam counter_inst.T = 26'd49; counter counter_inst( .clk (clk), .rst_n (rst_n), .flag (flag) ); always #10 clk = ~clk; initial begin clk = 0; rst_n = 0; #20; rst_n = 1; #5000000; $stop; end endmodule

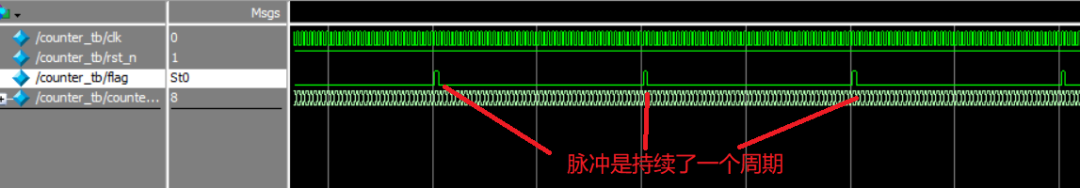

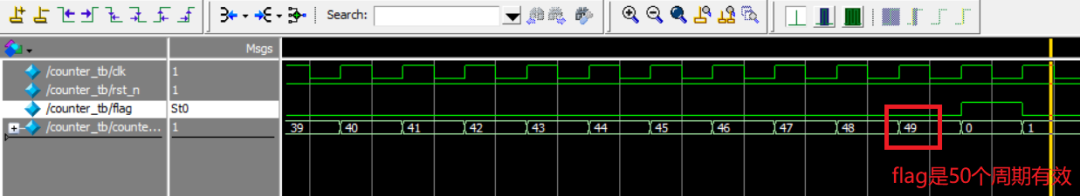

3、仿真結(jié)果

1、可以看出脈沖flag只持續(xù)了一個周期

2、可以看出脈沖的觸發(fā)是50個計數(shù)值

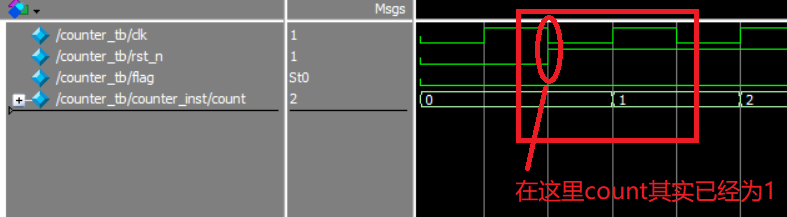

七、計數(shù)器里隱藏的加法器問題

我們設計的這個計數(shù)器,里面其實用了一個加法器,加法器是組合邏輯(因為組合邏輯只取決于輸入)

當我們給加法器一個初值0的時候,加法器的輸出立即就輸出1,這就是仿真的時候,開始復位拉高后,count在第一個clk上升沿就為1的原因

審核編輯:劉清

-

FPGA

+關注

關注

1644文章

22002瀏覽量

615892 -

邏輯電路

+關注

關注

13文章

502瀏覽量

43244 -

寄存器

+關注

關注

31文章

5428瀏覽量

123809 -

Verilog

+關注

關注

29文章

1366瀏覽量

112012 -

計數(shù)器

+關注

關注

32文章

2290瀏覽量

96195 -

時序邏輯電路

+關注

關注

2文章

94瀏覽量

16805 -

開發(fā)板

+關注

關注

25文章

5602瀏覽量

103344 -

FPGA開發(fā)板

+關注

關注

10文章

124瀏覽量

31915 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8517

原文標題:筆記連載精選 |【時序邏輯、競爭冒險、同步復位、異步復位】之【計數(shù)器設計、verilog語法補充】

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

時序電路設計的計數(shù)器詳解

中規(guī)模集成時序邏輯設計

時序邏輯電路

計數(shù)器,計數(shù)器的工作原理是什么?

基于Multisim的計數(shù)器設計仿真

采用中規(guī)模集成計數(shù)器進行任意進制計數(shù)器設計的解決方案

同步計數(shù)器和異步計數(shù)器是什么 同步計數(shù)器和異步計數(shù)器的主要區(qū)別?

時序邏輯電路設計之異步計數(shù)器

設計一個計數(shù)器來講解時序邏輯

設計一個計數(shù)器來講解時序邏輯

評論