前不久一位朋友發來一道驗證題,雖然題目不是很復雜,但是琢磨了下感覺其中需要掌握的內容還是很多的,正所謂麻雀雖小五臟俱全。下面將對此題涉及的一些內容進行挖掘和示例,與大家分享下。

【問題描述】

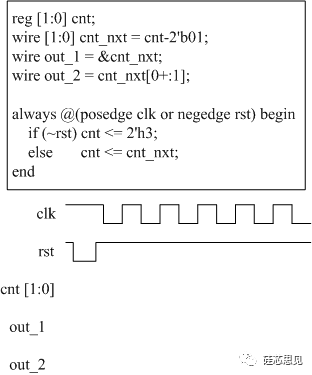

如下一段Verilog代碼,請根據代碼的描述,并結合已知的clk和rst的波形圖,畫出對應信號的波形。

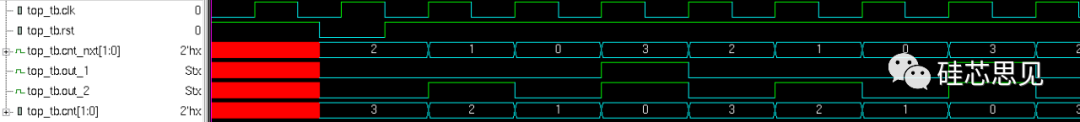

通過仿真工具得到對應的仿真波形如下。

【仿真波形】

【知識點挖掘】

0.reg和wire都采用的四值邏輯

reg變量在未進行賦值時,其默認值為x,wire默認為z,上圖中cnt_nxt之所以仿真開始時為不定態,主要是因為它是由cnt進行運算后得到的,而cnt剛開始就是個x。

1.變量和線網聲明時初始化

線網在聲明的同時進行賦值操作實際上完成的是一種隱含的連續賦值操作(implicit continuous assignment),即相當于該線網從聲明的時候就開始采用了連續賦值操作,此時如果有其他對于該線網的賦值操作,將會導致多驅動;與之相對應的是變量在聲明時的初始化,實際上僅僅完成了對于該變量真正的初始化操作,后續對該變量的賦值操作將會覆蓋聲明時初始化的值。

示例詳見《硅芯思見:【173】隱藏的初始化》

2.縮減操作符

| 操作符 | 作用 |

| &(縮減與) | 操作數中只要有任意一位的值為0,則操作的結果就為0;操作數中只要有任意一位的值為x或者z,則操作的結果就為x;否則結果為1 |

| ~&(縮減與非) | 上述結果取反即可 |

| |(縮減或) | 操作數中只要有任意一位的值為1,則操作的結果就為1;操作數中只要有任意一位的值為x或者z,則操作的結果就為x;否則結果為0 |

| ~|(縮減或非) | 上述結果取反即可 |

| ^(縮減異或) | 操作數中只要有任意一位的值為x或者z,則操作的結果就為x;若操作數中有偶數個1,則操作結果為0;否則其操作結果為1 |

| ~^(縮減同或) | 上述結果取反即可 |

3.阻塞賦值與非阻塞賦值區別

詳見《Verilog系列:【17】阻塞賦值與非阻塞賦值》

| 阻塞賦值(blocking assignment) | 非阻塞賦值(non-blocking assignment) |

| 格式:“LHS”=“RHS” | 格式:“LHS”<= “RHS” |

| 阻塞賦值RHS會延遲指定延遲(如果沒有指定就是0延遲,如果指定了非零延遲,那么就延遲非零延遲,關于延遲位置不同結果不同可參見topic“阻塞賦值中的延遲”)后立即更新至LHS | 非阻塞賦值LHS會在當前仿真時間槽(time-slot)最后被更新,即RHS變化后不會立即反應在LHS上 |

| 當多條阻塞賦值語句順序出現在同一個進程中時,所有的語句按順序執行,即后續的語句必須在當前賦值操作完成后才能進行 | 同一個進程中的非阻塞賦值在同一個時間槽中是同時執行的,即不會互相阻塞 |

| 建議在組合邏輯的結構中使用 | 建議在時序邏輯進程中使用 |

| 可以在過程性賦值和連續性賦值中使用 | 建議在時序進程中使用 |

| 當阻塞賦值中的變量同時出現在不同的進程中時,可能會出現競爭的情況 | 非阻塞賦值LHS更新在仿真時間槽的最后,可以在一定程度上避免競爭的出現 |

|

【示例】 initial begin temp_1 = #5 2'b10; temp_2 = #1 2'b01; end 從仿真0時刻開始,temp_1在時刻5被賦值為2'b10,temp_2在時刻6(5+1)被賦值為2'b01,即temp_2更新發生在temp_1之后,即兩次賦值有先后順序 |

【示例】 initial begin temp_1 <= #5 2'b10; temp_2 <= #1 2'b01; end 從仿真0時刻開始,temp_1在時刻5被賦值為2'b10,temp_2在時刻1被賦值為2'b01,即temp_2更新發生在temp_1之前,即兩次賦值從同一時刻同時開始 |

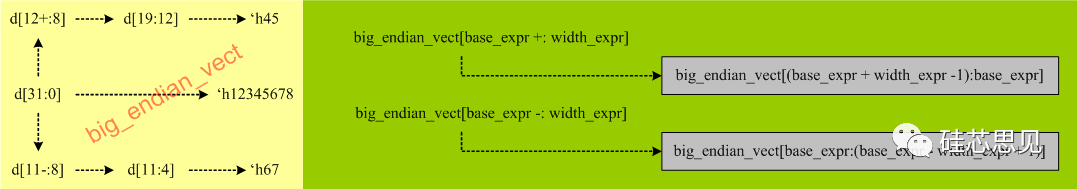

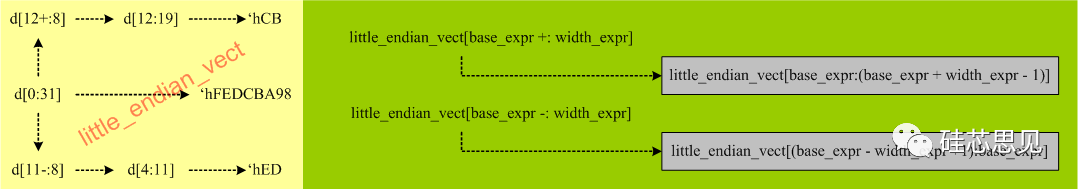

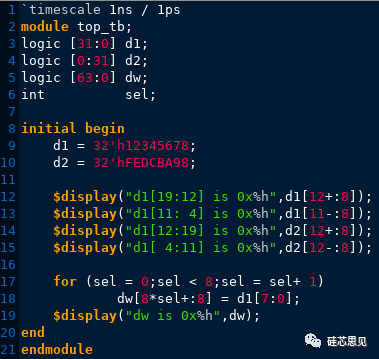

4.+:和-:位選操作

如果base_expr和width_expr經過位選后超過d本身的位寬,那么讀取超出部分將獲得不定態表示。其中base_expr是可以在仿真運行過程中按照需要變化的,但是width_expr是必須是確定的。

【示例】

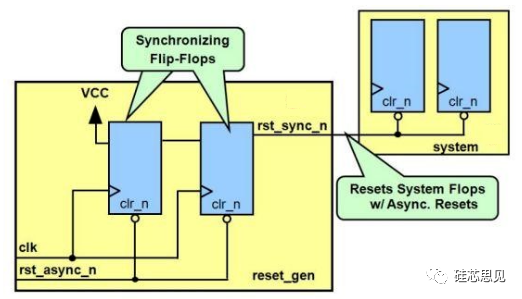

【仿真結果】

5.wire和reg分別在什么時候使用

wire常用于連續賦值語句(連續賦值語句左側信號)、模塊端口(input、output、inout,其中注意output默認為wire),reg常用于過程性賦值語句(當然也可以位于連續賦值語句的右側),關于連續賦值語句和過程性賦值語句的關系可以參看《Verilog系列:【32】Verilog中的幾種賦值語句》

6.異步復位、同步復位和異步復位同步撤銷

復位主要用于將數字電路中的觸發器置為一個確定的初始值上,例如可以是狀態機工作于初始狀態。而觸發器一般情況下分為兩種:一種是有復位引腳的,一種是沒有復位引腳的,帶有復位的觸發器占用的面積比沒有復位引腳的觸發器大一些。一般情況下,處于數據路徑上的觸發器的初始值無關緊要,此時可以使用不帶復位引腳的觸發器,以降低芯片的面積。兩者之間的優缺點如下。

【同步復位】

l抗干擾性強,可以容忍一定的毛刺,但是前提是這個毛刺不要出現在setup和hold違例區間;

l利于后端人員進行STA分析;

l觸發器的復位信號完全同步于時鐘源,確保時鐘和復位作用下的邏輯電路的一致性;

l復位信號要確保大于時鐘周期,避免沒有被采樣到;

l因為觸發器本身不帶復位引腳,綜合后會增加很多其他的邏輯資源;

l如果時鐘信號出現問題,可能會影響到復位;

【異步復位】

相較于同步復位,異步復位有以下特點。

l復位信號不依賴于時鐘;

l大多數庫提供的觸發器都是自帶異步復位的觸發器;

l異步復位不管產生或撤銷復位信號,都是一個異步過程,但是撤銷時就出現了問題,如果異步復位在觸發器時鐘有效沿附近釋放,觸發器的輸出就會進入亞穩態,因此導致復位狀態丟失;

l毛刺容易對電路造成干擾,導致不期望的復位產生;

l異步復位需要滿足時序要求(recover time、remove time,類似于setup和hold);

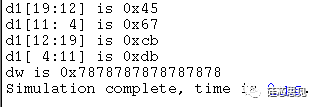

為了綜合兩種復位的優缺點,提出了一種異步復位同步釋放的方式,就是指在復位信號到來的時候不受時鐘信號的同步,而是在復位信號釋放的時候受到時鐘信號的同步,即用一個同步器來將異步復位信號轉換為同步的復位信號,從而確保復位操作的可控性和穩定性。。其典型結構圖如下。

其操作過程如下為當復位信號rst_async_n有效時,第一個D觸發器的輸出是低電平,第二個D觸發器的輸出rst_sync_n也為低電平,此時驅動后級方框中的異步復位端口有效,其輸出被復位。復位撤銷時,rst_async_n經過兩級觸發器同步后得到的rst_sync_n是與時鐘同步的,從而可以實現復位的同步撤銷。假設rst_async_n在clk的上升沿時撤除,那么第一個大黃框中的第一級觸發器處于亞穩態,但是由于兩級觸發器的同步作用,第二級觸發器的輸入為clk到來前第一級觸發器的輸出,即為低電平。因此,此時第二級觸發器的輸出一定是穩定的低電平,方框左中觸發器此時還處于復位狀態。在第二個clk到來時,第一級觸發器的輸出已經是穩定的高電平了,故rst_sync_n已經是穩定的高電平,此時復位釋放,也就是同步釋放。

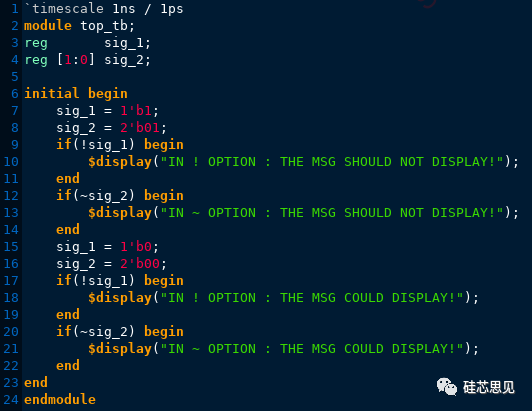

7.~和!區別

首先條件判斷語句根據根據判斷其關鍵字后的條件判斷表達式結果的真假(非零的結果被認為"真",零的結果對應為"假")來選擇不同的條件分支,即可以將條件表達式分為兩步來實現:第一步計算條件表達式,第二步判斷條件表達式結果;其次,在Verilog中"!"的意思為邏輯非,"~"為按位操作符, "!"主要是對操作數進行邏輯非操作,其預算結果只能為"0"(假)或者"1"(真),"~"主要是對操作數進行按位運算,即對操作數的每一位進行取反操作.但是這里需要注意的是對于一位數據來說,兩種操作的結果是一樣的,但是如果操作數為多位數據,那么兩個操作的運算結果將會不一樣.使用邏輯操作符"!",在進行位運算時使用按位運算符"

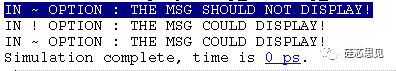

【示例】

【仿真結果】

從上例仿真結果可以觀測到,代碼10行沒有執行,13行執行。代碼中9行的條件判斷語句"if(!sig_1)"中的"!sig_1"計算結果為"0",條件表達式對應的分支不會執行,所以仿真過程中并沒有顯示對應的消息;12行的"if(~sig_2)"中的"~sig_2"計算結果為"2'b10",為非零值,即條件表達式判斷的條件為真,所以對應的分支被有效執行;17和20行兩個條件表達式都為真,所以對應的分支都被有效執行,但是這時需要注意兩個條件表達式的具體計算結果并不相同,17行"!sig_1"計算結果為"1",而20行"~sig_2"計算結果為"2'b11",兩者的相同點是均為非零值,所以對于條件語句來說都是為真的條件,所以對應的分支會被執行.在具體使用這兩種操作符的時候,一般情況下推薦進行邏輯判斷時~"。

審核編輯:湯梓紅

-

仿真

+關注

關注

51文章

4212瀏覽量

135079 -

信號

+關注

關注

11文章

2834瀏覽量

77741 -

Verilog

+關注

關注

28文章

1364瀏覽量

111514 -

波形圖

+關注

關注

1文章

35瀏覽量

15116 -

代碼

+關注

關注

30文章

4880瀏覽量

70031

原文標題:一道設計&驗證“麻雀”題

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Xilinx FPGA異步復位同步釋放—同步后的復位該當作同步復位還是異步復位?

阻塞賦值與非阻塞賦值區別 異步復位、同步復位和異步復位同步撤銷

阻塞賦值與非阻塞賦值區別 異步復位、同步復位和異步復位同步撤銷

評論