問題

最近在使用 STM32F3 芯片的時候,遇到這樣一個問題:如果外部中斷來的頻率足夠快,上一個中斷沒有處理完成,新來的中斷如何處理? 在調試時,發現有中斷有 掛起、激活、失能等狀態,考慮這些狀態都是干啥用的呢!他們是 Cortex-M 核所共有的,因此,這里不針對與具體用的 STM32 MCU,直接上升到 Cortex-M 內核來了解一下!

簡介

中斷(也稱為“異常”)是微控制器一個很常見的特性。中斷一般是由硬件(例如外設、外部引腳)產生,當中斷產生以后 CPU 就會中斷當前的程序執行流程轉而去處理中斷服務中指定的操作。

所有的 Cortex-M 內核都會包含一個用于中斷處理的組件:NVIC(Nested Vectored Interrupt Controller,嵌套向量中斷控制器)。它處理處理中斷,還處理其他需要服務的事件(例如 SVC 指令),通常稱為異常(按照 ARM 的說法,中斷也是一種異常)。

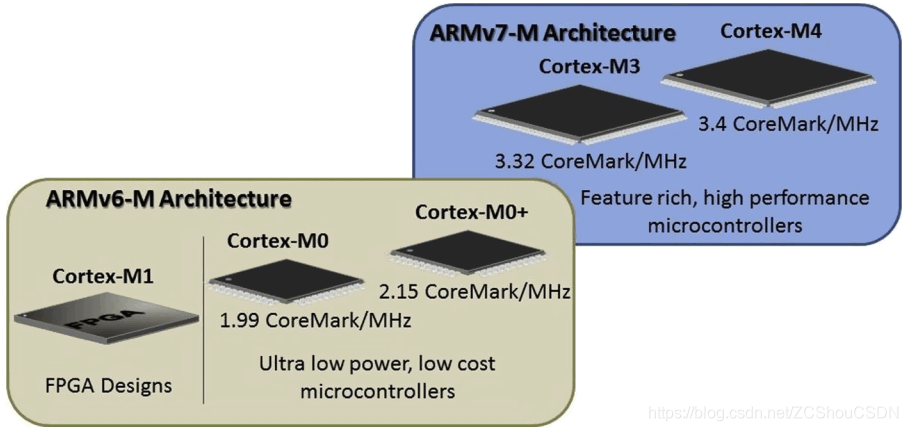

Cortex-M3 和 Cotex-M4 的 NVIC 最多支持 240 個 IRQ(中斷請求)、1 個不可屏蔽中斷(NMI)、1 個 Systick(滴答定時器)定時器中斷和多個系統異常。而 Cortex-M0 最多支持 32 個 IRQ、1 個不可屏蔽中斷(NMI)、1 個 Systick(滴答定時器)定時器中斷和多個系統異常。

注意,本文所說的 Cortex-M 主要指定是 Cotex-M3 和 Cotex-M4。

Cortex-M0、Cortex-M0+、Cortex-M1 基于 ARMv6-M。與 Cotex-M3 和 Cotex-M4 相比,他們的指令集較小。而且,Cortex-M1 是專門為FPGA 應用設計的,沒有獨立 MCU。

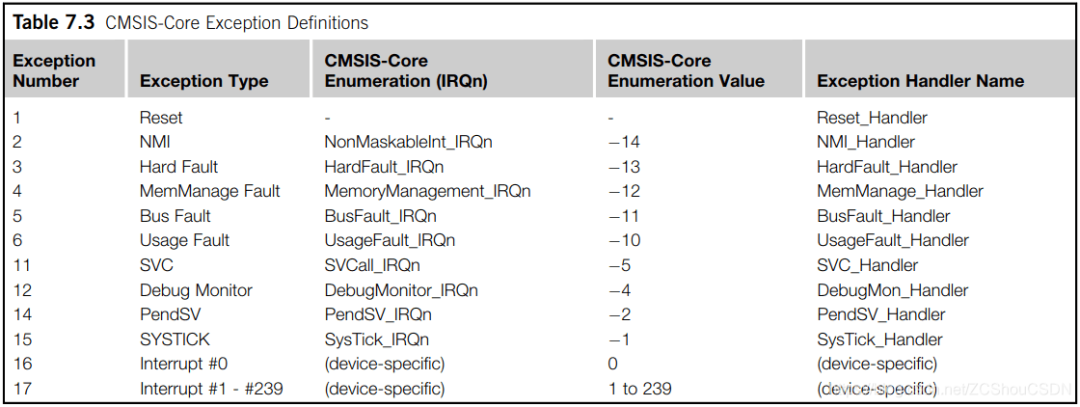

異常類型

Cortex-M 處理器的異常中,編號 1~15 的為系統異常,16 及以上的則為中斷輸入。所有中斷級別的異常都具有可編程的優先級。部分系統異常具有固定優先級。ARM 給出了以下一張表:

針對 Cortex-M 系列的內核,ARM 提供了一套叫做 CMSIS 的東西。目前,所有的 MCU 均使用 CMSIS 作為編程基礎。在 CMSIS-Core 中,中斷標識有中斷枚舉實現,從數值 0 開始(代表中斷 #0)。其中,系統異常的編號為負數。具體如下:

CMSIS-Core 之所以使用另外一種編號系統,是因為這樣可以稍微提高部分 API 的效率。中斷的編號和枚舉定義是同設備相關的,他們位于微控制器供應商提供的頭文件中,在一個名為 IRQn 的 typedef 段中。

中斷處理(異常處理)

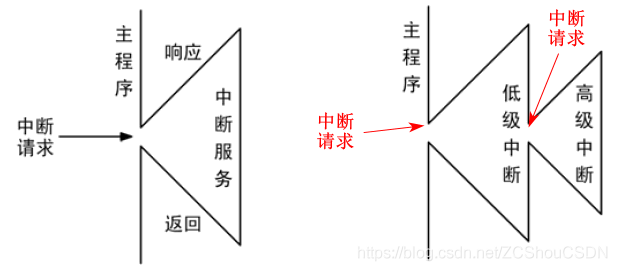

當某種內部或外部事件發生時,MCU 的中斷系統將迫使 CPU 暫停正在執行的程序,轉而去進行中斷事件的處理,中斷處理完畢后,又返回被中斷的程序處,繼續執行下去。

主程序正在執行,當遇到中斷請求(Interrupt Request)時,暫停主程序的執行轉而去執行中斷服務例程(Interrupt Service Routine,ISR),稱為響應,中斷服務例程執行完畢后返回到主程序斷點處并繼續執行主程序。多個中斷是可以進行嵌套的。正在執行的較低優先級中斷可以被較高優先級的中斷所打斷,在執行完高級中斷后返回到低級中斷里繼續執行。

中斷管理

管理中斷所使用的大部分寄存器都位于 NVIC(Nested Vectored Interrupt Controller,嵌套向量中斷控制器)和 SCB(System Control Block,系統控制塊)中。實際上,SCB 是作為 NVIC 的一部分來實現的,不過在 CMSIS-Core 中,將其定義在了獨立的結構體中。除此之外,處理器內核中還有用于中斷屏蔽寄存器:PRIMASK、FAULTMASK、BASEPRI。

NVIC 和 SCB 位于系統控制空間,地址從 0xE000E00 開始,大小 4KB。SCB 中還有 SysTick 定時器,存儲器保護單元等。

優先級

這部分暫且不說!

中斷輸入和掛起

在 Cortex-M 內核中,每個中斷都具有多個屬性:

-

每個中斷都可以被禁止(默認)或者使能

-

每個中斷都可以別掛起或者解除掛起

-

每個中斷都可以處于活躍或者非活躍

這些狀態屬性具有多種可能的組合。例如,在處理中斷時,可以將其禁止,若在中斷退出前產生了同一個中斷的新請求,由于該活躍中斷被禁止了,那就會處于掛起狀態。

NVIC 在設計上既支持產生 脈沖中斷請求 的外設,也支持產生 高電平中斷請求 的外設。無需配置任何一個 NVIC 寄存器以選擇其中一種中斷類型。對于脈沖中斷請求,脈沖寬度至少要為一個時鐘周期;而對于電平觸發的請求,在 ISR 中的操作清除請求之前,請求服務的外設要一直保持電平信號(如寫入寄存器以清除中斷請求) 。盡管外部中斷請求在 I/O 引腳上的電平可能是低電平有效,但是 NVIC 收到的請求信號為高有效!

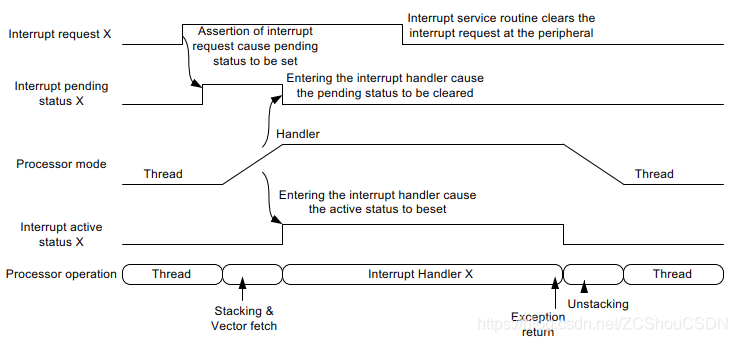

中斷的掛起狀態被存儲在 NVIC 的可編程寄存器中,當 NVIC 的中斷輸入被確認后,它就會引發該中斷的掛狀態。即便中斷請求被取消,掛起狀態仍會為高。這樣,NVIC 就可以處理脈沖中斷請求了。

掛起狀態的意思是,中斷被置于一種等待處理器處理的狀態。有些情況下,處理器在中斷掛起時就會進行處理。不過,若處理器已經在處理另外一個更高或同優先級的中斷,或者中斷被某個中斷屏蔽寄存器給屏蔽掉了,那么在其他的中斷處理結束前或者中斷屏蔽被清除前,掛起請求會一直保持。

在傳統 ARM 處理器中,如果外設產生了中斷,那么它們得到處理前必須一直保持中斷請求信號。

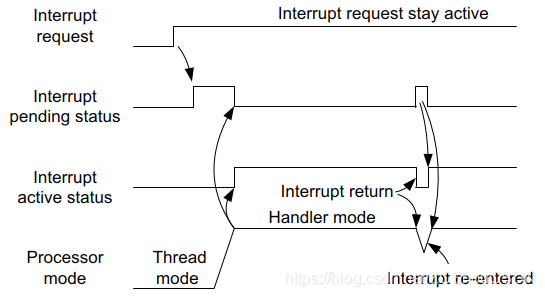

當中斷開始處理中斷請求時,中斷的請求信號會被自動清除。當中斷正在被處理時,它就會處于活躍狀態。

當中斷處于活躍狀態時,處理器無法再中斷完成和異常返回前再次處理同一個中斷請求。

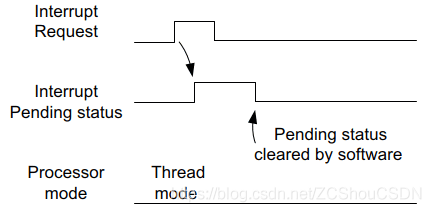

中斷的掛起狀態位于中斷掛起狀態寄存器中,軟件可以復位這些寄存器。因此,可以手動清除或者設置中斷的掛起狀態。若中斷請求產生時處理器正在處理另一個具有更高優先級的中斷,而在處理器對該中斷請求做出響應之前,掛起狀態被清除掉了,則該中斷會被取消且不會再得到處理。

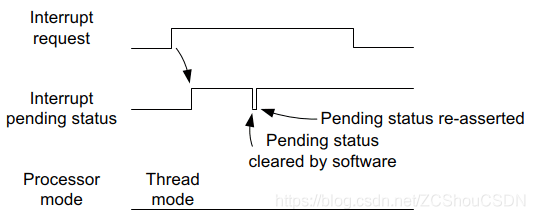

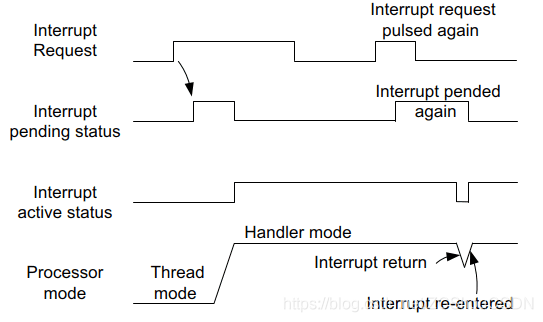

若持續保持某個中斷請求,那么及時軟件嘗試清除該掛起狀態,掛起狀態還是會再次被置位的。

若中斷已經得到了處理,中斷源仍然在繼續保持中斷請求,那么這個中斷就會再一次進入掛起狀態且再次得到處理

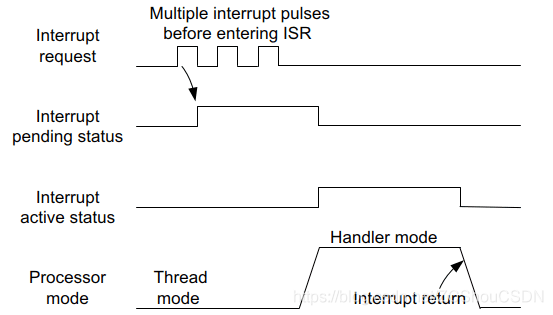

對于脈沖中斷請求,若在處理器開始處理前,中斷請求信號產生了多次,他們會被當做一次中斷請求處理

中斷掛起狀態可以在其正在被處理時再次置位。之前的中斷請求正在被處理時產生了新的請求,這樣機會引發新的掛起狀態。處理器在前一個 ISR 結束后需要再次處理這個中斷。

即使中斷被禁止了,他的掛起狀態仍然可置位。 這種情況下,若中斷稍后被使能了,它仍然可以被觸發并被得到處理。這種情況可能不是我們需要的,因此需要在使能 NVIC 中斷前手動清除掛起狀態。

總結

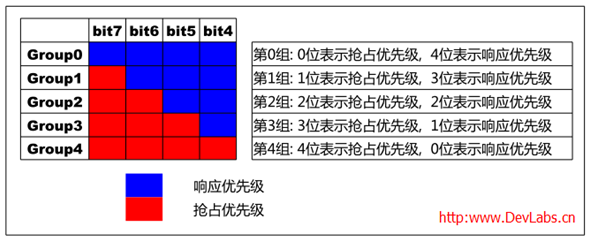

NVIC 中對于每個中斷需要設置 搶占優先級 和 響應優先級(又稱子優先級)。多個中斷會先比較 搶占優先級,搶占優先級相同的比較響應優先級。高搶占優先級能夠打斷低搶占優先級的,但是相同搶占優先級的高響應優先級不能打斷低響應優先級。

-

高優先級的搶占優先級是可以打斷正在進行的低搶占優先級中斷的。

-

搶占優先級相同的中斷,高響應優先級不可以打斷低響應優先級的中斷。

-

搶占優先級相同的中斷,當兩個中斷同時發生的情況下,哪個響應優先級高,哪個先執行。

-

如果兩個中斷的搶占優先級和響應優先級都是一樣的話,則看哪個中斷先發生就先執行。

參考

-

The Definitive Guide to ARM Cortex-M3 and Cortex-M4 Processors, 3rd Edition

-

The De?nitive Guide to the Cortex-M0

————————————————

版權聲明:本文為CSDN博主「ZC·Shou」的原創文章,遵循CC 4.0 BY-SA版權協議,轉載請附上原文出處鏈接及本聲明。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請聯系小編進行處理

審核編輯 黃宇-

微控制器

+關注

關注

48文章

7937瀏覽量

154342 -

mcu

+關注

關注

146文章

17938瀏覽量

363324 -

中斷

+關注

關注

5文章

905瀏覽量

42680 -

Cortex-M

+關注

關注

2文章

231瀏覽量

30320

評論

發布評論請先 登錄

Cortex-M 內核中斷/異常系統、中斷優先級/嵌套 詳解

Cortex-M 內核中斷/異常系統、中斷優先級/嵌套 詳解