最近客戶在使用i.MX RT1010的I2C作為從機設備與主機通訊,使用了時鐘延展的功能(clock stretching)。在開發過程中遇到了一些小煩惱和小細節,在此呢,也寫下一篇文檔予以總結。

什么是時鐘延展

首先,簡單介紹一下什么是時鐘延展。時鐘延展是指從機通過將SCL拉低以暫停數據傳輸的一個過程,在暫停過程中,從機可以有更多的時間處理接收到的數據,或者準備即將發送的數據。在相關的處理和準備完成之后,將交出SCL的控制權,主機繼續控制SCL的節奏進行數據的收發。換句話說,時鐘延展是從機跟不上主機的速度,讓老司機等等它,啊不,是讓主機等等它的操作。

時鐘延展通常分為兩種,一種是字節級(byte)的時鐘延展,一種是比特級(bit)的時鐘延展。字節級的時鐘延展是按照字節為單位開展,每一個字節收發結束之后啟動。比特級則是每個數據bit都進行延展,強行讓master慢下來。

在查閱相關資料的過程中發現,并不是所有的I2C從機設備都支持時鐘延展,例如I2C的傳感器,部分存儲設備;也并不是所有的主機設備也支持時鐘延展,例如使用IO口模擬實現的I2C或者是FPGA上實現的I2C。因此在使用之前,需要檢查器件自身是否支持時鐘延展。

四種時鐘延展功能

在我們i.MX RT1010上總共支持4種字節級的時鐘延展:

下面我們將對這四種時鐘延展的功能進行簡要介紹,以下介紹均為從機視角。

延展功能1:收完地址等一等

在從機接收完主機發送的地址信息后,且AVF 置位,則此時從機獲得SCL的控制權,開始持續拉低SCL開啟時鐘延展。那么什么時候結束呢,從硬件狀態機的角度看,當AVF bit被清除,時鐘延展結束,主機獲得SCL的控制權。

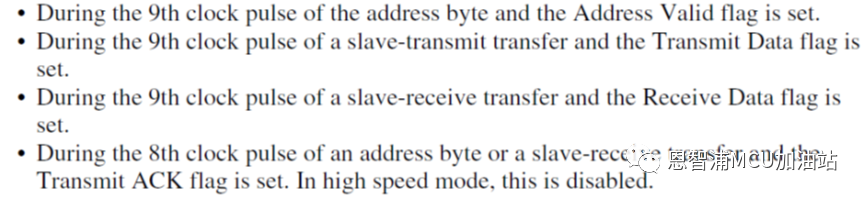

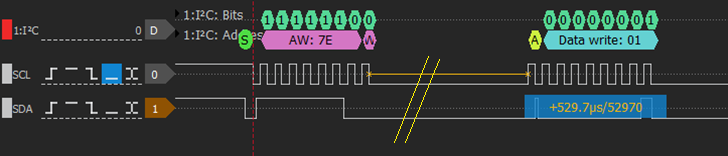

舉個例子,用我們SDK工程在接收到地址信息后強行延時500us再去清除AVF bit, 看看波形是怎樣的:

從圖中可以看到,兩次時鐘間隔約491us,基本上與500us的預期相匹配。并不是完美的500us的原因是,延時函數沒有使用定時器精確延時。

延展功能2:發送之前等一等

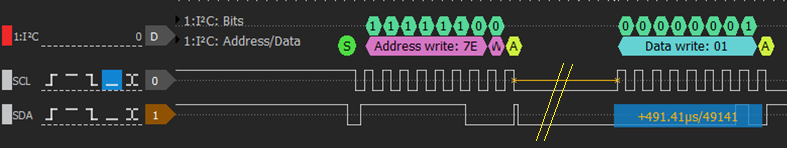

在從機接收到主機的地址信息和讀指令后,TDF將會置位,則此時從機獲得SCL的控制權。同樣是在清除TDF bit之后,主機再次獲得SCL的控制權。在這個過程中,從機可以根據主機發送的信息,把要發送的數據準備好,再釋放SCL的控制權。同樣舉個例子,再清除TDF bit 之前等一等,這次等的長一點800us。

延展功能3:接收之前等一等

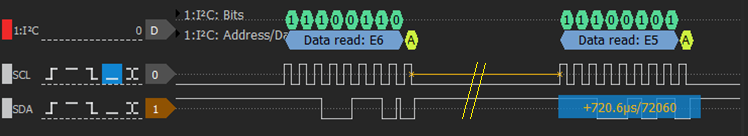

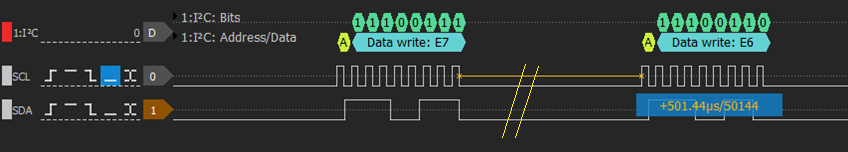

在從機接收到數據之后,RDF會置位,此時從機會獲得SCL的控制權。同樣是在清除TDF bit之后,主機再次獲得SCL的控制權。拉個波形看看,在清標志位前拉個1000us的延時,波形如下圖所示。

延展功能4:手動回ACK

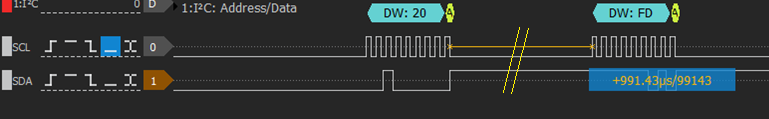

這里是指,當主機把數據(地址信息或者數據信息)發送給從機后,在傳送完第八個bit(或者說是第八個時鐘)之后,從機即獲得了SCL的控制權限,在此時需要手動向STAR寄存器中最后一位寫0或者1,以向主機反饋ACK 或者NACK。在寫0之前,我們增加一個500us的延時,地址信息的波形見下圖,可以看到第八個和第九個CLK時鐘的間隔被拉長。

從機接收數據的信息見下圖,同樣可以看到,第八個和第九個的時鐘被拉長了。

時鐘延展的時序要求

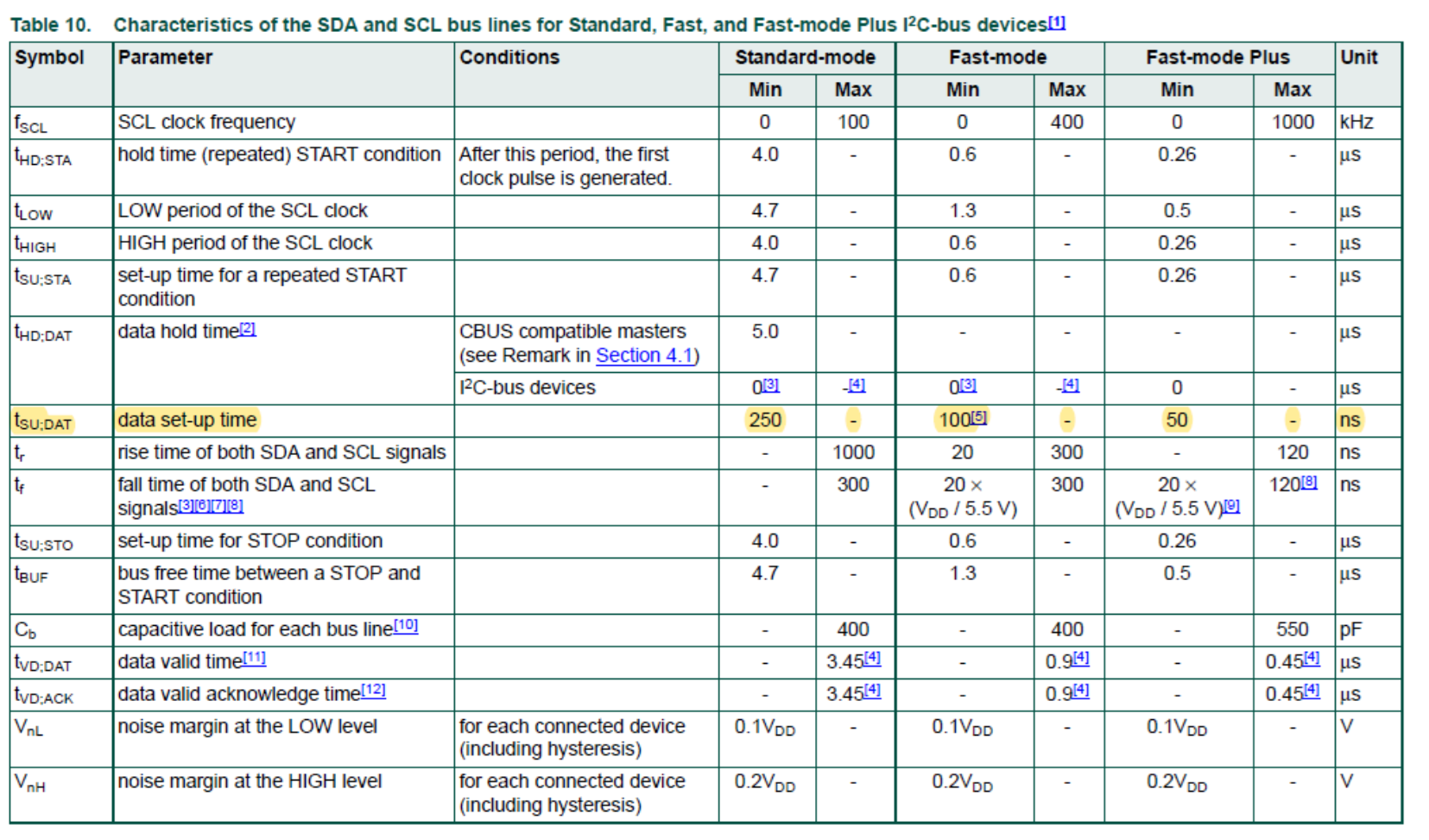

在使用時鐘延展的功能后,同樣不能忽略的一個要點是要滿足I2C的AC timing,即數據的建立時間和保持時間。對于不同的工作速度,I2C對于這兩個參數的時間要求也是不同的,下圖為I2C的規范上的截圖。

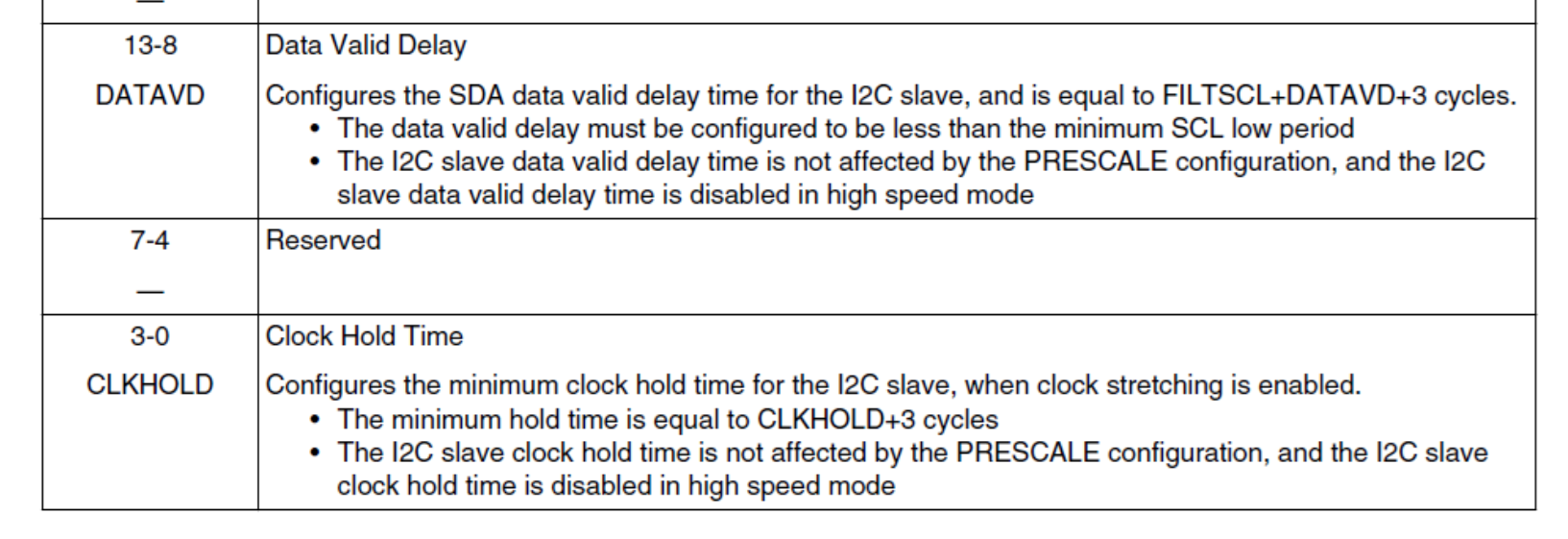

對于i.MX RT1010來說,我們在開啟時鐘延展功能后需要對下面的兩個參數進行設置,以滿足I2C的timing要求。

CLKHOLD: I2C的數據的建立時間,需要根據不同的通訊速度進行設置。

DATAVD: I2C的數據保持時間,通常來看保持為0即可。

如果不能正確設置CLKHOLD的時間會怎樣呢?

造成時序混亂,當SCL的驅動能力較強,且SDA的負載較重的時候,甚至會引起SCL上升的比SDA速度快,那么想一下I2C的停止條件,當SCL處于高電平時,SDA拉高。那么就會讓總線停止傳輸,除此以外,可能還會有其他的未知問題發生。

其次,關于CLKHOLD時間的計算,目前的驅動程序是有些小問題的。因此建議徒手擼寄存器,自己把想要的數值填寫到CLKHOLD寄存器內。對于具體的時間,計算公式如下:

t =(CLKHOLD + 3) * Tclk

這里的Tclk是指I2C的functional clock的周期。因此,真正的建立時間,是CLKHOLD的數值和I2C 的輸入時鐘頻率共同作用的結果。

哦對了,如何使能時鐘延展功能?

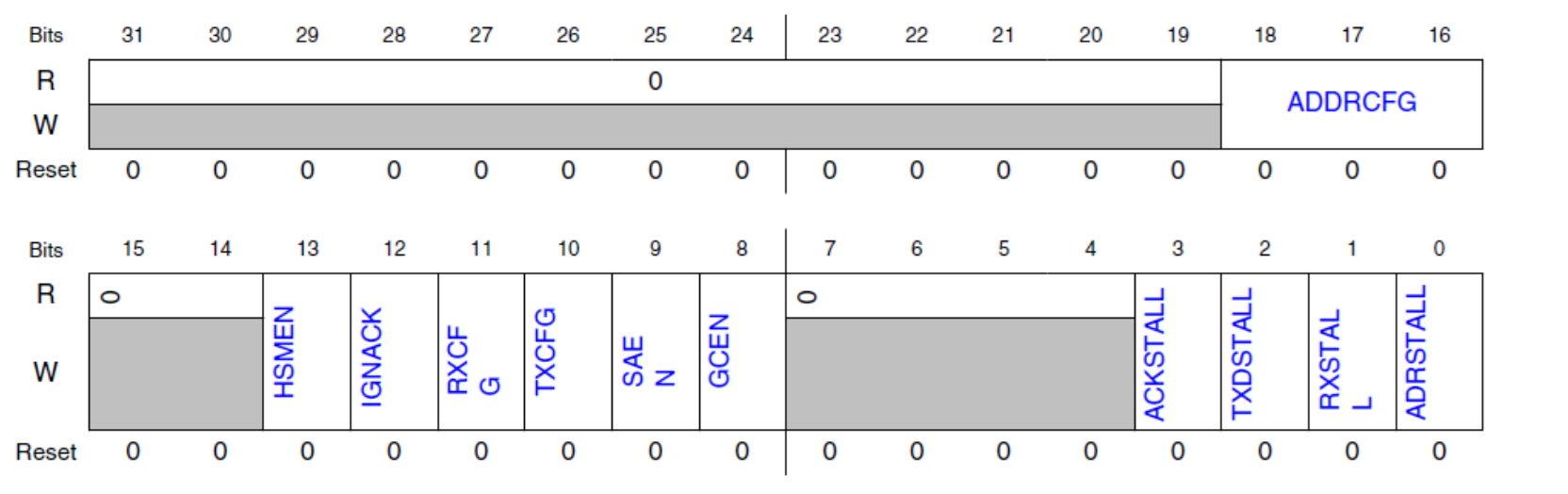

如果你喜歡寄存器操作,那么可以在SCFGR1寄存器中的bit[3:0]直接開啟對應的功能:

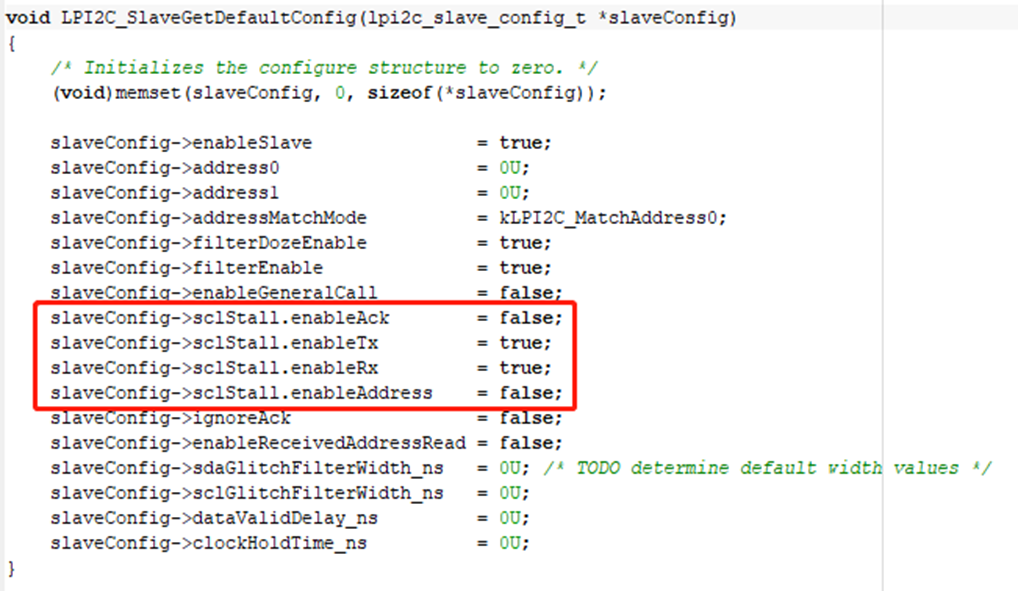

如果你習慣SDK操作,那么在這個結構體里把對應的功能寫true吧:

來源:恩智浦MCU加油站

審核編輯:湯梓紅

-

FPGA

+關注

關注

1643文章

21982瀏覽量

614561 -

時鐘

+關注

關注

11文章

1886瀏覽量

132889 -

I2C

+關注

關注

28文章

1537瀏覽量

127137 -

SCL

+關注

關注

1文章

243瀏覽量

17480

發布評論請先 登錄

基于FPGA的I2C SLAVE模式總線的設計方案

i.MX RT1xxx 系列的時鐘系統以及相關功能引腳

01:i.MX RT的市場應用和參考解決方案

恩智浦i.MX RT1170開創GHz MCU時代

恩智浦i.MX RT1170在將該系列帶上了更高的層面

i.MX RT開發筆記-08 | i.MX RT1062嵌套中斷向量控制器NVIC(按鍵中斷檢測)

RT-Thread & NXP 發布 i.MX RT 系列 BSP 新框架

STM32F103硬件I2C Slave

Gowin I2C Master/Slave用戶指南

i.MX RT1010的I2C Slave時鐘延展功能小記

i.MX RT1010的I2C Slave時鐘延展功能小記

評論