隨著領(lǐng)先的芯片制造商繼續(xù)將finFET以及很快的納米片晶體管縮小到越來越小的間距,使用銅及其襯墊和阻擋金屬,較小的金屬線將變得難以維持。接下來會(huì)發(fā)生什么以及何時(shí)發(fā)生,仍有待確定。

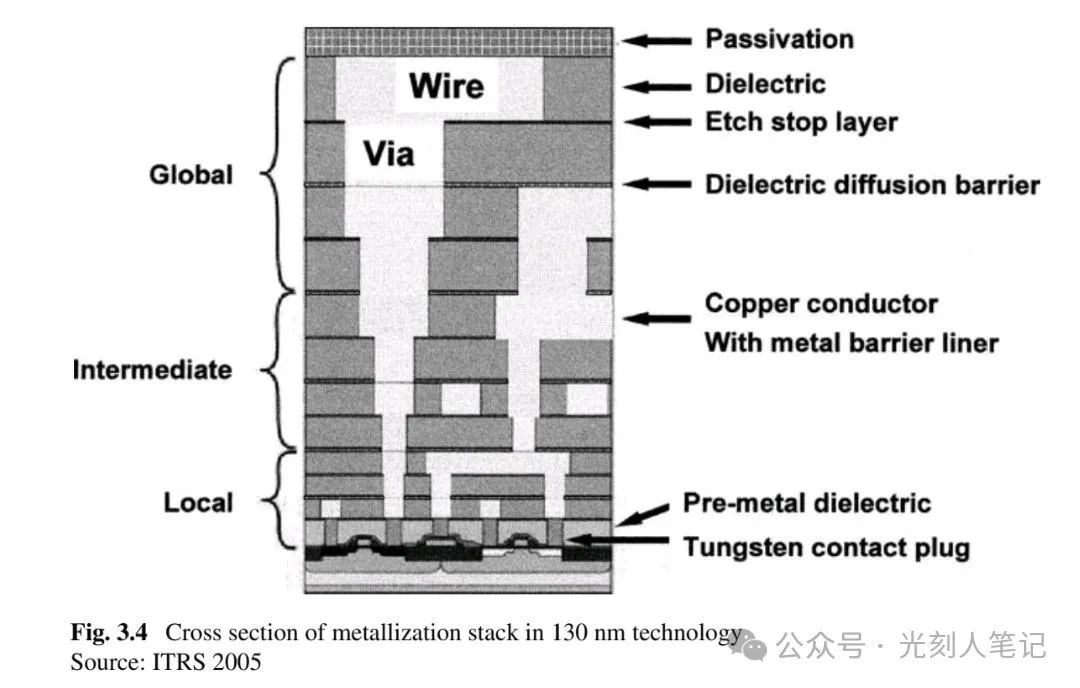

自從IBM在20世紀(jì)90年代向業(yè)界引入采用雙鑲嵌工藝的銅互連以來,半導(dǎo)體行業(yè)一直在利用銅的高導(dǎo)電性、低電阻率和可靠互連的優(yōu)勢(shì)。但隨著電阻和電容的增加,RC延遲將繼續(xù)顯著影響器件性能。

與此同時(shí),系統(tǒng)性能驅(qū)動(dòng)因素使得在可能的情況下將存儲(chǔ)設(shè)備移至生產(chǎn)線后端變得有吸引力。如果業(yè)界開始引入具有較低熱預(yù)算的互連工藝,那么存儲(chǔ)器或其他設(shè)備集成之類的事情就變得可行。但首先,必須解決延伸銅線和引入背面配電方案的直接工程挑戰(zhàn)。

銅的里程更長

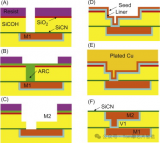

在2nm邏輯節(jié)點(diǎn),銅線和通孔正在通過創(chuàng)造性的方式延伸。一些吸引力的選擇包括限制阻擋層和襯墊材料的電阻率影響,要么通過使這些薄膜更薄——從化學(xué)氣相沉積(CVD)到原子層沉積(ALD)——要么消除它們,例如沿著通孔和線路之間的垂直路徑。

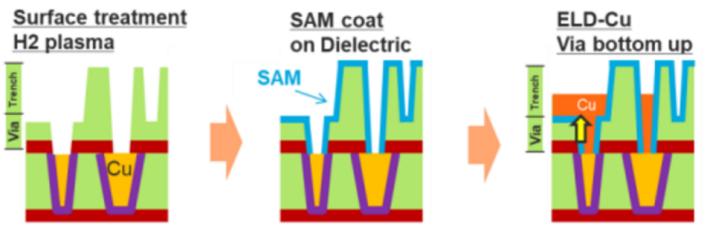

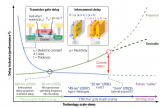

圖1

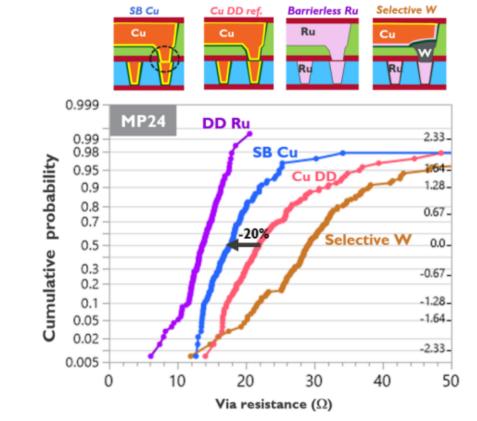

圖2

英思特測(cè)試了預(yù)通孔填充工藝,該工藝在銅填充下不使用阻擋層(TaN),而是在無電沉積(ELD)后進(jìn)行沉積。微小過孔是互連鏈中的薄弱環(huán)節(jié)(圖2),關(guān)鍵工藝步驟是在對(duì)通孔底部暴露的銅進(jìn)行原位界面工程之后,僅在電介質(zhì)上進(jìn)行選擇性ALD TaN阻擋層沉積,通過消除勢(shì)壘,通孔電阻可降低20%。在較小的尺寸下,減少量會(huì)更大。

連接背面電源

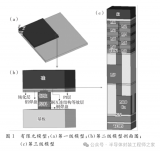

背面供電(BPD)是一種從晶圓背面向晶體管供電的創(chuàng)新方法,從而釋放正面互連以僅傳輸信號(hào)。這緩解了擁塞,利用晶圓背面進(jìn)行配電,可以有效增加芯片的功能面積,而無需增加其占地面積。

背面電源集成的較大挑戰(zhàn)之一是如何以電氣方式連接晶圓正面和背面。較具挑戰(zhàn)性的方案涉及到源外延的直接背面接觸。通孔將很小且縱橫比很高,還需要與外延層進(jìn)行低電阻接觸,就像正面的源極/漏極接觸一樣。因此,鎢填充物或可能是鉬將是可能的選擇。

結(jié)論

如今,雙鑲嵌銅的間距已擴(kuò)展到20納米,但涉及釕或其他替代金屬的減材方案即將發(fā)生根本性變化。就電阻率而言,隨著尺寸降至17 x 17nm以下,釕變得有吸引力。公司可以使用無障礙通孔底部來獲得額外收益,同時(shí)為偉大的轉(zhuǎn)型做好準(zhǔn)備。

審核編輯 黃宇

-

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28871瀏覽量

237285 -

晶圓

+關(guān)注

關(guān)注

53文章

5154瀏覽量

129731 -

晶體管

+關(guān)注

關(guān)注

77文章

10015瀏覽量

141542

發(fā)布評(píng)論請(qǐng)先 登錄

銅對(duì)芯片制造中的重要作用

從微米到納米,銅-銅混合鍵合重塑3D封裝技術(shù)格局

一文詳解銅互連工藝

與樹莓派的“黃金”關(guān)系,是如何幫助這家醫(yī)療設(shè)備公司擴(kuò)大規(guī)模?

背接觸(BC)太陽能電池組件封裝損失研究:從材料選擇到工藝優(yōu)化

探究絲網(wǎng)印刷的導(dǎo)電銅漿在PERC太陽能電池上的性能和可靠性

規(guī)模化印刷銅電子越來越接近現(xiàn)實(shí)

SK海力士被曝贏得博通 HBM 訂單,預(yù)計(jì)明年 1b DRAM 產(chǎn)能將擴(kuò)大到 16~17 萬片

研究透視:芯片-互連材料

TS3DV520E的傳輸距離可以擴(kuò)大嗎?

銅互連雙大馬士革工藝的步驟

優(yōu)化銅互連結(jié)構(gòu)的熱應(yīng)力分析與介電材料選擇

研究銅互連的規(guī)模能擴(kuò)大到什么程度

研究銅互連的規(guī)模能擴(kuò)大到什么程度

評(píng)論