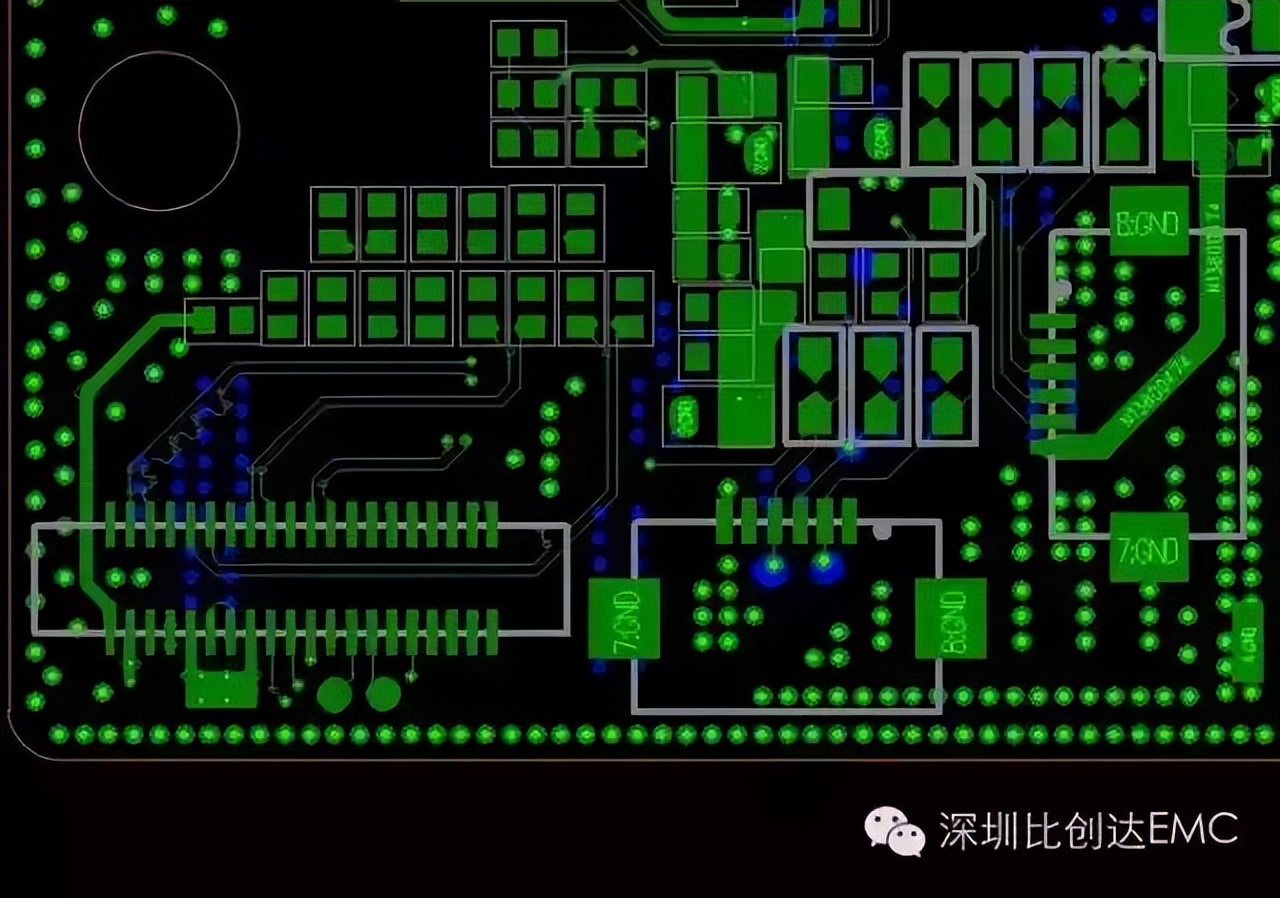

PCB布線是ESD防護的一個關鍵要素,合理的PCB設計可以減少故障檢查和返工所帶來不必要的成本。在PCB設計中,不但需要在靜電薄弱電路增加靜電抑制器件,還要克服放電電流產生的電磁干擾(EMI)電磁場效應。

本文重點提供可優化的ESD防護的PCB設計準則。那么PCB設計ESD抑制準則?接下來就跟著深圳比創達EMC小編一起來看下吧!

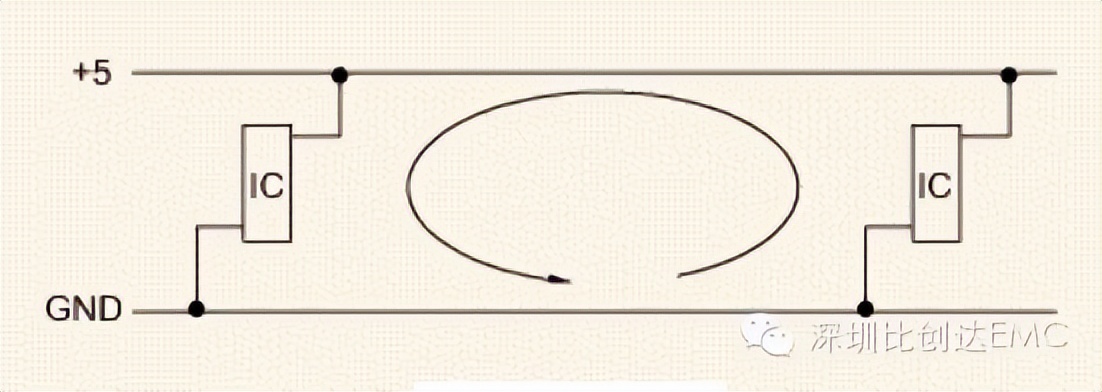

一、電路環路

電流通過感應進入到電路環路,這些環路是封閉的,并具有變化的磁通量。電流的幅度與環的面積成正比。較大的環路包含較強的磁通量,因此在電路中產生較強的磁通量。因此必須減少環路面積。如圖:

常見環路如上圖所示,由電源和地線所形成的。在可能的條件下,可以采用具有電源和接地層的多層PCB設計。多層電路板不僅將電源和接地之間的回路面積減到最小,也減小了ESD脈沖產生的高頻電磁場。

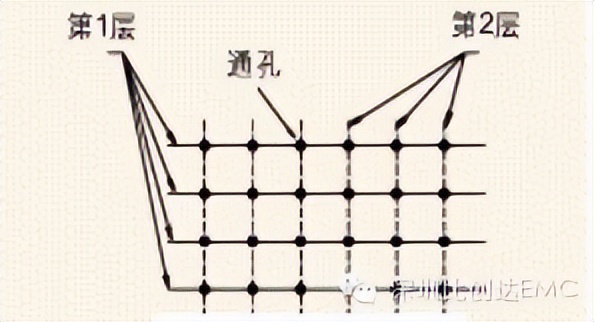

如果不能采用多層電路板設計,那么用于電源線和接地線可以做成如下圖所示的網格狀。

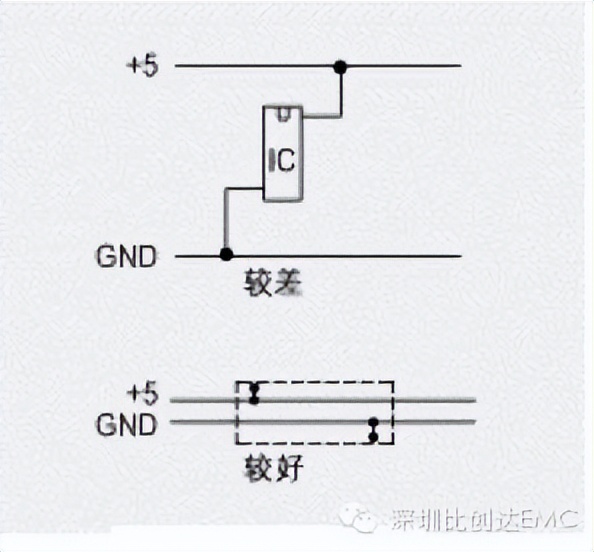

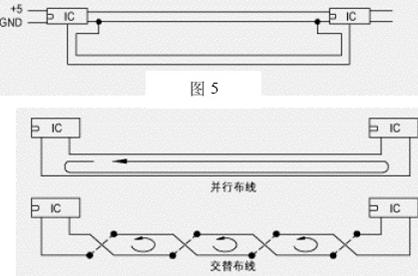

網絡連接可以起到電源和接地層的作用,用過孔連接各層的抑制線,且在每個方向上過孔連接間隔應該在6里面以內。另外,在布線時將電源和接地印制線盡可能靠近過也可以降低環路面積,如下圖所示:

綜上所述,相信通過本文的描述,各位對PCB設計ESD抑制準則都有一定了解了吧,有疑問和有不懂的想了解可以隨時咨詢深圳比創達這邊。今天就先說到這,下次給各位講解些別的內容,咱們下回見啦!也可以關注我司wx公眾平臺:深圳比創達EMC!

以上就是深圳市比創達電子科技有限公司小編給您們介紹的PCB設計ESD抑制準則的內容,希望大家看后有所幫助!

深圳市比創達電子科技有限公司成立于2012年,總部位于深圳市龍崗區,成立至今一直專注于EMC電磁兼容領域,致力于為客戶提供最高效最專業的EMC一站式解決方案,業務范圍覆蓋EMC元件的研發、生產、銷售及EMC設計和整改。

審核編輯:湯梓紅

-

ESD

+關注

關注

50文章

2282瀏覽量

175611 -

PCB設計

+關注

關注

396文章

4795瀏覽量

90150 -

emc

+關注

關注

172文章

4154瀏覽量

186721

發布評論請先 登錄

PCB設計中ESD抑制準則

【轉載】PCB設計中ESD抑制準則

PCB設計的ESD注意事項

PCB設計的ESD抑止準則

ESD防護的PCB設計準則

PCB設計中ESD抑制準則

PCB設計ESD抑制準則?

PCB設計ESD抑制準則?

評論