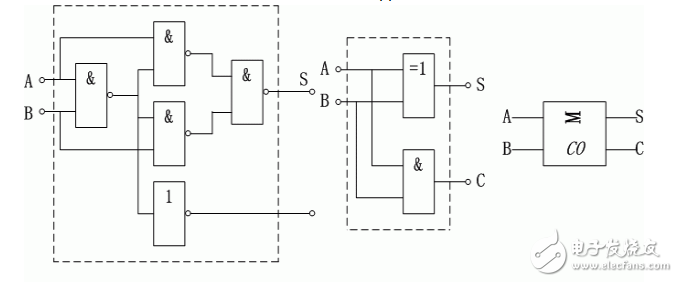

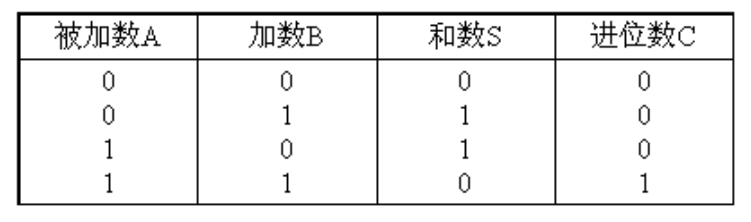

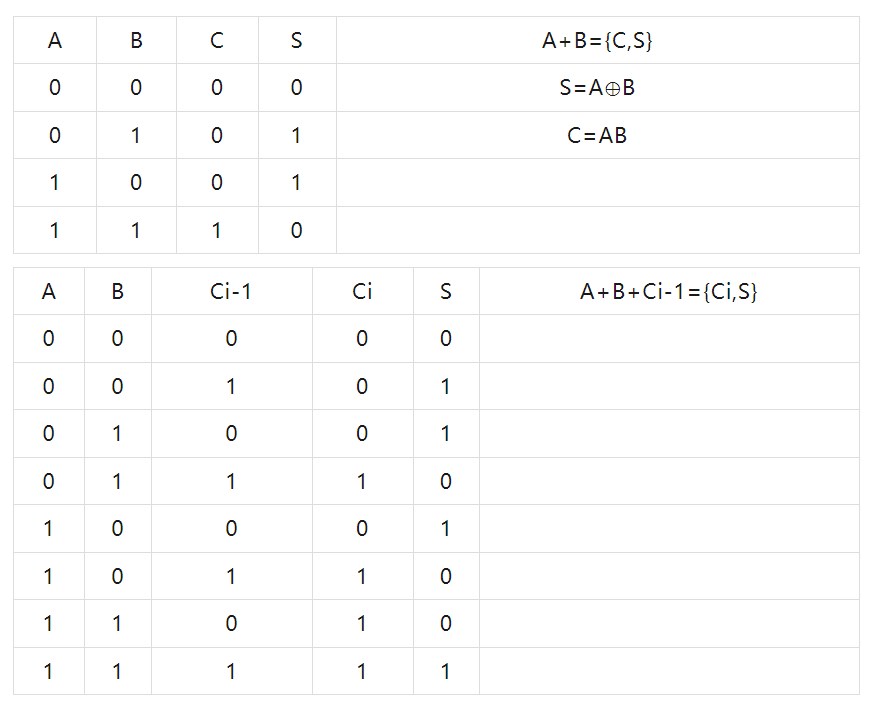

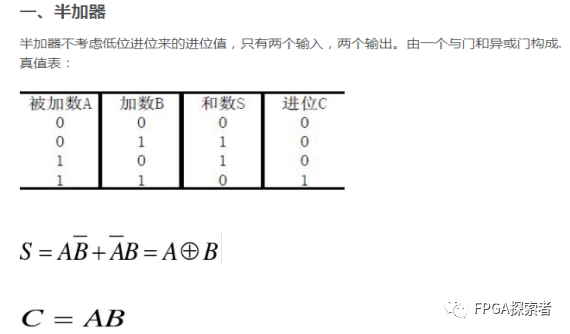

2.1半加器

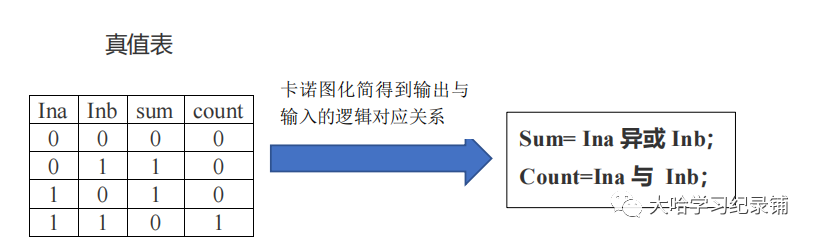

2.1.1原理推導得到邏輯關系

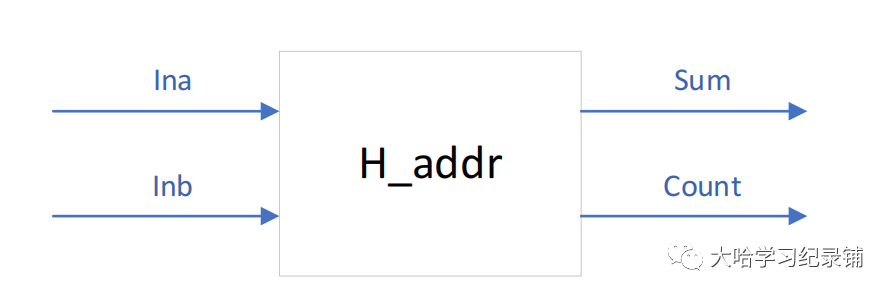

2.1.2 端口定義

做任何模塊前,要確定輸入輸出端口有哪些,有一個整體的概念;方便以后模塊調用;

2.1.3 源代碼(附 test 文件)

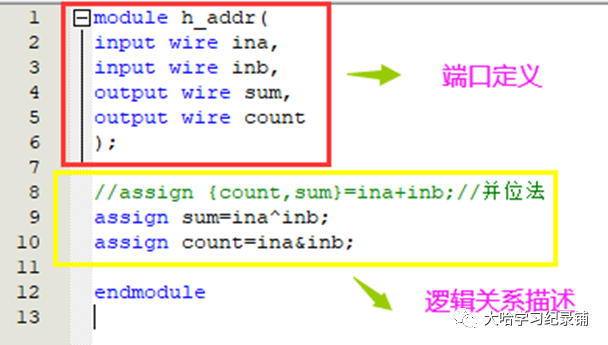

源文件

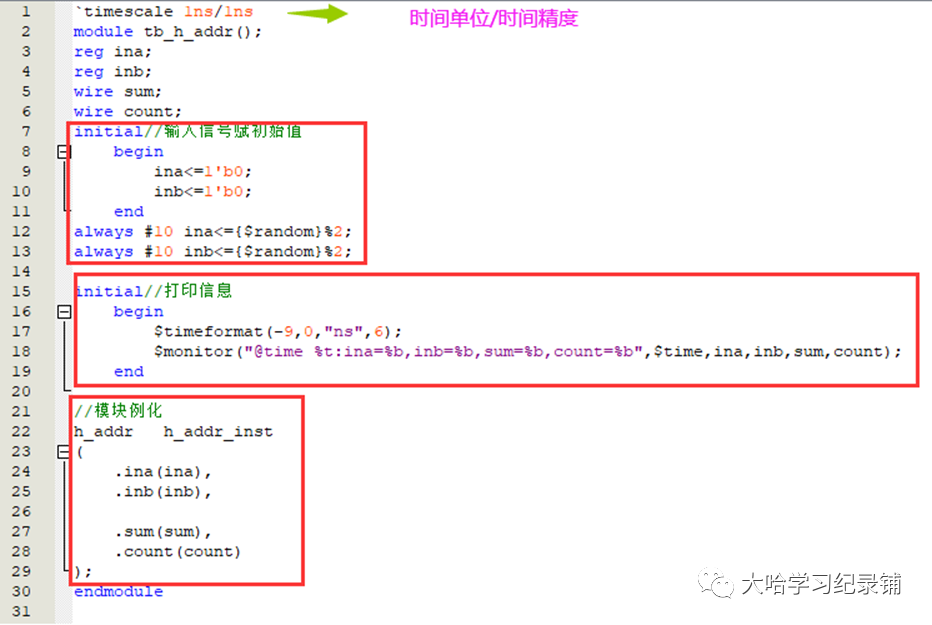

測試文件

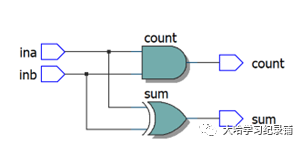

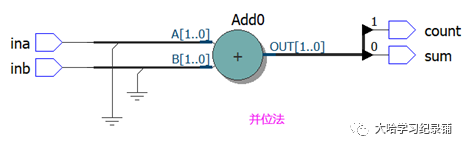

2.1.4RTL試圖(兩種)

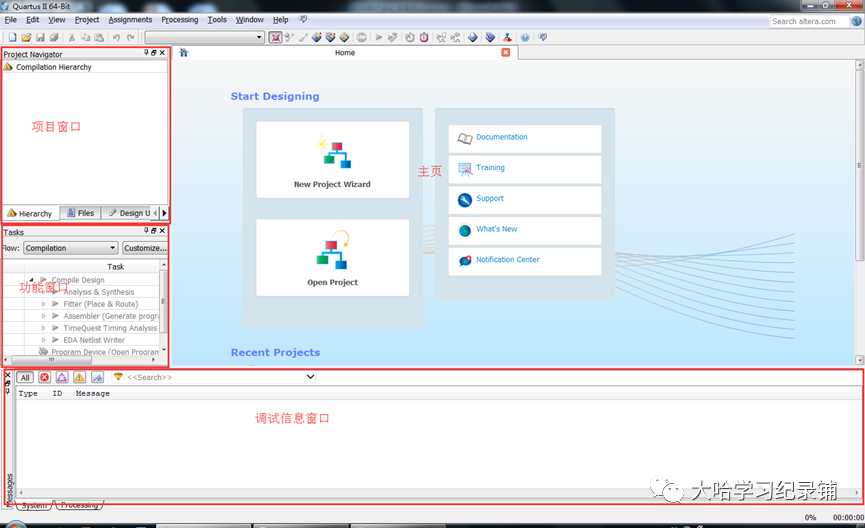

2.2實操(quartus13.1與modelsim_alter的操作,主要是每次重新撿起來的時候,都要重新看一遍,所示匯總一次)

2.2.1工程建立

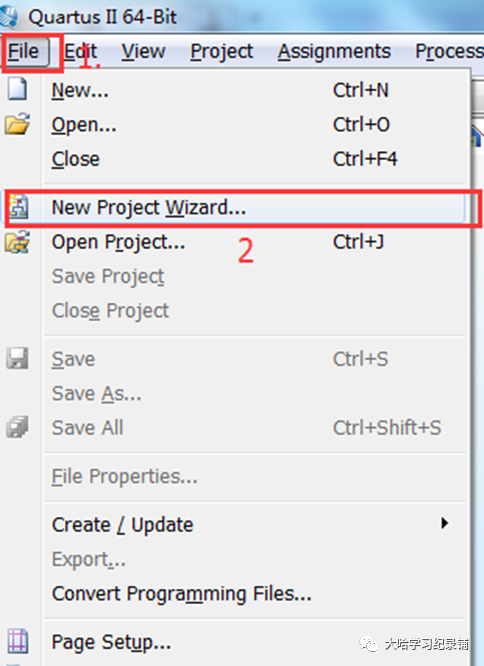

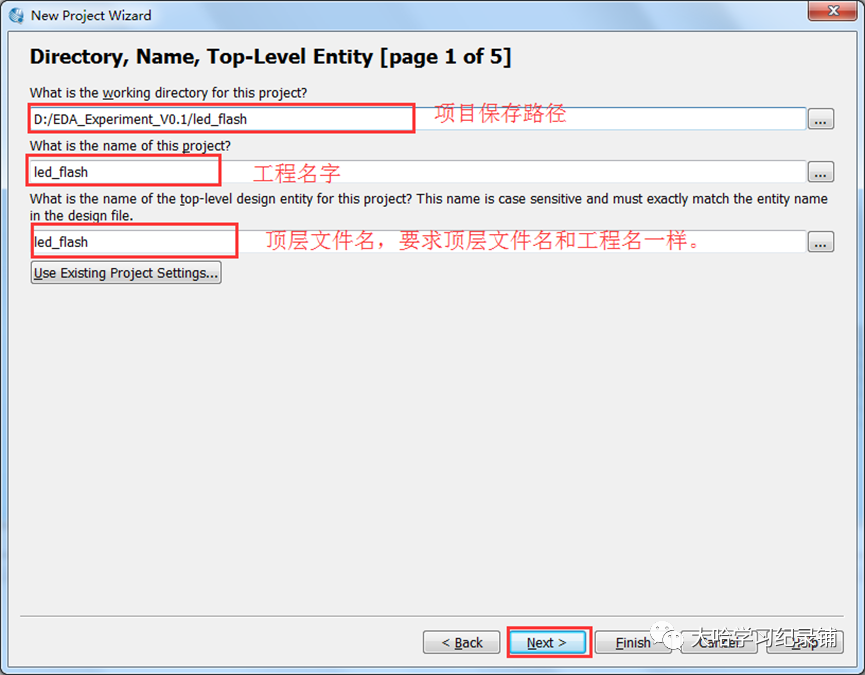

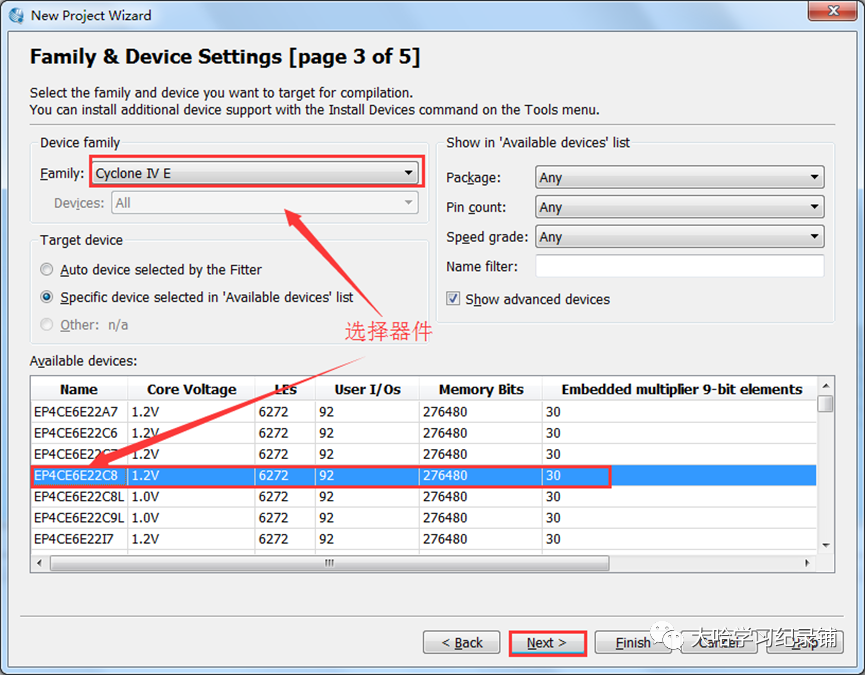

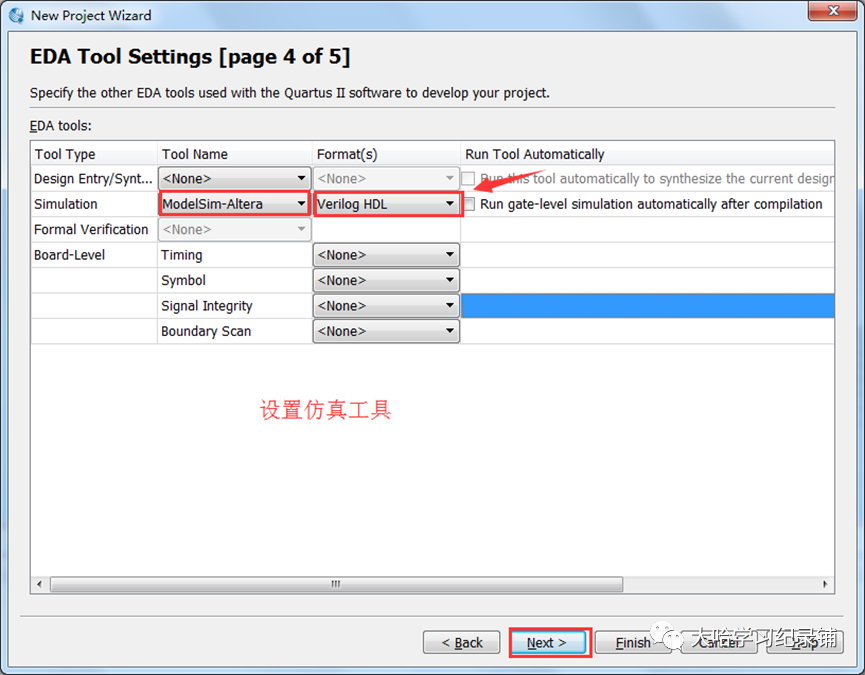

點擊左上角的File---->New Project Wizard如下圖所示

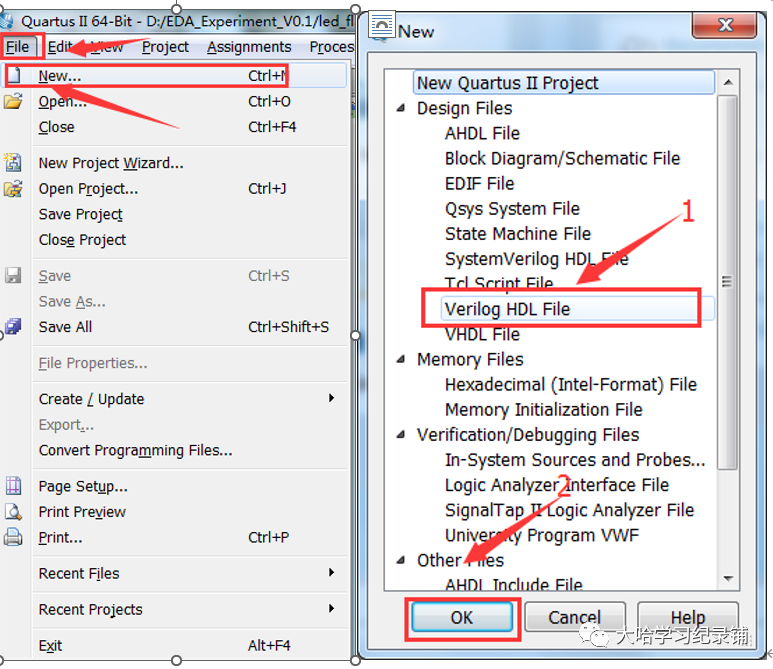

至此完成了工程的創建。下面我們就來創建工程頂層文件,我們可以點擊菜單欄的 File?New…,然后彈出如圖所示的新建文件窗口, 在這里我們可以選擇各種需要的設計文件格式。可以作為工程頂層設計文件的格式主要在 Design Files 類別下,我們選擇 Verilog HDL File并單擊OK 完成文件創建。在主編輯窗口中, 出現了一個新建的空白的可編輯文件, 我們接著在該文件中輸入實現實驗功能的一段 Verilog 代碼,并保存文件名為h_addr.v

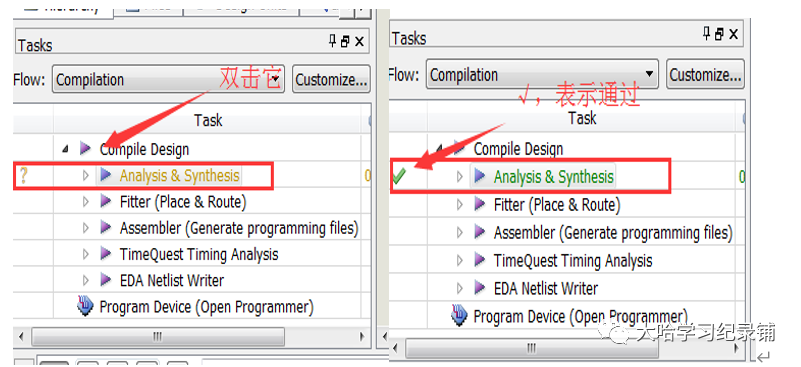

自此, 我們的工程創建和設計輸入工作已經完成。但是為了驗證一下設計輸入的代碼的基本語法是否正確,可以點擊 Flow→Compilation 下的 Analysis & Elaboration 按鈕,如圖所示。同時我們可以輸出打印窗口的 Processing 里的信息,包括各種 warning 和 Error。

Error是不得不關注的,因為 Error 意味著我們的代碼有語法錯誤,后續的編譯將無法繼續;而warning 則不一定是致命的,但很多時候 warning 中暗藏玄機,很多潛在的問題都可以從這些條目中尋找到蛛絲馬跡。當然了,也并不是說一個設計編譯下來就不可以有 warning,如果能夠確認這些 warning 符合我們的設計要求,那么可以忽略它。

最后,在 Analysis & Elaboration 完成后,通常前面的問號會變成勾號,表示通過。

2.2.2仿真文件

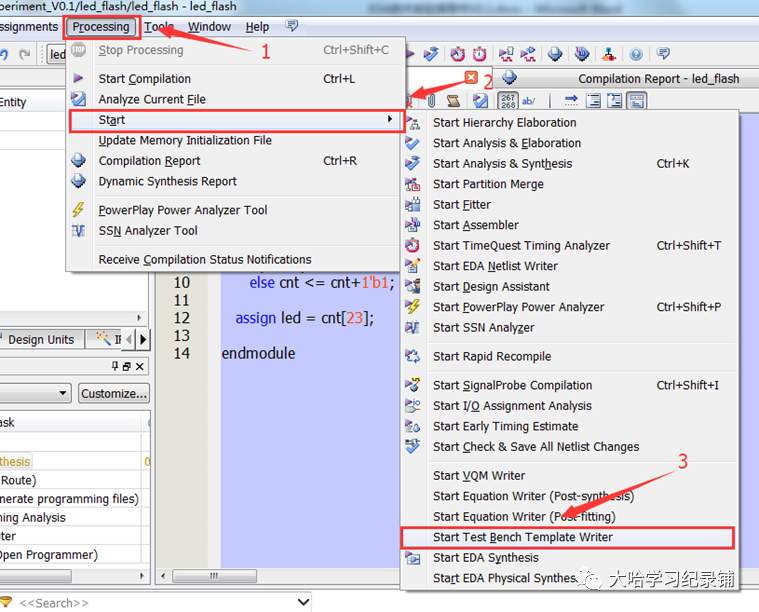

完成了前面基本的設計輸入后, 為了進一步的驗證代碼所實現功能的正確性, 我們還需要進行仿真測試。首先我們可以點擊菜單欄的Processing→Start→Start Test Bench Template Writer,隨后彈出提示“Test Bench TemplateWriter was successful“,那么我們就已經創建了一個 Verilog測試腳本,在此腳本中,我們可以設計一些測試激勵輸入并且觀察相應輸出, 借此我們就能夠驗證原工程的設計代碼是否符合要求。

我們打開工程路徑下的/simulation/modelsim 文件夾,可以看到一個名為led_flash.vt 的測試腳本文件創建了。

我們可以在 Quartus II 中打開這個文件,并且將其重新編輯(見2.1.3測試文本撰寫)

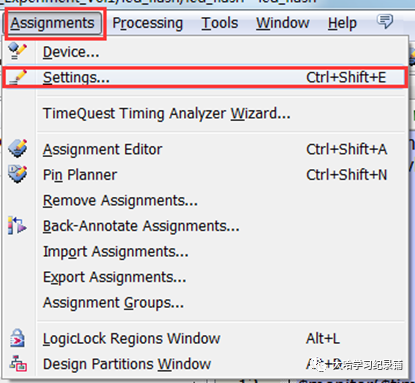

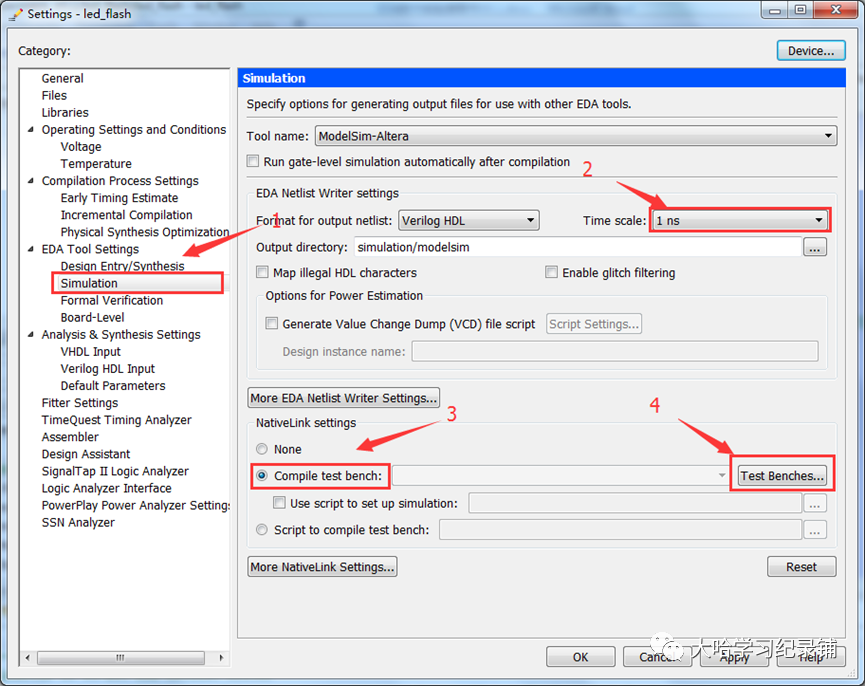

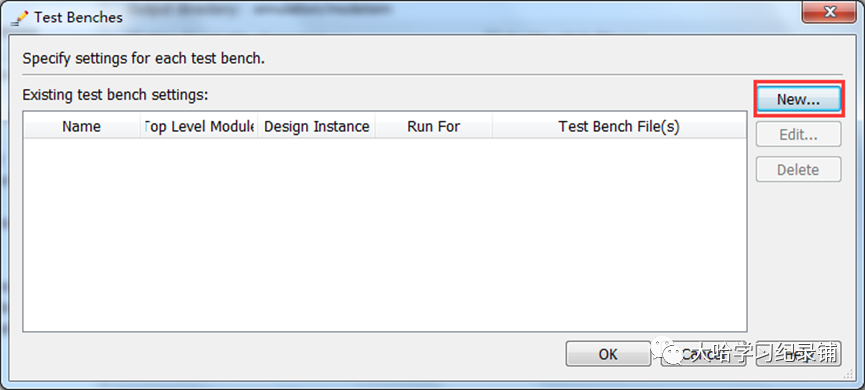

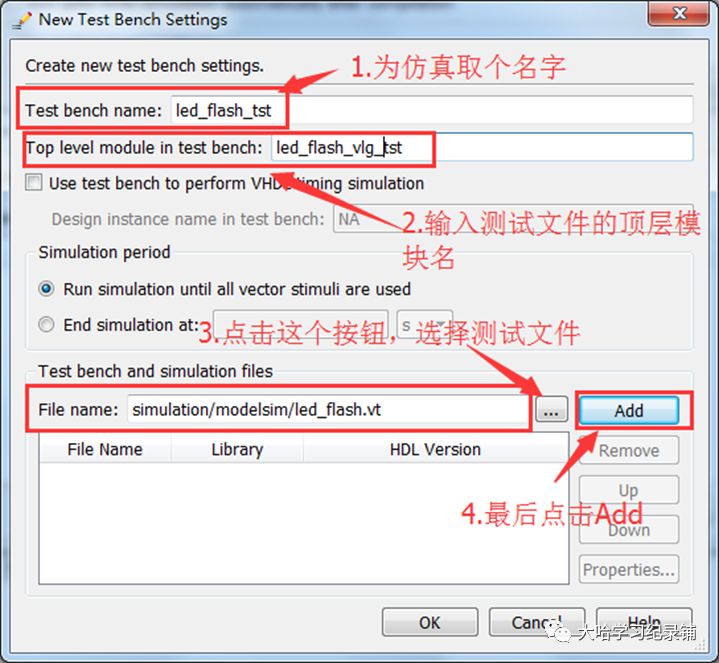

完成測試腳本編寫,我們接著需要打開菜單欄的 Assigement→Settings 選項,選擇Category?EDA Tool Setting→Simulation,在右邊的相關屬性中做如圖所示的設置,在選中Comple test bench 后,我們要點擊后面的 Test Benches…按鈕去選擇剛才創建的測試腳本。

回到 Setting 中也點擊 OK 完成所有相關設置。我們還需要打開菜單欄的 Tools→Options配置頁面,我們選擇 Category 下的 General→EDA Tool Options,然后設置 ModelSim-Altera軟件安裝路徑(請根據實際安裝時的路徑進行設置) 。

當 Quartus II 調用 ModelSim-Altera 軟件進行仿真時,會通過這里所設置的路徑來查找并啟動ModelSim-Altera。

在仿真測試前,我們還需要對工程進行一次編譯。點擊 Flow→Compilation 下的 Analysis & Elaboration 按鈕。

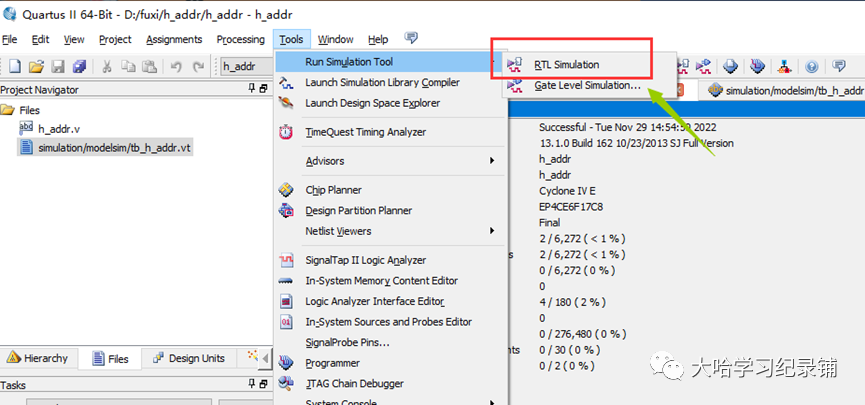

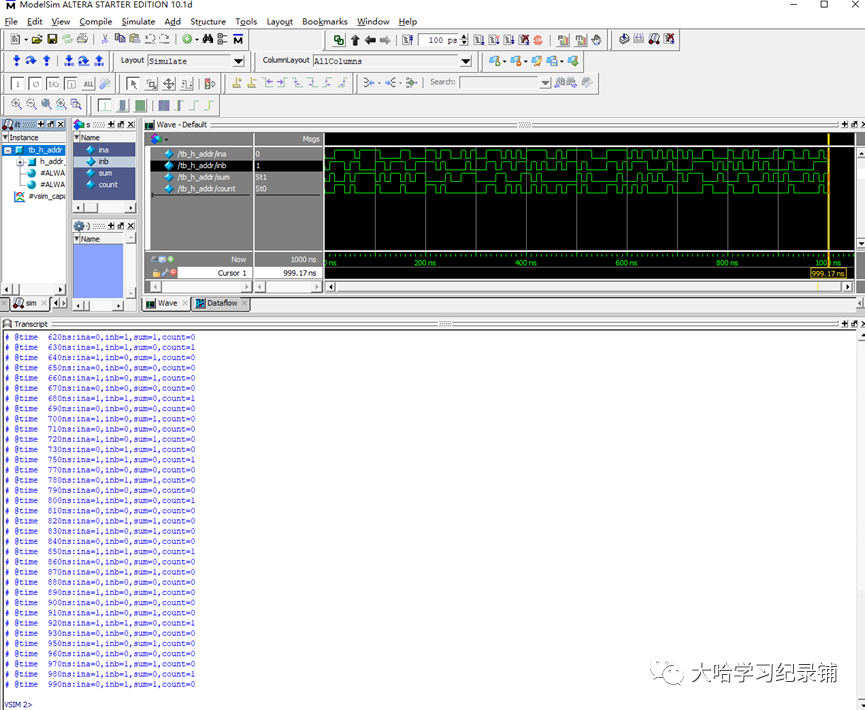

仿真測試的所有準備工作就緒了,下面我們就可以一鍵完成仿真工作。點擊菜單欄的Tools→Run Simulation Tool→RTL Simulation。隨后 ModelSim-Altera 便啟動,如圖所示,這ModelSim-Altera 軟件的工作界面。

3.最終仿真結果以及打印信息

-

EDA工具

+關注

關注

4文章

272瀏覽量

32607 -

仿真器

+關注

關注

14文章

1034瀏覽量

84993 -

RTL

+關注

關注

1文章

388瀏覽量

60696 -

半加器

+關注

關注

1文章

29瀏覽量

8914 -

Verilog設計

+關注

關注

0文章

20瀏覽量

6614

發布評論請先 登錄

單相半橋逆變器仿真技巧資料下載

一種分布式半實物仿真測試前端系統的研究

全加器是什么?全加器和半加器的區別?

仿真測試1:半加器

仿真測試1:半加器

評論