一、實(shí)驗(yàn)?zāi)康?/strong>

1、學(xué)習(xí)用集成觸發(fā)器構(gòu)成計(jì)數(shù)器的方法

2、掌握中規(guī)模集成計(jì)數(shù)器的使用及功能測試方法

3、運(yùn)用集成計(jì)數(shù)計(jì)構(gòu)成1/N分頻器

二、實(shí)驗(yàn)原理

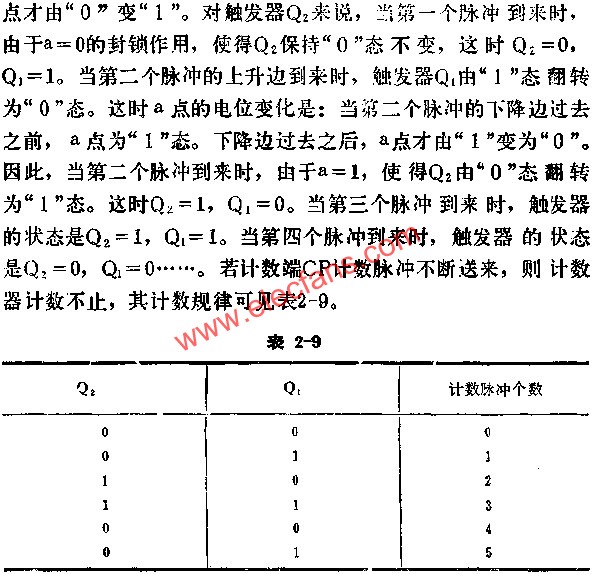

計(jì)數(shù)器是一個(gè)用以實(shí)現(xiàn)計(jì)數(shù)功能的時(shí)序部件,它不僅可用來計(jì)脈沖數(shù),還常用作數(shù)字系統(tǒng)的定時(shí)、分頻和執(zhí)行數(shù)字運(yùn)算以及其它特定的邏輯功能。

計(jì)數(shù)器種類很多。按構(gòu)成計(jì)數(shù)器中的各觸發(fā)器是否使用一個(gè)時(shí)鐘脈沖源來分,有同步計(jì)數(shù)器和異步計(jì)數(shù)器。根據(jù)計(jì)數(shù)制的不同,分為二進(jìn)制計(jì)數(shù)器,十進(jìn)制計(jì)數(shù)器和任意進(jìn)制計(jì)數(shù)器。根據(jù)計(jì)數(shù)的增減趨勢,又分為加法、減法和可逆計(jì)數(shù)器。還有可預(yù)置數(shù)和可編程序功能計(jì)數(shù)器等等。目前,無論是TTL還是CMOS集成電路,都有品種較齊全的中規(guī)模集成計(jì)數(shù)器。使用者只要借助于器件手冊提供的功能表和工作波形圖以及引出端的排列,就能正確地運(yùn)用這些器件。

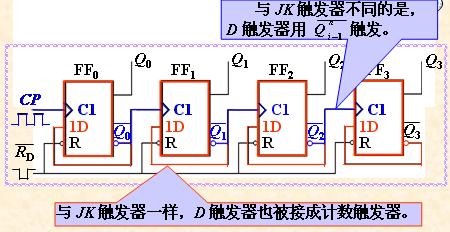

1、用D觸發(fā)器構(gòu)成異步二進(jìn)制加/減計(jì)數(shù)器

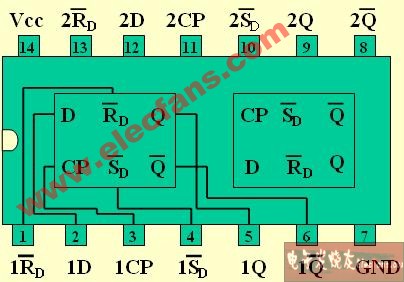

下圖是用四只D觸發(fā)器構(gòu)成的四位二進(jìn)制異步加法計(jì)數(shù)器,它的連接特點(diǎn)是將每只D觸發(fā)器接成T'觸發(fā)器,再由低位觸發(fā)器的 端和高一位的CP端相連接。

端和高一位的CP端相連接。

若將上圖稍加改動(dòng),即將低位觸發(fā)器的Q端與高一位的CP端相連接,即構(gòu)成了一個(gè)4位二進(jìn)制減法計(jì)數(shù)器。

2、中規(guī)模十進(jìn)制計(jì)數(shù)器

CC40192或74LS192是同步十進(jìn)制可逆計(jì)數(shù)器,具有雙時(shí)鐘輸入,并具有清除和置數(shù)等功能,其引腳排列及邏輯符號(hào)如下圖所示。

74LS192同步十進(jìn)制可逆計(jì)數(shù)器邏輯功能總結(jié):

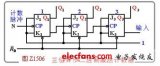

3、計(jì)數(shù)器的級(jí)聯(lián)使用

一個(gè)十進(jìn)制計(jì)數(shù)器只能表示0~9十個(gè)數(shù),為了擴(kuò)大計(jì)數(shù)器范圍,常用多個(gè)十進(jìn)制計(jì)數(shù)器級(jí)聯(lián)使用。

同步計(jì)數(shù)器往往設(shè)有進(jìn)位(或借位)輸出端,故可選用其進(jìn)位(或借位)輸出信號(hào)驅(qū)動(dòng)下一級(jí)計(jì)數(shù)器。

下圖是由CC40192利用進(jìn)位輸出控制高一位的CPU端構(gòu)成的加數(shù)級(jí)聯(lián)圖。用兩個(gè)CC40192計(jì)數(shù)器可以構(gòu)成100進(jìn)制計(jì)數(shù)器。

4、實(shí)現(xiàn)任意進(jìn)制計(jì)數(shù)

(1)用復(fù)位法獲得任意進(jìn)制計(jì)數(shù)器

假定已有N進(jìn)制計(jì)數(shù)器,而需要得到一個(gè)M進(jìn)制計(jì)數(shù)器時(shí),只要M<N,用復(fù)位法使計(jì)數(shù)器計(jì)數(shù)到M時(shí)置“0”,即獲得M進(jìn)制計(jì)數(shù)器。

(2)利用預(yù)置功能獲M進(jìn)制計(jì)數(shù)器

用三個(gè)CC40192可組成421進(jìn)制計(jì)數(shù)器。

外加的由與非門構(gòu)成的鎖存器可以克服器件計(jì)數(shù)速度的離散性,保證在反饋置“0”信號(hào)作用下計(jì)數(shù)器可靠置“0”。

三、實(shí)驗(yàn)設(shè)備與器件

1、 +5V直流電源

2、 雙蹤示波器

3、 連續(xù)脈沖源

4、 單次脈沖源

5、 邏輯電平開關(guān)

6、 邏輯電平顯示器

7、 譯碼顯示器

8、 CC4013×2(74LS74)

CC40192×3(74LS192)

CC4011(74LS00)

CC4012(74LS20)

四、實(shí)驗(yàn)內(nèi)容

1、用74LS74 D觸發(fā)器構(gòu)成4位二進(jìn)制異步加法計(jì)數(shù)器。

實(shí)驗(yàn)步驟- 連接電路后,按單次脈沖源,觀察輸出端狀態(tài)變化。

4位二進(jìn)制異步加法計(jì)數(shù)器狀態(tài)表:

將圖電路中的低位觸發(fā)器的Q端與高一位的CP端相連接,構(gòu)成減法計(jì)數(shù)器,按實(shí)驗(yàn)內(nèi)容2)、3)進(jìn)行實(shí)驗(yàn),觀察并列表記錄Q 3 ~Q0的狀態(tài)。(選做)

2. CC40192或74LS192構(gòu)成十進(jìn)制加法計(jì)數(shù)電路圖(選做)

(減計(jì)數(shù)時(shí)CPU接高CPD接脈沖)

3、用兩片CC40192或74LS192組成兩位十進(jìn)制加法計(jì)數(shù)器

按圖連接電路,輸入計(jì)數(shù)脈沖,進(jìn)行由00—99累加計(jì)數(shù),記錄之。

實(shí)驗(yàn)步驟- 連接電路后,按單次脈沖源,觀察輸出端狀態(tài)變化。

-

二進(jìn)制

+關(guān)注

關(guān)注

2文章

805瀏覽量

42199 -

分頻器

+關(guān)注

關(guān)注

43文章

491瀏覽量

50940 -

計(jì)數(shù)器

+關(guān)注

關(guān)注

32文章

2290瀏覽量

96150 -

D觸發(fā)器

+關(guān)注

關(guān)注

3文章

165瀏覽量

48611 -

CMOS集成電路

+關(guān)注

關(guān)注

4文章

41瀏覽量

14444

發(fā)布評(píng)論請先 登錄

計(jì)數(shù)器極及其應(yīng)用

D觸發(fā)器/J-K觸發(fā)器的功能測試及其應(yīng)用

同步二進(jìn)制計(jì)數(shù)器

什么是二進(jìn)制計(jì)數(shù)器,二進(jìn)制計(jì)數(shù)器原理是什么?

與非門組成二進(jìn)制計(jì)數(shù)器電路圖

異步二進(jìn)制減法計(jì)數(shù)器時(shí)序分析

數(shù)字二進(jìn)制計(jì)數(shù)器的設(shè)計(jì)和實(shí)現(xiàn)

異步二進(jìn)制加法計(jì)數(shù)器電路圖

異步7位二進(jìn)制計(jì)數(shù)器數(shù)據(jù)表

用D觸發(fā)器構(gòu)成異步二進(jìn)制加/減計(jì)數(shù)器

用D觸發(fā)器構(gòu)成異步二進(jìn)制加/減計(jì)數(shù)器

評(píng)論