不管喜不喜歡今年的 iPhone 15,大概都會認可一件事,很多人選擇購買 iPhone 15 Pro 系列的一大動機,就是沖著臺積電3nm工藝的 A17 Pro。

A17 Pro 采用了臺積電最新的 3nm 工藝(N3B)制造,晶體管數量達到了驚人的 190 億,這是全世界第一款采用臺積電 3nm 工藝的手機芯片,也是 3nm 工藝第一次出現普通人就可以買到的大眾消費品上。

要知道,隨著芯片尺寸越來越逼近物理極限,每一代工藝節點升級需要投入也在加速增加,僅臺積電一家的 3nm 新增投入就超過了 200 億美元。

巨大的投入意味著巨大的成本,尤其是在前期工藝尚不成熟、良率較低的情況下,沒有多少行業和公司能夠負擔 3nm 芯片的制造成本。

這其中,智能手機一直是最有實力和動力推動先進制程工藝不斷前進的力量。

一方面是因為智能手機需要在極小的內部空間里塞下算力驚人的芯片,同時還要極可能降低芯片的功耗和發熱;

另一方面是芯片制造太燒錢,也只有一年就能賣出十多億臺的智能手機可以形成規模效應,不斷推動先進制程改進工藝、提高良率,得以讓服務器、PC、游戲主機甚至是汽車用上更先進的芯片制造技術。

但更大的投入、更先進技術是不是就等同于「正確」?可能也未必,iPhone 15 Pro 系列的散熱風波還沒有過去,關于良率或者說成本的拷問,也一直是 3nm 上空的「烏云」。

良率和成本,3nm 的一朵「烏云」

10 月 9 日,《科創板日報》引述業內行業分析稱,三星、臺積電的 3nm 工藝良率目前都在 50%左右。一位接近三星的人士還透露,要贏得高通等大客戶明年的 3nm 移動芯片訂單,良率至少需要提高到 70%。

在半導體制造上,良率直接意味著一整片加工出來的晶圓上能正常工作的芯片的占比。通常來說,一片晶圓上可以同時制造出上百顆同樣的裸芯片,之后將晶圓片上的裸芯片切割開來,就可以封裝后安裝到產品上。

在成熟工藝上,代工廠的良率一般都能達到 99%,但在先進制程上,由于工藝難度和前期的大量問題,良率就可能非常低。但按照慣例,代工廠并不負責承擔不良芯片的制造成本,這部分費用還是由芯片設計客戶承擔,比如蘋果、英偉達。

當然,「50%的良率」未必可信,此前就有大量各種來源的信息給出了各不相同的良率,包括 A17 Pro 從產業鏈傳出的良率就為 70-80%。但這些消息無一例外,都透露出一個關鍵信息,即 3nm 的良率很低。

良率越低,成本越高。

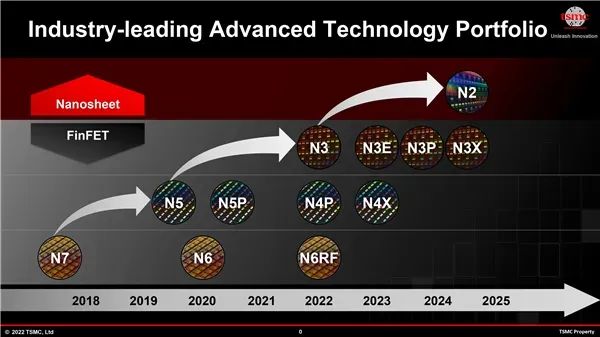

這也是為什么除了蘋果,其他所有主要芯片設計公司都沒有選擇在 2023 年這個節點采用 3nm 工藝,更多還是瞄準 N3B 之后的工藝。按照臺積電早前的規劃,臺積電 3nm 工藝其實是包括 N3B(即 N3)、N3E、N3P、N3X 等多個版本。

臺積電制程路線圖,圖/臺積電

甚至在業界傳聞中,就連蘋果也是與臺積電簽訂了一份「對賭」協議,規定未來一年臺積電 N3B 工藝為蘋果專用,且廢片均由臺積電承擔成本,而非蘋果買單。

而如果說良率很大程度上決定了 3nm 的成本居高不下,進而提高了芯片設計公司導入的門檻,那 3nm 的功耗和發熱問題,也是阻止他們較早導入的關鍵原因。

發熱和功耗,3nm 的另一朵「烏云」

iPhone 15 Pro 系列的發熱問題這里就不再贅述了,我們之前就在文章中分析,iPhone 15 Pro 系列發熱的「罪魁禍首」就是設計和芯片兩大部分,后者自然就是采用 3nm 工藝的 A17 Pro。

坦率地說,iPhone 15 Pro 的發熱到底有多大程度是因為 A17 Pro,A17 Pro 的問題有多大程度是因為臺積電 N3 工藝,目前來講都還沒有比較切實的論斷。

但問題一定是有的。按照蘋果給出的數據,A17 Pro 的晶體管數量為 190 億,比前代 A16 增加了近 20%,CPU 性能卻只提升了約 10%,GPU 核心數從 5 個增加到 6 個的同時,峰值性能提升了 20%。不過按照 GeekBench 數據來看,峰值性能大幅提高的另一面,是 A17 Pro TDP 峰值功率達到了驚人的 14W。

這不只是蘋果和臺積電面對的問題。

隨著晶體管尺寸不斷逼近物理極限,量子隧穿效應帶來的問題也越發嚴重,失控的電子引發的漏電,會導致芯片更嚴重的發熱和功耗問題。所以從 7nm 以后,整個業界的「制程焦慮」越發明顯,對摩爾定律新出路的探索越發加快。

當然回到 3nm 上,臺積電和三星也不是毫無準備的。

N3E 才是臺積電真正的 3nm,三星押寶 GAA

相比 A17 Pro 上采用的 N3B 工藝,N3E 是臺積電計劃推出的一個完全不同的工藝節點,在功耗控制方面更加理想。

臺積電不僅用上了「創新的阻擋工藝」,更重要的是 FINFLEX 技術的導入,讓芯片設計人員可以在一個模組內混搭不同的標準單元,實現同時優化性能、功耗和面積。包括 N3P、N3X、N3AE、N3S 等工藝節點,實際都是 N3E 的后續變體。

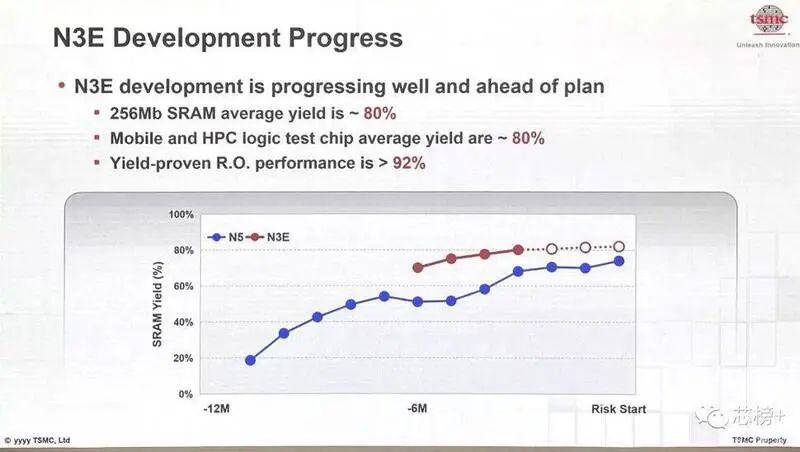

而且從過去半年的消息來看,普遍指出 N3E 的良率要好于 N3B,一份文件顯示,N3E 256Mb SRAM 平均良率達到 80%,Mobile 與 HPC 芯片的良率也達 80%。此前,也一直存在臺積電考慮放棄 N3B 節點,推遲到 N3E 節點正式進入 3nm 的傳聞。

圖/臺積電

9 月 7 日,聯發科與臺積電共同宣布,聯發科首款采用臺積電 3 納米制程生產的天璣旗艦芯片已經成功流片,該款天璣旗艦芯片將于 2024 年下半年上市。基本確定,這款天璣旗艦芯片(天璣 9400)采用了臺積電 N3E 工藝,而官方透露:

臺積電 N3E 工藝的邏輯密度相比 N5 工藝增加了約 60%,在相同功耗下速度提升 18%,或者在相同速度下功耗降低 32%。

相比之下,去年年末的 IEDM(IEEE 國際電子器件大會)上,臺積電披露 N3B 工藝實際只將 SRAM 密度提高了約 5%(相比 N5 工藝),與其最初聲稱的 20% 也是相去甚遠。

另外,9 月底業內又傳出英偉達也下單了臺積電 3nm 制程,以生產 Blackwell 構架 B100 數據中心 GPU,預計將采用更側重性能增強的 N3P 或 N3X 工藝。

可以這么說,N3E 及其變種對于大多數芯片廠商來說,才是真正的 3nm。

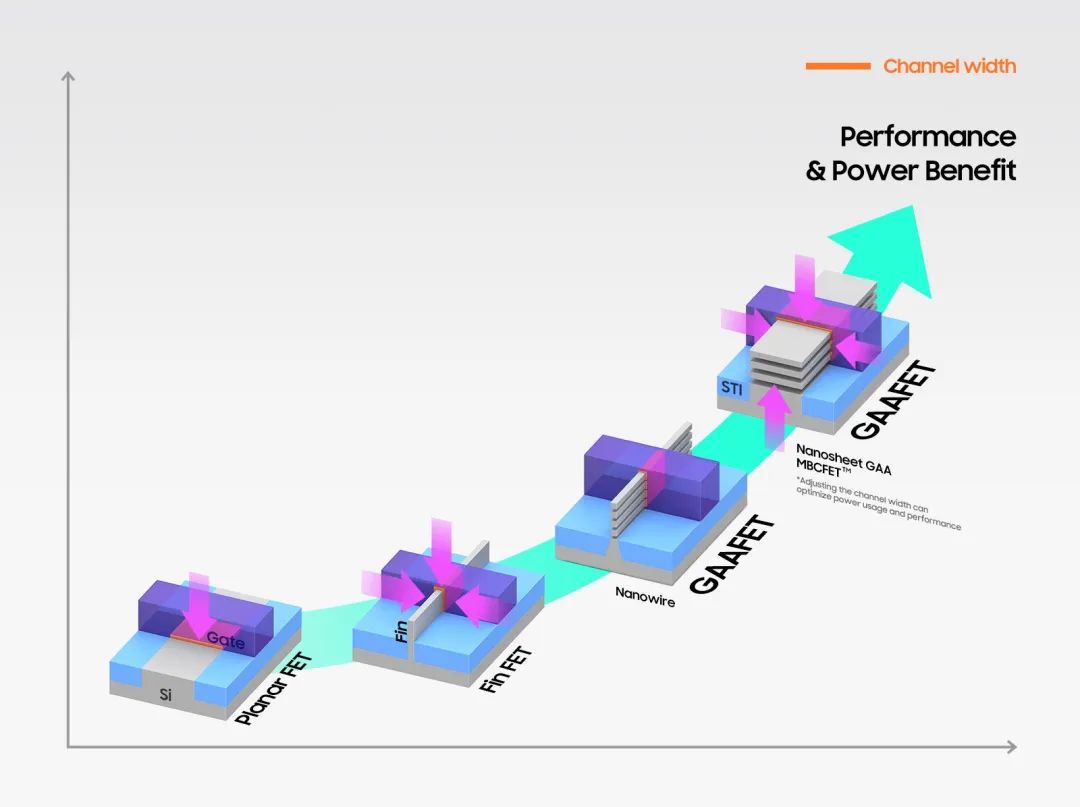

而在三星這邊,去年 6 月就率先宣布了在 3nm 成功應用 GAAFET 技術。GAAFET 的正式名稱是全環繞柵極晶體管(Gate-All-Around FET),架構上最明顯的變化在單位面積內的利用效率。

晶體管架構變遷,圖/三星

眾所周知,計算性能最底層其實就是晶體管的「一開一關」,代表了二進制中的「0」和「1」,更底層是對晶體管內通道(又稱溝道)的控制能力。FinFET 第一次將通道從橫向轉為豎向,而三星采用了寬通道(納米片)的 GAAFET 技術,在單位面積內支持更多通道的控制,由此得以實現了:

與 5nm 工藝相比,第一代 3nm 工藝可以使功耗降低 45%,性能提升 23%,芯片面積減少 16%;而第二代 3nm 工藝則使功耗降低 50%,性能提升 30%,芯片面積減少 35%。(注:三星第二代 3nm 也要等到明年。)

相比臺積電還在用的 FinFET 技術,GAA 擁有更好的靜電控制能力。法國信息技術電子實驗室高級集成工程師 Sylvain Barraud 也指出:「與 FinFET 相比,GAA 堆疊的納米線還具有更高的有效溝道寬度,能夠提供更高的性能。」

事實上,臺積電和英特爾也早早宣布將在 2nm 節點正式導入 GAA 技術,之所以沒有在 3nm 節點,主要顧慮還是技術成熟度不高帶來的良率問題,三星 GAA 3nm 此前就多次傳出嚴重的良率問題,甚至是在宣布量產后找上美國 Silicon Frontline Technology 公司,合作提高 3nm GAA 工藝的良率。

所以對三星來說,關鍵還是在于保持 3nm GAA 能效優勢的同時,如何盡可能地提高良率。

寫在最后

時至今日,所有人都明白,在物理尺寸上極其微小的芯片,在現實世界是何等的重要,而芯片上的每一寸進步,實質上也會推動全世界算力的大幅提升,這也是過去幾十年人類科技進步的主要動力之一。

與 1nm 之后的未來相比,3nm 目前遇到的問題既不困難也不意外,晶圓廠早就有所預想和準備。但即便是芯片制程無限逼近物理極限的幾年后,從來也沒有什么無解的問題。

大規模集成電路興起的時候,糟糕良率一度讓很多公司失去了信心,但還是仙童半導體、德州儀器等公司將芯片制造車間換成了無塵的超凈間,進入的人都要穿上極其嚴密的防護服,確保灰塵、汗液和毛發不會損壞脆弱的晶圓,實現了足夠高的良率。

MOS 管(場效應晶體管)接近性能極限的時候,很多人也認為晶體管不能再變小,芯片性能提升到了盡頭。但最終,FinFET 架構繼續推動了芯片技術的前進。

2019 年,在臺積電內部舉辦的運動會上,臺積電創始人張忠謀被媒體問到了摩爾定律是否走到盡頭時,他認為這個問題的答案,沒有人知道,因為后面至少還有 5nm、3nm 和 2nm 的技術。但他相信,摩爾定律的未來會是:

山窮水盡疑無路,柳暗花明又一村。

-

手機芯片

+關注

關注

9文章

374瀏覽量

49843 -

芯片制造

+關注

關注

10文章

681瀏覽量

29593 -

3nm

+關注

關注

3文章

232瀏覽量

14296

原文標題:3nm,手機芯片的全新戰爭

文章出處:【微信號:IC修真院,微信公眾號:IC修真院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

小米自研3nm旗艦SoC、4G基帶亮相!雷軍回顧11年造芯路

傳AMD再次進軍手機芯片領域,能否打破PC廠商折戟移動市場的“詛咒”

3nm,手機芯片的全新戰爭

3nm,手機芯片的全新戰爭

評論