隨著ChatGPT強勢來襲,AI人工智能應用層出不窮。智能化時代,數據量指數型增長,摩爾定律已經不能滿足當前的數據處理需求,元器件的物理尺寸已經接近極限。人工智能的硬件平臺面臨兩大艱巨挑戰:算力不足和能效過低。那么,有什么方法提高芯片的算力呢?

其實關鍵還是在于系統設計和芯片加工。系統設計,重在高性能微架構和先進算術運算,芯片加工則有賴于先進工藝制程和先進封裝制備。今年9月份的時候,EETOP曾從運算機制的角度,探討了計算芯片算力的提升。本期,我們試著從芯片架構方面,繼續探討芯片算力提升的話題。

計算芯片架構趨勢:存算一體

現在,無論是CPU還是GPU,采用的都是70年前的馮.諾伊曼體系架構。馮諾依曼體系結構是現代計算機的基礎。在馮諾依曼架構中,計算和存儲功能分別由中央處理器和存儲器完成。計算機的 CPU 和存儲器是相互獨立發展的,也就是CPU和內存是在不同芯片上的,它們之間的通信要通過總線來進行。數據量少的時候沒問題,但一旦數據變多,總線本身就會擁擠成為瓶頸。而現在的GPU,并行處理能力越來越強。當數據傳輸速度不夠時,就會限制算力的天花板, 嚴重影響目標應用程序的功率和性能。

業界很多也都在研究相關的解決方案,以實現更為有效的數據運算和更大的數據吞吐量,其中“存算一體”被認為是未來計算芯片的架構趨勢。它是把之前集中存儲在外面的數據改為存在GPU的每個計算單元內,每個計算單元既負責存儲數據,又負責數據計算。

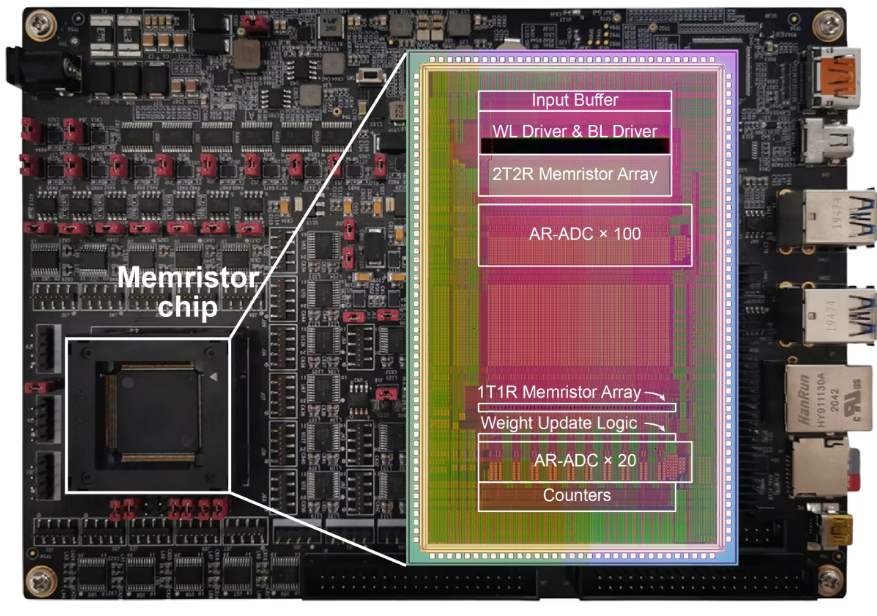

這幾天,清華大學研制出全球首顆全系統集成的、支持高效片上學習(機器學習能在硬件端直接完成)的憶阻器存算一體芯片,可謂刷爆行業媒體圈。這項最新的研究證明了在全集成憶阻器存算一體系統上實現矩陣向量乘法的可行性。據了解,清華大學的研究團隊對芯片算法、系統、架構、電路與器件進行了全層次協同優化設計:

器件層面,實現300萬個具有高模擬可編程性的憶阻器與CMOS電路的單片集成;

電路層面,提出電壓模神經元電路,支持可變精度計算、激活操作、低功耗模數轉換;

架構層面,提出雙向TNSA(transposable neurosynaptic array)架構,以最小的面積、能耗開銷實現靈活的數據流重構;

系統層面,48個CIM核心支持多種權重映射方案,提高推理任務并行度;算法層面,利用多種硬件-算法協同優化方案,降低硬件非理想特性對準確率的影響。

傳統計算系統,其計算器件用的是場效應晶體管,計算范式是布爾邏輯數字計算,架構采用的是存算分離;而存算一體計算系統的計算器件是憶阻器,計算范式用的是物理定律模擬計算,架構是存算一體。存算一體架構徹底消除了數據在邏輯處理器與存儲芯片之間的搬遷問題,減少能量消耗及延遲。據公開資料顯示,相同任務下,該芯片實現片上學習的能耗僅為先進工藝下專用集成電路(ASIC)系統的1/35,同時有望實現75倍的能效提升。

摩爾定律很好的歸納了信息技術進步的速度,但隨著半導體芯片技術的快速發展,摩爾定律已經不太適用于現在的半導體芯片發展規律了。馮諾依曼架構遇到了瓶頸,這時便需要憶阻器的魔力,來實現存算一體,打破傳統的馮諾依曼架構,開拓新的存儲器道路。談到這里,我們就必須來認識認識憶阻器這個非線性電路元件了。

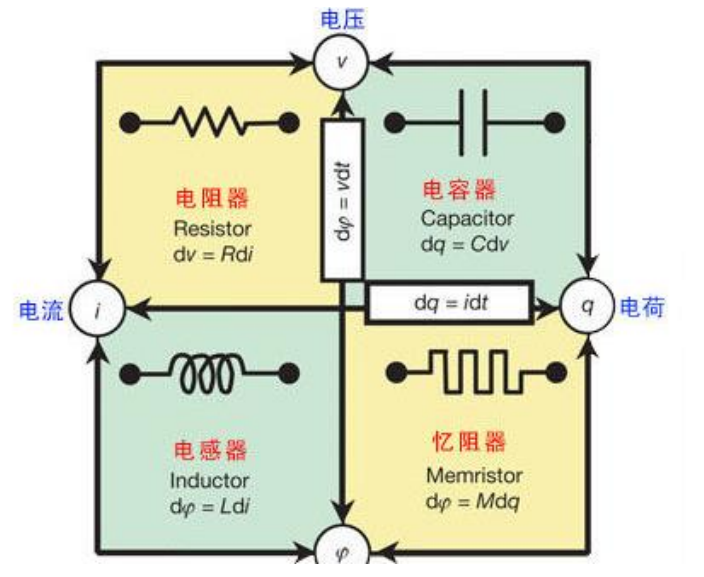

憶阻器的發展

憶阻器英文名為memristor,也被稱為阻變存儲器(RRAM),用符號M表示,與電阻R,電容C,電感L構成四種基本無源電路器件。它是連接磁通量與電荷之間關系的紐帶,同時具備電阻和存儲的性能,是一種新一代高速存儲單元。其功耗,讀寫速度都要比傳統的隨機存儲器優越,是硬件實現人工神經網絡突觸的最好方式,主要應用于非易失存儲、邏輯運算以及類腦神經形態計算。

憶阻器全稱記憶電阻,是一種具有電荷記憶功能的非線性電阻,于1971年,由加州大學伯克利分校的華裔科學家蔡少棠教授提出。蔡教授從電路完整性角度出發,從數學上推導出憶阻器的概念。不過,由于缺乏實驗的支撐,而且傳統存儲器在工藝上和摩爾定律契合的很好,一直在刷新著自己的存儲極限,所以在那之后的很長一段時間,人們認為沒有必要花費時間和金錢去研究憶阻器。

憶阻器發展的拐點,發生在2000年之后。2000-2008年,A Beck等人在Cr摻雜的SrZrO3中觀察到憶阻器滯回曲線,并指出器件具有存儲功能,2006年HP實驗室證明了Crossbar RRAM,并于2008年在《Nature》發表了“下落不明的憶阻器找到了”的相關文章,同年,HP公司制備出憶阻器。科學家們開始意識到憶阻器的優勢和作用,全世界相關科學家都紛紛參與到憶阻器的研究中來,憶阻器研究高潮就此到來。

類腦計算及神經形態計算是當今科研熱點之一,憶阻器是神經元網絡的核心器件,它為發展信息存儲與處理融合的新型計算體系架構,突破傳統馮·諾伊曼架構瓶頸,提供了可行的路線,其性能直接影響神經元網絡的計算能力。

下面為大家分享一段教學視頻,是清華大學高濱教授主講的“憶阻器存算一體芯片與類腦計算”。高濱老師表示,現有計算系統普遍采用存儲和運算分離的架構,存在存儲墻與功耗墻瓶頸,嚴重制約了系統算力和能效的提升。存算合一的電子突觸就是憶阻器。不過,憶阻器也面臨著嚴峻的挑戰。核心挑戰之一是器件非理想特性,即憶阻器件性能存在離散性和不穩定性,嚴重影響計算精度;另一個關鍵挑戰就是模擬計算的誤差累積。

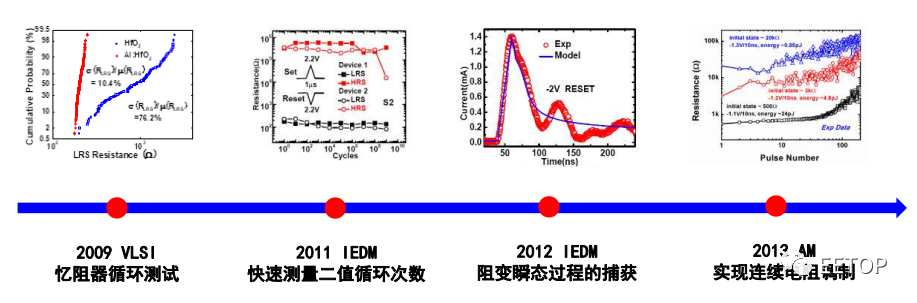

高濱教授介紹,解決的辦法就是存算一體芯片的協同設計。存算一體芯片急需跨層次的協同優化方案,單一層面的優化已經難以達到高性能。其實憶阻器研究的每一次推進和成功,都離不開測試設備提供的數據支持。高濱表示:“測試設備的進步,為憶阻器的研發做出了重要的貢獻!”

高濱教授關于憶阻器研究的幾個關鍵時間點

憶阻器電學測試現狀與展望

存算一體技術對憶阻器特性要求非常高,測試難度也很大。通常,憶阻器的測試可分為三大類,即:

憶阻器基礎研究測試,包括憶阻器參數表征、分類及測試流程,以及分析器件在相應的交流、直流、脈沖電信號作用下的憶阻特性;

憶阻器性能研究特性,旨在提高憶阻器存儲性能和模擬神經元的性能,如功耗、擦寫速度、集成度和可靠性等各方面;

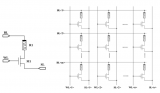

最后是憶阻器集成及應用研究測試,憶阻器單元集成結構是實現陣列憶阻器的關鍵,如1T1R、1TNR等cell及陣列結構的測試。

如果憶阻器被用于神經元方面的研究,其性能測試除了擦寫次數和數據保留時間外,還需要進行神經突觸阻變動力學測試。

結束語

在 AI 算力需求暴漲下,存算一體被認為是突破算力瓶頸最有前景的新賽道。目前,國內外很多科技企業及初創公司都在積極開展相關的研發。據相關預測數據顯示,到 2030 年,基于存算一體技術的芯片市場規模有望超過千億人民幣。憶阻器在數據存儲、存算一體、類腦計算等領域將發揮越來越重要的作用。目前,憶阻器已經具備在先進CMOS工藝平臺集成的能力。不過,憶阻器依然面臨著嚴峻的挑戰,核心挑戰之一是器件非理想特性,即憶阻器件性能存在離散性和不穩定性,嚴重影響計算精度;另一個關鍵挑戰就是模擬計算的誤差累積。

基于憶阻器的存算一體變革性技術正成為學術界和產業界關注的前沿熱點。未來仍期待在多通道快切換、高時間分辨等方面取得更大進步。期待***走的更遠、更高、更好!

-

芯片

+關注

關注

459文章

52253瀏覽量

436970 -

人工智能

+關注

關注

1804文章

48788瀏覽量

246930 -

憶阻器

+關注

關注

8文章

75瀏覽量

20314 -

ChatGPT

+關注

關注

29文章

1588瀏覽量

8827

原文標題:憶阻器,你了解嗎?刷爆朋友圈的全球首顆清華憶阻器存算一體芯片究竟是個啥?

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

憶阻器存算一體芯片新突破!有望促進人工智能、自動駕駛等領域發展

中國制造的全球首款多陣列憶阻器存算一體系統問市

基于憶阻器存算一體芯片的研究進展

基于憶阻器存算一體芯片研究進展、總結與展望

憶阻器,你了解嗎?全球首顆清華憶阻器存算一體芯片究竟是個啥?

全球首顆清華憶阻器存算一體芯片究竟是個啥?

全球首顆清華憶阻器存算一體芯片究竟是個啥?

評論