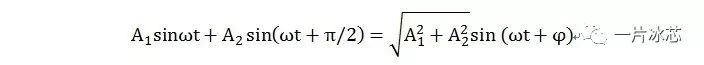

1. PI的數學原理

對于信號sin ωt和sin (ωt+π/2),可通過調整二者幅值,實現相位在0~π/2之間的信號。

其中,

對于,

C為常量,上式可寫為:

函數tanx和

的趨勢相似,在x=0時,二者均為0,tanx在x=π /2時趨于無窮大,

在x趨于C時趨于無窮大。

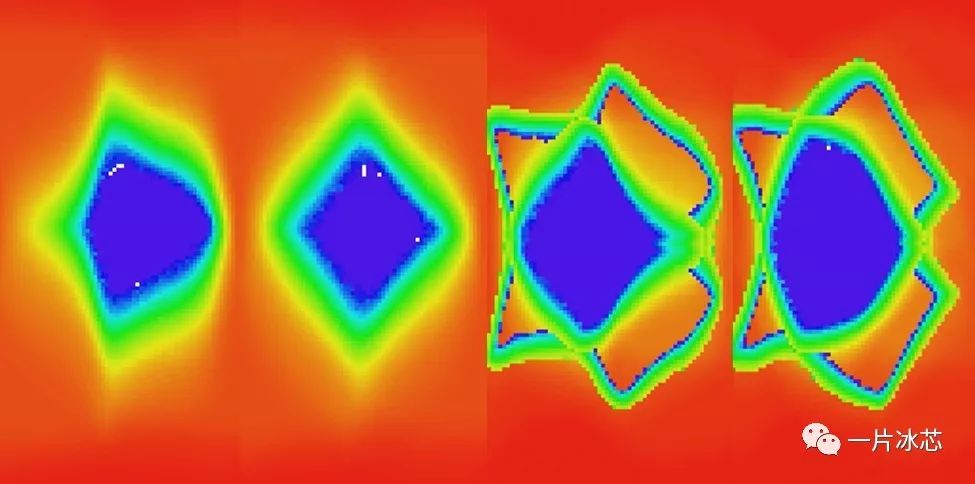

設C為1,利用Matlab,畫出相位φ與A2的關系如下圖所示。其中,藍線為相位φ與A2的關系,紅線為理想關系曲線。

Fig1. 相位與幅值的關系

可以將公式中π/2推廣到π/4,π/8…,可推導出分相數越多線性度越好,但電路設計越復雜,一般都是分成四個相限。

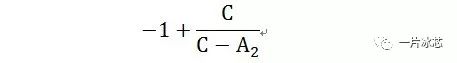

2. PI結構及原理

PI的核心功能就是對來自cpll或qpll的四相位時鐘進行相位插值,從而使輸出相位能跟隨PI code變化,最終使時鐘邊沿與數據中心位置對齊,達到最佳采樣。PI整體框圖如圖2所示,通路包括DCC Circuit、Clock Buffer、Phase Mixer、Limiting Amplifier、CML-to-CMOS Converter、Divider Circuit、Bias和DAC電路。

Fig2. PI整體框圖

PI通路上的每個電路都不可或缺,下面章節將逐一分析每個模塊的功能。

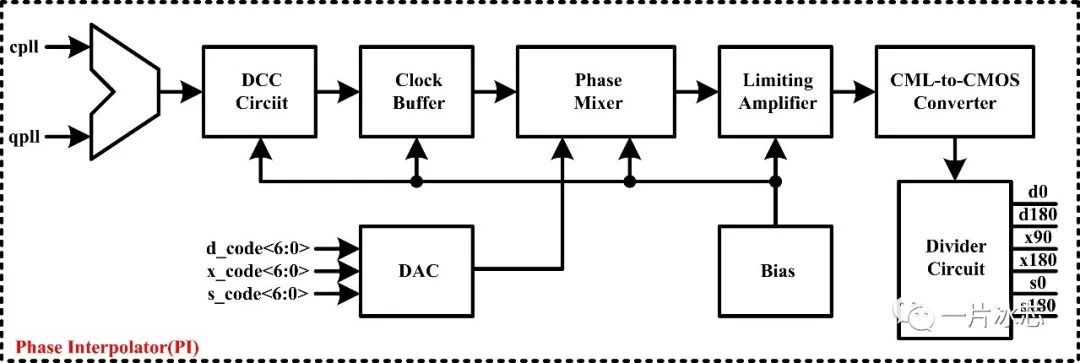

2.1 DCC Circuit

cpll或qpll本地產生的四相位時鐘可以保證每個相位50%的占空比,但由于SerDes整體規模龐大,pll時鐘往往經過上千微米的走線,layout中即使采用頂層金屬,外加電源或地的Shielding也不可避免的產生干擾,進而影響PI輸入時鐘的占空比,而占空比失真對CDR的影響是致命的,占空比必須要嚴格限制在50%左右,有些設計會在PI進入CDR的slicer之前加入復雜的占空比校正電路。

本人用到的占空比校正電路較簡單,結構如圖3所示。該結構是一個電流源作負載的源級負反饋電路,整體傳函呈現帶通特性,可濾除pll時鐘通路上低頻干擾引起的占空比失真。

Fig3. Duty-Cycle-Correction Circuit

2.2 Clock Buffer

正弦信號和三角波信號插值可提高PI線性度,因此進入Phase Mixer之前需要將方波信號(通常為半擺幅)整形為正弦信號(三角波不易實現)。Clock Buffer通常采用一級或多級CML結構的Buffer,同時為了保證寬頻率范圍內都為正弦信號,Clock Buffer的負載電阻、電容及尾電流源通常設為可編程結構。

2.3 Phase Mixer

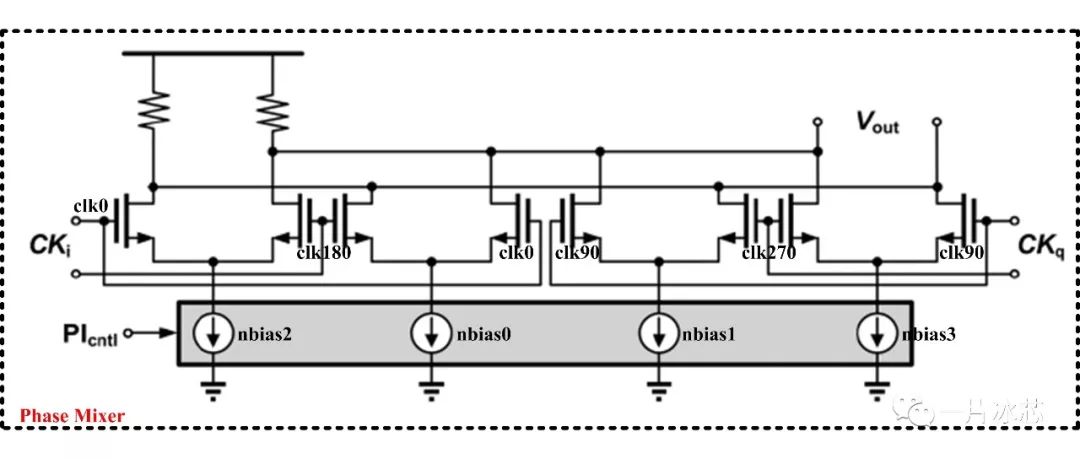

Phase Mixer采用CML結構,如圖4所示。其中PIcntl每個相位區間(共四個相位區間)共有32種電流組合,因此插值精度為360°/128=2.8125°。

Fig4. Phase Mixer

進行相位插值時每次只選中兩個尾電流源,選中方式由DAC單元中的d/x/s_code<6:0>中的高兩位決定。具體控制方式如圖5所示,其中Sel6和Sel5對應d/x/s_code<6:5>位,1LSB的ilive電流用于解決相位區間切換時尾電流建立時間引起的PI非線性。

Fig5.相位插值區間真值表

2.4 Limiting Amplifier

Phase Mixer輸出信號幅度受DAC輸入code調制,這會引入非線性,因此后一級需要增加限幅放大器,來解決幅度變化引起的PI非線性。限幅放大器與Clock Buffer結構類似,都是采用CML結構。

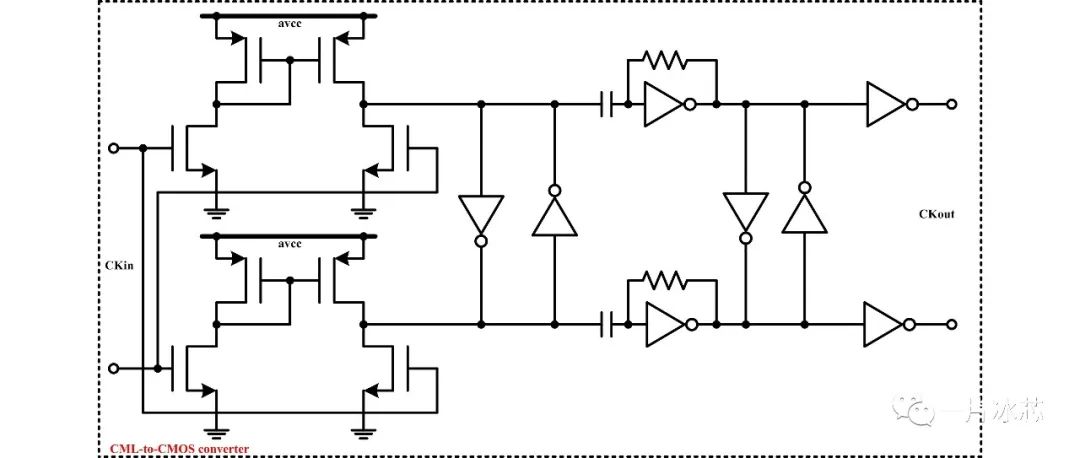

2.5 CML-to-CMOS Converter

前級Limiting Amplifier輸出信號幅度為半擺幅的CML電平,進入分頻器之前需要轉換為CMOS電平,這就需要CML-to-CMOSConverter,結構框圖如圖6所示。

Fig6.CML-to-CMOS Converter

反相器自偏置的ac-coupling circuit結構可以隔離前級直流干擾,進而改善時鐘占空比。

2.6 Divider Circuit

分頻電路通過DFF級聯的方式,對時鐘信號進行1/2/4/8/16分頻,來滿足不同速率需求。分頻器要特別注意復位時序,復位時序會影響時鐘的初始相位,初始相位錯亂,會導致后面所有相位固定錯誤。

2.7 Bias

Bias電路用于產生通路上所需的偏置電流。

2.8 DAC

相位插值器是在相位差為90°的4個相位區間進行相位插值,每個相位區間為了得到32個相位,需要一個5位DAC。為了獲得較高精度的DAC設計,一般采用分段式結構的電流舵DAC。該結構是將數字碼分為兩部分進行轉換,一般是較高位的數字碼采用溫度計碼,低位的數字碼采用二進制碼。

相位插值器將相位控制信號轉化為帶權重的電流,再根據兩個輸入信號之間的相位關系對兩個電流信號進行混合,通過負載電阻又將電流信號轉換為電壓信號輸出。

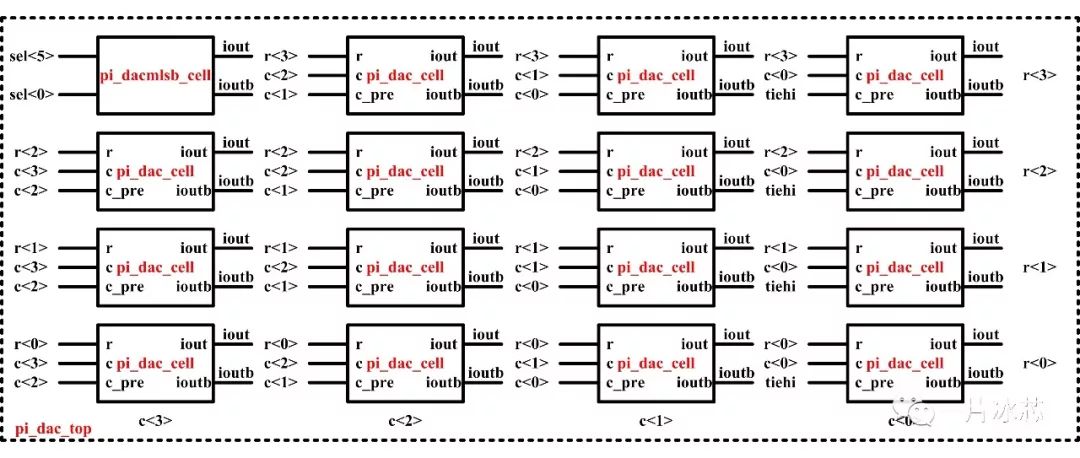

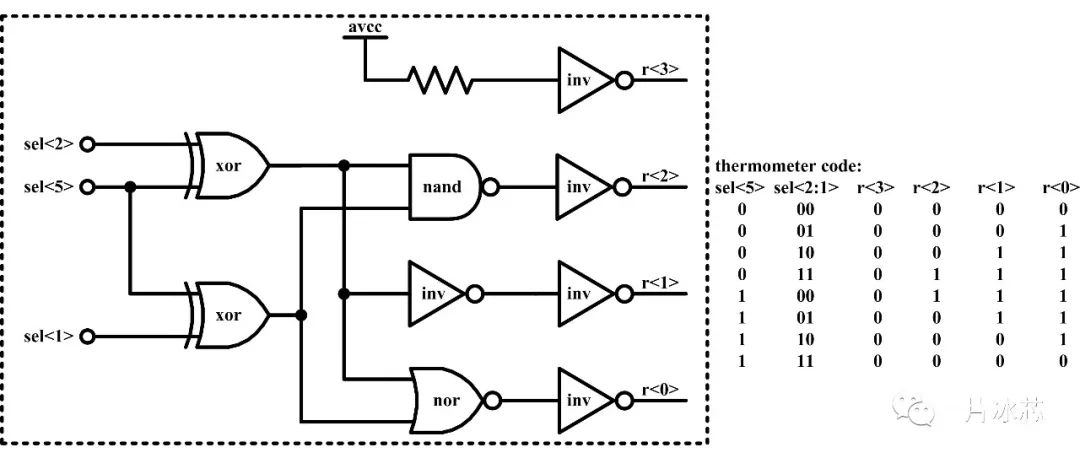

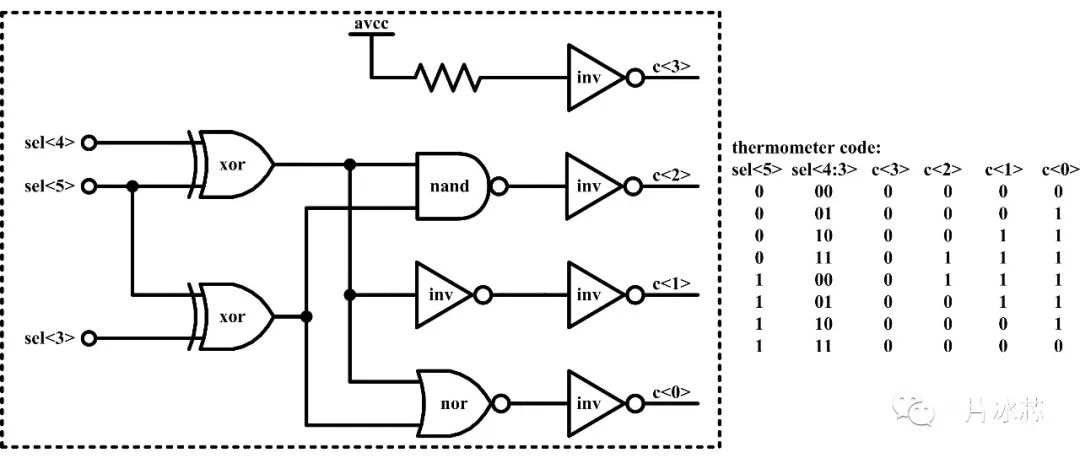

該DAC電路輸入的5位數字碼采用高4位,低1位的分段結構,高位碼為溫度計譯碼,低位碼為二進制碼。行列譯碼為4位二進制碼到溫度計碼的譯碼方式,其中行列譯碼都為2位二進制到溫度計譯碼,即sel<4:1>位是溫度計編碼,控制15路電流源;sel<0>是二進制編碼,控制1路電流源,通過5位控制編碼可以產生32個電流臺階步長。

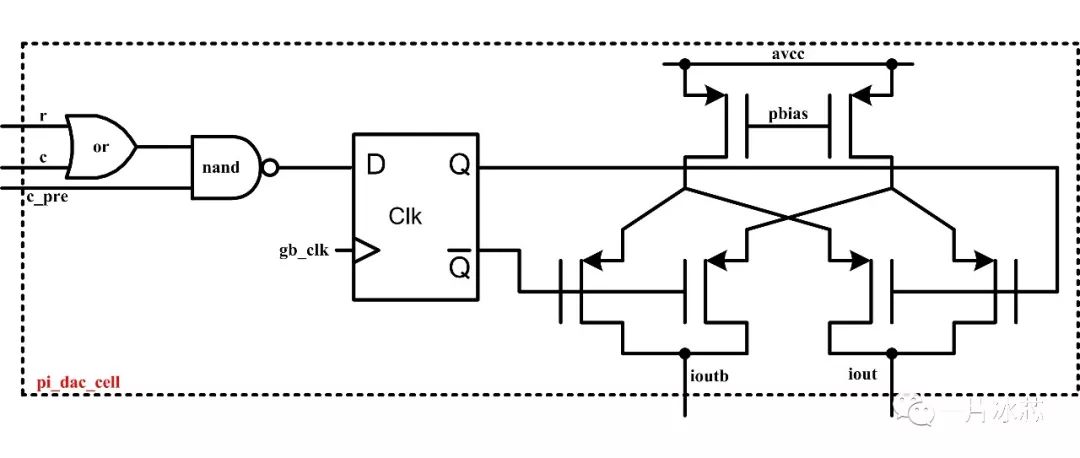

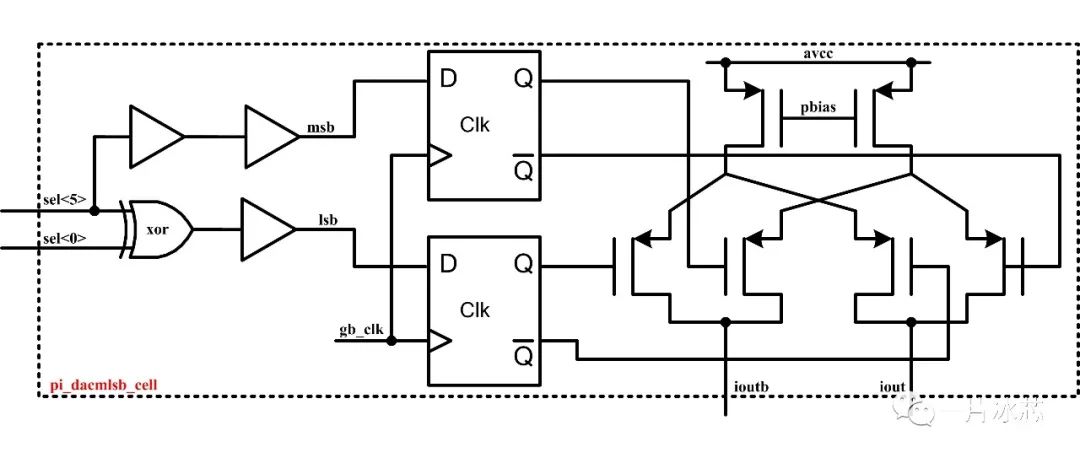

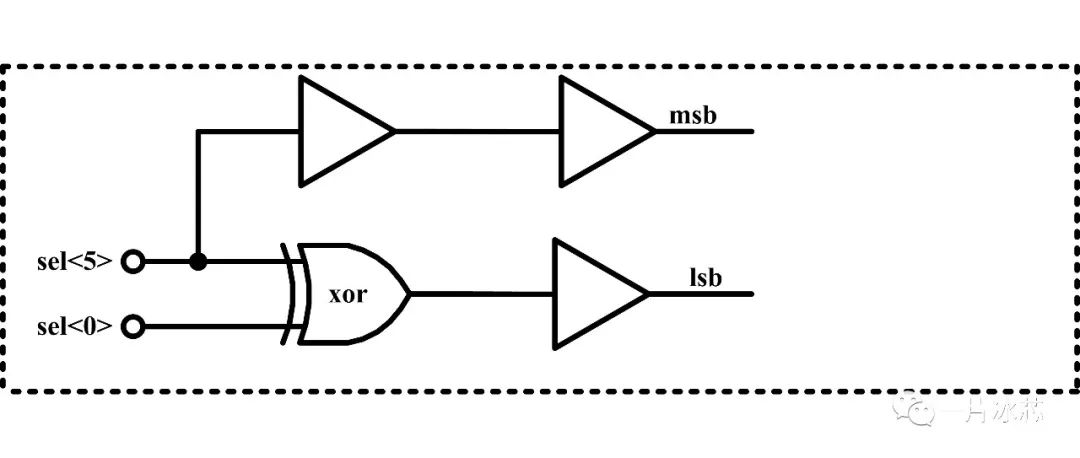

sel<4:0>都與sel<5>進行異或操作,這樣可以保證相位區間切換時,電流不會發生突變。圖7給出了采用行列譯碼方式的電流舵DAC頂層框圖,其中pi_dacmlsb_cell和pi_dac_cell內部結構分別如圖8和圖9所示,行列譯碼和二進制譯碼邏輯如圖10~12所示。

Fig7.DAC Top

Fig8. DAC Top中的pi_dac_cell單元

Fig9.DAC Top中的pi_dacmlsb_cell單元

Fig10. 行譯碼產生溫度碼

Fig11. 列譯碼產生溫度碼

Fig12.高位和低位二進制碼

**3. **測試結果

某一速率下,s路線性度對眼圖的影響如圖13所示。可以看出,s路非線路會導致眼圖形狀畸變,相當于眼圖測量的“尺子”刻度不均勻。

Fig13. s路非線性對眼圖的影響

**4. **總結

①PI輸出時鐘要滿足50%占空比,一般會加入占空比校正電路;

②正弦信號和三角波插值線性度高,插值之前需要整形;

③在非插值區間引入一個LSB的小電流,可以減小區間切換時尾電流的建立時間,從而提高PI線性度;

④PI后增加限幅放大器可以減小PI Code對幅度的調制,從而提高PI線路度;

⑤反相器自偏置的ac-coupling circuit結構可以隔離前級直流干擾,進而改善時鐘占空比;

⑥分頻器復位時序會影響時鐘的初始相位,初始相位錯亂,會導致后面所有相位固定錯誤,設計時應多加留意;

⑦DAC產生的電流要呈現溫度碼特性。

-

負反饋電路

+關注

關注

1文章

35瀏覽量

9391 -

CMOS電平

+關注

關注

0文章

20瀏覽量

7382 -

時鐘信號

+關注

關注

4文章

468瀏覽量

29140 -

限幅放大器

+關注

關注

1文章

50瀏覽量

10272 -

負載電阻

+關注

關注

0文章

112瀏覽量

8176

發布評論請先 登錄

PI推出電源設計軟件PI Expert7.1.5版PI

raspberry_pi各版本差別

冷或門系列PI2121、PI2123 及 PI2125的應用指南

raspberry pi官網

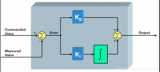

PI調節器介紹及設計

串聯型PI和并聯型PI調節器的比較

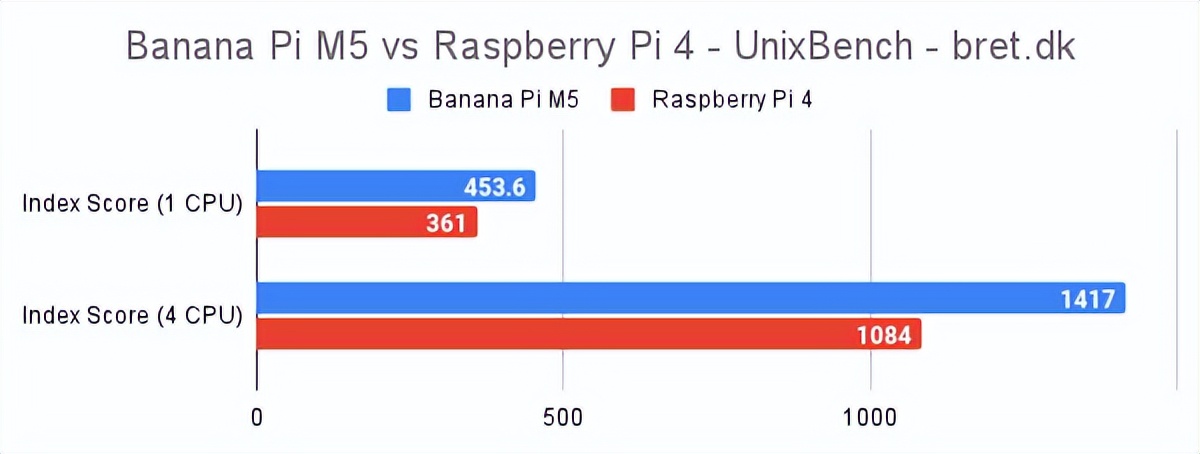

Banana Pi M5 與 Raspberry Pi 4 – 基準測試

PI的數學原理 PI結構及原理

PI的數學原理 PI結構及原理

評論