在信號完整性分析中存在兩類基本問題:

一類問題是與信號路徑相關的反射問題和相鄰路徑間的串擾問題,這類問題都與信號的上升時間和時鐘工作頻率有關,稱之為信號路徑問題;

另一類問題則與信號路徑無關,而是歸因于電源路徑和地路徑,稱之為電源分配系統問題,又叫電源完整性問題。

電源分配系統(PDS)的用途就是為每個用電芯片提供恒定的電壓。根據用電芯片器件工藝的不同,該電壓一般為5V、3.3V或2.4V,通常要求供給用電芯片的電壓波動不超過5%。

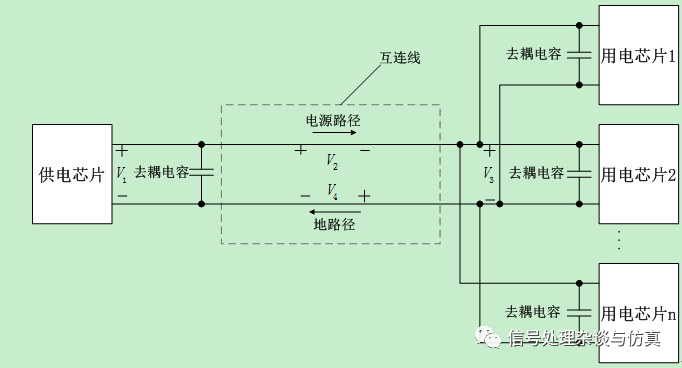

如圖1所示,一個完整的PDS包括供電芯片、去耦電容、用電芯片和連接這些單元之間的互連線。

?圖1 電源分配系統組成

由于在PDS中,通過電源路徑和地路徑上的電流不可能是絕對的直流電流,都會或多或少的含有一定比例的交流電流在里邊,由于在由電源路徑和地路徑組成的電流回路中存在回路電感L,根據V=Ldi/dt可知,交流電流會使整個電源分布路徑上存在電壓降,因此供給用電芯片的電壓通常會降低,這問題稱為軌道塌陷。

由圖1可知,在電流返回路徑上產生的電壓降通常稱為地彈噪聲,地彈噪聲問題是信號完整性中常見的一種問題。因此,要使電流變化引起的電壓降最小,就要設法降低整個PDS的阻抗或者整個PDS電流路徑的回路電感。

通常,降低整個PDS的阻抗可以分別圍繞PDS的基本組成單元來進行設計。具體分為以下幾個方面:

(1)在進行供電芯片和用電芯片的電源引腳及地引腳的封裝設計時,盡量使由電源引腳和地引腳組成的回路電感最小。由于電源引腳和地引腳上通過的電流大小相等、方向相反,因此要減小回路電感,通常要使電源引腳和地引腳的局部自感盡量小,而電源引腳和地引腳之間的局部互感要盡量大。通常采用扁平導體帶而非圓柱形金屬作為封裝引腳可以降低引腳的局部自感,降低電源引腳和地引腳之間的間距可以增大兩者之間的局部互感。

(2)關于去耦電容的設計,通常有兩條設計原則:低頻時,添加阻抗值較低的去耦電容;高頻時,使去耦電容與供電芯片和用電芯片焊盤之間的回路電感最小,以保證它們之間的阻抗低于一定值。

這里需要說明的是,位于供電芯片一側的去耦電容的作用主要是為供電芯片輸出的交流電流提供交流通路,從而避免電源電壓的波動,這個電容典型值是10uF。

位于用電芯片一側的去耦電容作用又因芯片種類不同而不同,用在模擬芯片一側的去耦電容通常用于旁路電源上的高頻信號,如果不加去耦電容,這些高頻信號可能通過電源引腳進入敏感的模擬芯片。對于控制器和處理器這樣的數字器件,同樣需要去耦電容,但原因不同。這些電容的一個功能是用作“微型”電荷庫。在數字電路中由于執行門電路狀態的切換通常需要很大的電流,因而有額外的備用電荷是有利的。如果執行開關動作時沒有足夠的電荷,會使電源電壓發生很大的變化。電源電壓變化太大,會導致數字信號電平進入不確定狀態,并很可能引起數字器件中的狀態機錯誤運行。

(3)關于供電芯片和用電芯片之間互連線的設計,總的原則是使電源路徑和信號路徑的回路電感最小。詳細情況關注筆者公眾號,后續文章會進行詳細分析。

總之,在以上三個方面設計中,電路和PCB設計人員可以進行自主設計的只有后兩個方面,供電芯片和用電芯片的選擇更多的是出于功能性考慮,兼有一部分性能考慮,如信號完整性,電磁兼容性等。

-

電源

+關注

關注

185文章

18308瀏覽量

255340 -

芯片

+關注

關注

459文章

52282瀏覽量

437492 -

信號完整性

+關注

關注

68文章

1438瀏覽量

96515 -

信號路徑

+關注

關注

0文章

16瀏覽量

8734

發布評論請先 登錄

基于信號完整性的電源分配系統設計

基于信號完整性的電源分配系統設計

評論